Determinisme van de opstartfase:PLL-synthesizer en kalibratie op systeemniveau

In het eerste deel van deze serie artikelen hebben we onderzocht hoe we bekende (deterministische) fasen kunnen bereiken voor alle kanalen binnen chips die zijn geïntegreerd met meerdere digitale signaalverwerkingsblokken (DSP), breedband digitaal-naar-analoogomzetters (DAC's) en breedbandanaloog. -naar-digitaal converters (ADC's). We zijn begonnen met een systeemblokdiagram op hoog niveau dat gebruikmaakt van een subarray-klokboomstructuur en we hebben een multichip-synchronisatiemethode beschreven. In dit tweede deel onderzoeken we faseaanpassingen van de PLL-synthesizer, schaalbaarheid naar meerdere subarrays en kalibratie-algoritmen op systeemniveau.

PLL-synthesizer-fase-aanpassingen

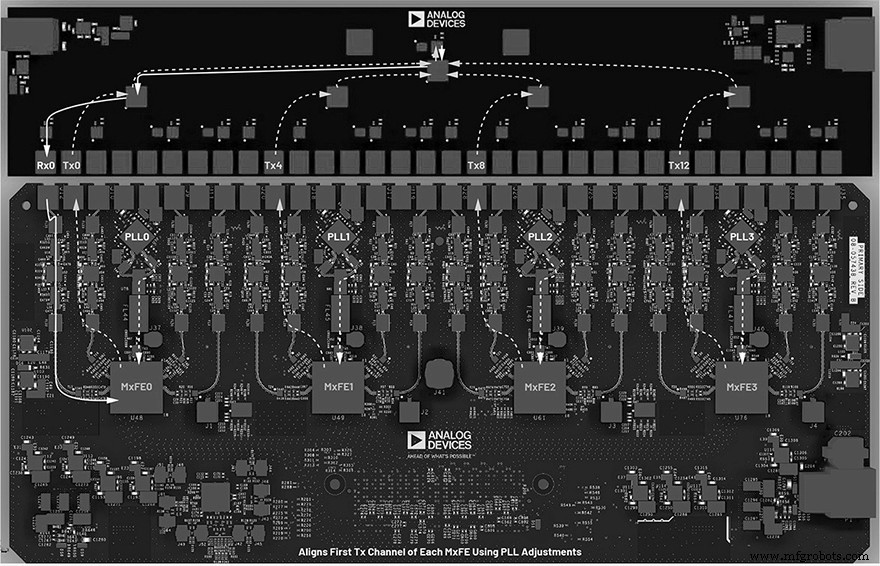

De gekozen PLL-synthesizer-IC's zijn geselecteerd om relatieve bemonsteringsklokfase-aanpassingen mogelijk te maken die in elk digitizer-IC worden geïnjecteerd. Thermische drift, en de resulterende PLL-fasedrift tussen de sampleklok en de SYSREF van elke IC, wordt gecompenseerd door een feedbackmechanisme te creëren dat ervoor zorgt dat het eerste zendkanaal van elke digitizer-IC in fase wordt uitgelijnd met het eerste zendkanaal van de eerste digitizer-IC. Om deze feedbacklus te bereiken, voert het eerste zendkanaal van elke IC een signaal uit dat zich onderscheidt van de andere zendkanalen, zoals weergegeven in figuur 1. Deze vier signalen worden gecombineerd en verzonden naar een gemeenschappelijke ontvanger, die voor dit systeem Rx0 heet. .

klik voor afbeelding op volledige grootte

Figuur 1. Met een PLL-synthesizer-fase-aanpassingsfunctie kan het eerste zendkanaal van elk digitizer-IC worden uitgelijnd over de subarray. (Bron:Analoge apparaten)

Gelijktijdige ontvangstgegevens worden verkregen voor alle ontvangstkanalen, waardoor gebruikers kruiscorrelatietechnieken kunnen toepassen en de complexe faseverschuivingen tussen deze vier zendkanalen kunnen bepalen, ΦTxOffset . De PLL-synthesizer-IC's bevatten een spanningsgestuurde oscillator (VCO) die werkt op een frequentie ƒ VCO_PLL .

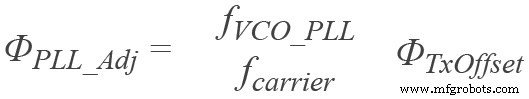

De gemeten faseverschuivingen ΦTxOffset zijn dan gerelateerd aan de vereiste PLL-faseaanpassing ΦPLL_Adj en de RF-frequentie ƒ vervoerder zodanig dat:

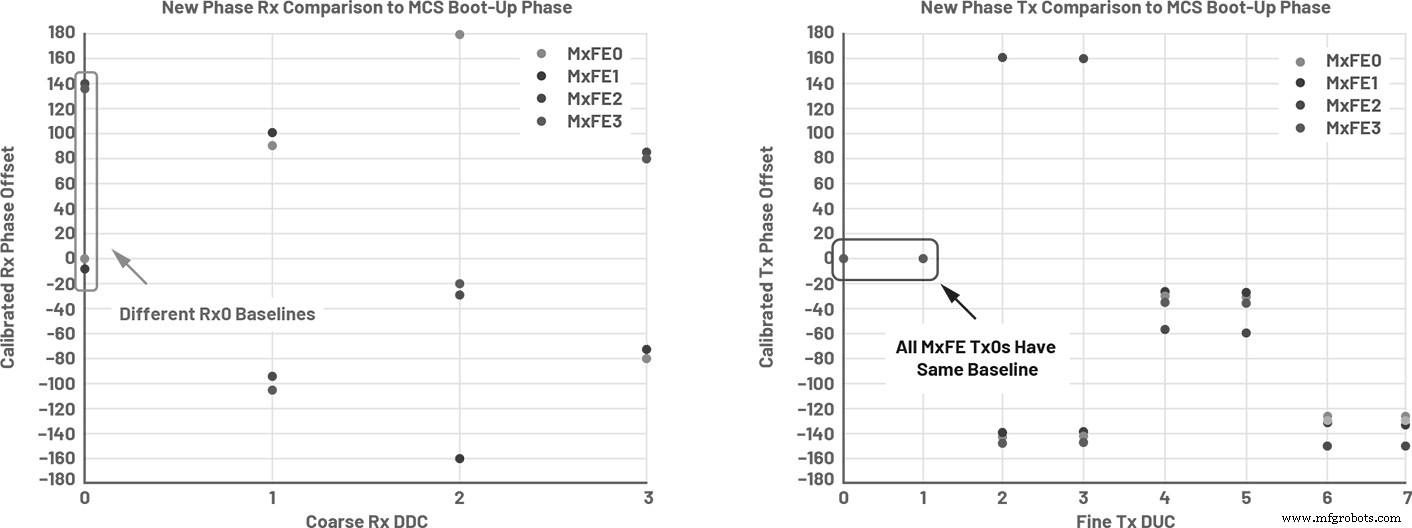

Met behulp van deze formule kunnen de PLL-synthesizerfasen worden aangepast met een nieuwe bekende hoeveelheid om een gemeenschappelijke zendbasislijn tot stand te brengen tussen alle digitizer-IC's voor alle vermogenscycli, zoals weergegeven in afbeelding 2. De open cirkels voor elk kanaal weergegeven in afbeelding 2 komen overeen met de eerste stroomcyclus, terwijl alle andere vaste punten overeenkomen met daaropvolgende stroomcycli. Zoals te zien is in deze figuur, zijn de gekalibreerde zendfase-offsets voor de eerste (en tweede) channelizers van alle digitizer-IC's in fase uitgelijnd. De tweede kanalizer van elk digitizer-IC is in dit geval ook uitgelijnd, omdat er twee kanalizers worden gebruikt voor elke DAC in het systeem.

Door deze faseaanpassingsstap van de PLL-synthesizer toe te voegen voorafgaand aan de MCS-routines die in de eerdere sectie zijn besproken, wordt daardoor een deterministische fase gecreëerd over alle geïnduceerde thermische gradiënten in het systeem door het systeem te dwingen tot dezelfde sampleklok-SYSREF-faserelatie, die zich manifesteert als een zend uitlijningsbasislijn over alle digitizer-IC's.

klik voor afbeelding op volledige grootte

Figuur 2. Door de PLL-fase aan te passen, kan de gebruiker het eerste zendkanaal van alle digitizer-IC's uitlijnen. (Bron:Analoge apparaten)

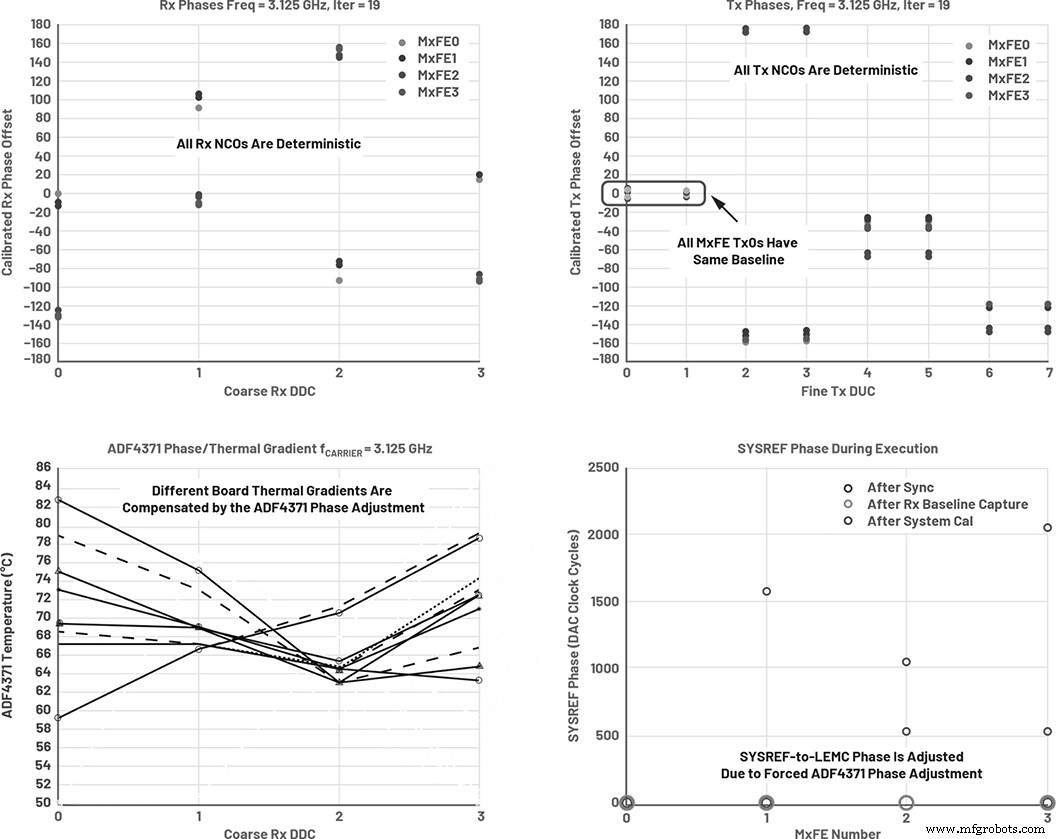

Figuur 3 laat zien dat een geïnduceerde thermische gradiënt kan worden gedetecteerd via de temperatuurmeeteenheid (TMU) op elke PLL-synthesizerchip. Zoals te zien is aan het blauwe spoor linksonder in figuur 3, zijn met opzet sterk variërende temperaturen over het platform geïnduceerd door verschillende ventilatorluchtstromen naar het systeem toe te passen. Het gebruik van de PLL-faseaanpassing voor elke IC toont echter aan dat, ongeacht de luchtstroom die op het bord wordt toegepast, de gekalibreerde NCO-faseverschuivingen voor elk ontvangst- en zendkanaal deterministisch zijn wanneer de eerste zendkanalizer van elke digitizer-IC wordt uitgelijnd op elk ander. Dit wordt onthuld door de strakke cluster van dezelfde kleur stippen op de bovenste twee percelen in figuur 3 te observeren, ondanks de verschillende thermische gradiënten die op het bord worden toegepast tijdens verschillende stroomcycli.

klik voor afbeelding op volledige grootte

Afbeelding 3. De MCS-functie die wordt gebruikt in combinatie met de PLL-fase-aanpassingsfunctie toont determinisme van de opstartfase voor alle ontvangst- en zendkanalen, ongeacht de thermische gradiënt die op het platform wordt geïnduceerd. (Bron:Analoge apparaten)

Rechtsonder in figuur 3 worden de IC-registers van de polled digitizer weergegeven, die de gemeten SYSREF-LEMC-faserelatie tonen na het toepassen van de PLL-synthesizer-fase-offset. Merk op aan de hand van de oranje sporen op de grafiek linksonder dat de PLL-synthesizerfase-aanpassingen alle gemeten niet-nul SYSREF-fasen die het gevolg zijn van een andere geïnduceerde thermische gradiënt volledig compenseren.

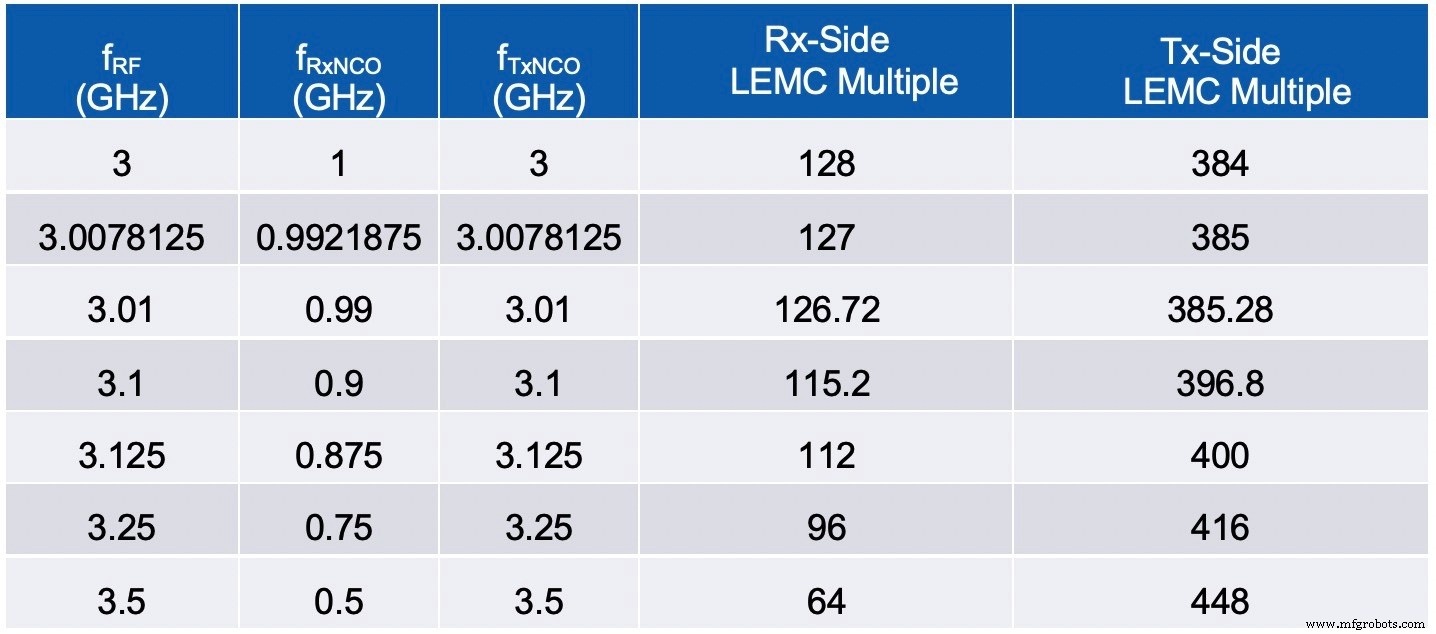

Er zijn veel frequenties gemeten, die allemaal een deterministische ontvangst- en zendfase vertonen. De specifieke frequenties die voor dit artikel zijn gekozen, worden weergegeven in figuur 4 en zijn zodanig gekozen dat MCS wordt aangetoond over veel geïnduceerde thermische gradiënten bij gebruik van niet-gehele veelvouden van de referentieklok of de LEMC.

Figuur 4. De RF-frequenties die in dit artikel worden gebruikt, zijn gekozen om MCS-functies te demonstreren over een breed scala aan klokbronnen, inclusief niet-gehele veelvouden van de referentieklok en LEMC. (Bron:Analoge apparaten)

Schaalbaarheid naar meerdere subarrays

De gegevens in dit artikel zijn voornamelijk gericht op MCS-prestaties op subarrayniveau, maar er moet ook voor worden gezorgd dat deze synchronisatiefuncties realiseerbaar zijn op het grotere arrayniveau en over meerdere subarrays. Om dit hogere synchronisatieniveau te bereiken, is een klokstructuur op array-niveau vereist om ervoor te zorgen dat de SYSREF-verzoeken aan elke subarray die wordt getoond in figuur 1 in deel 1 synchroon aankomen bij de klokbuffer-IC van elke subarray. Gegeven dit criterium kan elke subarray vervolgens de vereiste SYSREF's en BBP-klokken afgeven, zoals eerder beschreven, zodat deze signalen binnen dezelfde bemonsteringsklokcyclus over de grotere array aankomen bij de subarray-digitizer-IC's en BBP. Deze klokboom op array-niveau vereist dat de klokdistributie naar elke subarray de vertragingsaanpassingsblokken bezit die nodig zijn om synchrone SYSREF-verzoekdistributie naar elk van de stroomafwaartse subarray-klokchip-IC's te bereiken. Op deze manier worden uiteindelijk meerdere BBP's die zijn aangesloten op meerdere subarrays gesynchroniseerd.

Kalibratie-algoritme op systeemniveau

Hoewel de MCS-algoritmen die in de vorige secties zijn getoond, een deterministische opstartfase bieden voor elk ontvangst- en zendkanaal, zijn deze fasen niet noodzakelijkerwijs in fase uitgelijnd over alle kanalen binnen het RF-domein vanwege eventuele verschillen in RF-front-end-tracelengtes over kanalen. . Daarom, hoewel de MCS-algoritmen het array-kalibratieproces inderdaad vereenvoudigen, is er nog steeds behoefte aan een kalibratieroutine op systeemniveau om de fasen van elk RF-kanaal binnen het systeem uit te lijnen.

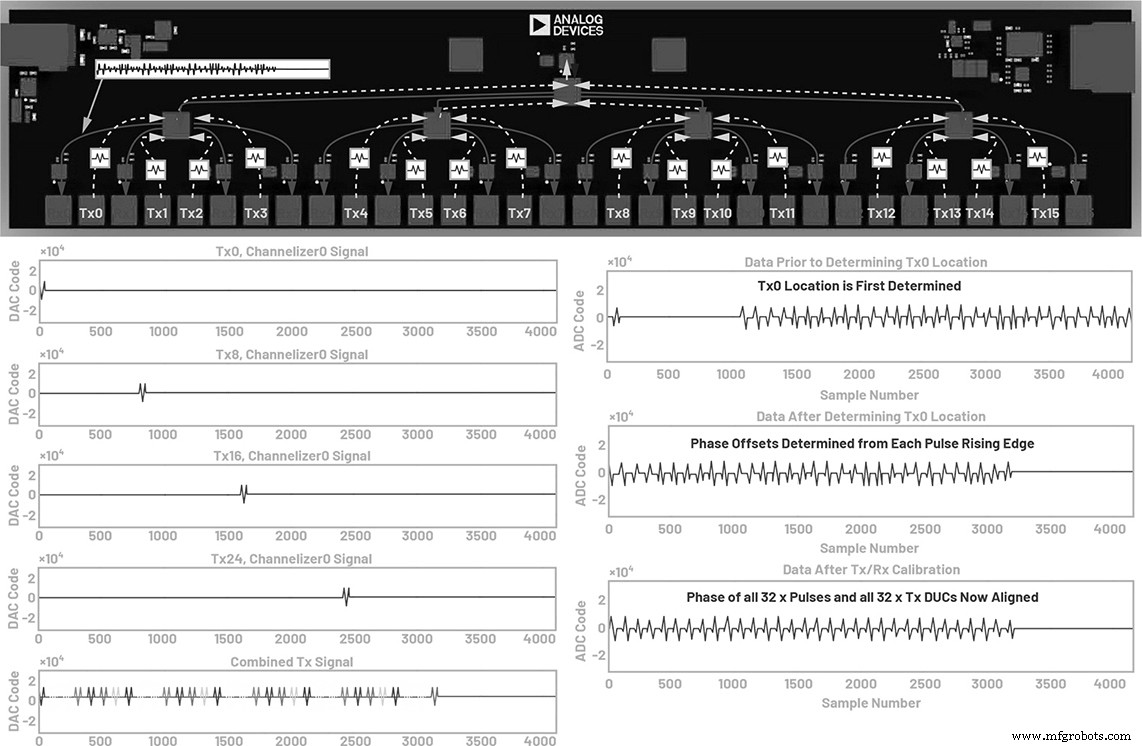

Het is daarom noodzakelijk om naast het uitvoeren van de MCS-algoritmen een efficiënt kalibratiealgoritme op systeemniveau te ontwikkelen. De kalibratiemethode op systeemniveau voor dit artikel maakt gebruik van een specifieke basisbandgolfvorm en is volledig autonoom zonder dat er externe apparatuur nodig is. Het systeem dat in dit artikel wordt beschreven, kan afzonderlijke basisbandgolfvormen in elke channelizer op het platform injecteren. Gebruikmakend van deze mogelijkheid, wordt een basisbandgolfvorm bestaande uit een puls van één periode voor elke zend-channelizer geïnjecteerd in de subarray, zoals weergegeven in de linkerbenedenhoek van figuur 5. Elke zend-channelizer voert daarom slechts één puls uit. De golfvormen zijn echter gespreid over alle zenderkanalizers, zodat er slechts één puls van één periode tegelijk door het systeem wordt afgegeven. De output van alle zendchannelizers wordt gecombineerd binnen het RF-domein en vervolgens gesplitst en teruggestuurd naar alle ontvangstkanalen, zoals weergegeven in de bovenkant van figuur 5. Ten slotte wordt een gelijktijdige ontvangstgegevensregistratie uitgevoerd voor alle ontvangstkanalen en worden de gegevens opgeslagen naar een 4096×16 matrix, waarbij 4096 de steekproefomvang is die is verzameld voor alle 16 ontvangstkanalen.

klik voor afbeelding op volledige grootte

Figuur 5. Een kalibratiealgoritme op systeemniveau wordt gebruikt in combinatie met MCS om snel alle ontvangst- en zendkanalen in het systeem op één lijn te brengen. (Bron:Analoge apparaten)

Deze gegevens worden vervolgens verticaal geanalyseerd langs de eerste kolom (overeenkomend met Rx0) om de Tx0-kanalizerpuls te lokaliseren, zoals wordt weergegeven in de bovenste subplot rechtsonder in figuur 5. Nadat de Tx0-puls is geïdentificeerd, zijn alle andere pulslocaties bekend en de complexe fase van de stijgende flank van elke puls wordt berekend en opgeslagen in een 1×16 vector die overeenkomt met de gemeten faseverschuivingen die aanwezig zijn op alle zendkanalen in het systeem. Met deze kennis en met Tx0 als basisreferentie, worden de complexe fasen van alle zendkanalen vervolgens aangepast op basis van de gemeten offsets.

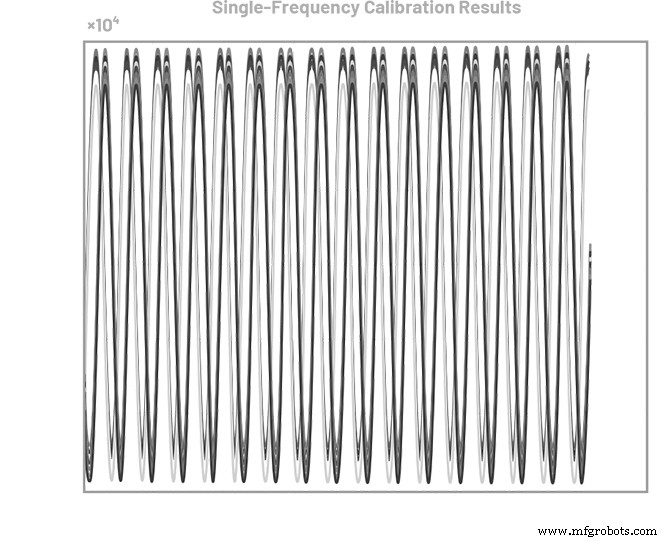

Evenzo, aangezien hetzelfde gecombineerde signaal naar alle ontvangstkanalen wordt verzonden, worden de gegevens vervolgens horizontaal langs de matrix geanalyseerd (kijkend over alle ontvangstkanalen). De complexe fasen van alle ontvangstkanalen worden vervolgens gemeten met betrekking tot Rx0 en opgeslagen in een 1×16 vector die overeenkomt met de gemeten ontvangstfaseverschuivingen die in het systeem aanwezig zijn. De ontvangst-NCO-complexfasen worden vervolgens door de hele subarray aangepast om alle kanalen in fase uit te lijnen met betrekking tot Rx0, zoals wordt getoond door de in-fase (I) en kwadratuurfase (Q) ADC-codes voor alle 16 ontvangstkanalen in figuur 6. Het kan worden opgemerkt dat, hoewel de plot in de fase van figuur 6 alle kanalen uitlijnt, deze niet noodzakelijk alle kanalen in amplitude uitlijnt. Met behulp van de on-chip finite impulse response (FIR) filters die nu aanwezig zijn op deze digitizer-IC's, zou men als alternatief amplitude- en fase-uitlijning over kanalen kunnen bereiken zonder de noodzaak om energieverslindende FPGA-bronnen toe te wijzen om hetzelfde resultaat te bereiken.

klik voor afbeelding op volledige grootte

Figuur 6. 16-kanaals ontvangst I&Q fase-uitlijning wordt bereikt met behulp van MCS en een op zichzelf staand kalibratie-algoritme op systeemniveau. (Bron:Analoge apparaten)

Dit kalibratiealgoritme op systeemniveau wordt momenteel bereikt in MATLAB ® en duurt ongeveer drie seconden om te voltooien. Indien geïmplementeerd in hardwarebeschrijvingstaal (HDL), kan deze kalibratietijd echter verder worden verkort terwijl een volledig op zichzelf staand algoritme behouden blijft. Bovendien kunnen gebruikers, door te vertrouwen op de MCS-algoritmen, als de systeemfrequentie en -amplitude bekend zijn bij het opstarten, fase-offsetwaarden laden uit een opzoektabel in plaats van de metingen te hoeven ondergaan die worden beschreven in deze kalibratiemethode op systeemniveau. In dit geval kan de kalibratiemethode op systeemniveau worden gebruikt om de fase-offsets te vullen die tijdens een fabriekskalibratie in een opzoektabel zijn opgeslagen.

Conclusie

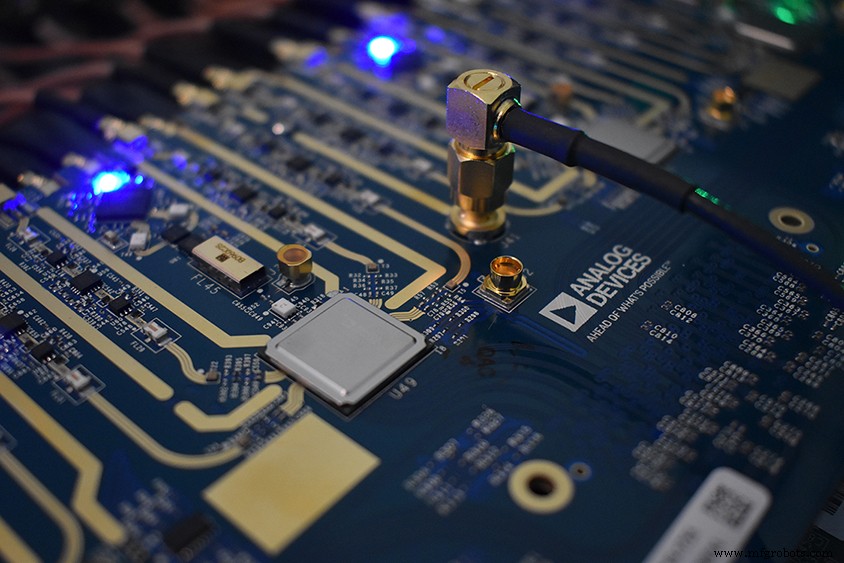

Een succesvol MCS-proces is aangetoond met behulp van vier AD9081 MxFETM IC's van Analog Devices als de ruggengraat van de subarray. Thermische gradiënten over het platform worden gecompenseerd met behulp van fase-aanpassingsblokken in vier ADF4371 PLL-synthesizers. Een HMC7043 klok-IC wordt gebruikt om de SYSREF's en BBP-klokken te distribueren die nodig zijn voor de JESD204C-interface. MCS-algoritmen binnen de AD9081 maken vereenvoudigde kalibraties op systeemniveau mogelijk en bieden deterministische opstartfase voor meerdere frequenties en thermische gradiënten die in het systeem aanwezig zijn. Er wordt ook een efficiënt kalibratie-algoritme op systeemniveau gepresenteerd dat wordt gebruikt om LUT's te vullen tijdens fabriekskalibratie, en daardoor de opstarttijd van het systeem aanzienlijk verkort. Dit platform wordt getoond in figuur 7 en wordt de Quad-MxFE genoemd. Het systeem is te koop bij Analog Devices. Dit werk is relevant voor elk meerkanaals systeem dat aanwezig is in elk phased array radar, elektronische oorlogsvoering, instrumentatie of 5G-platform.

Figuur 7. Het Quad-MxFE-platform is te koop bij Analog Devices. (Bron:Analoge apparaten)

Referenties

1 Del Jones. "JESD204C Primer:wat is nieuw en zit erin voor u - deel 1." Analoge dialoog , vol. 53, nr. 2, juni 2019.

2 Del Jones. "JESD204C Primer:wat is nieuw en zit erin voor u - deel 2." Analoge dialoog , vol. 53, nr. 3, juli 2019.

Ingebed

- 3 redenen waarom DevOps en Cloud elkaar nodig hebben; DevCloudOps

- Vectors en AC-golfvormen

- Frequentie- en fasemeting

- Wat is sensorkalibratie-definitie en zijn toepassing

- Structuren en klassen in C++

- Mailboxen:introductie en basisservices

- Semaphores:introductie en basisdiensten

- Wachtrijen:introductie en basisservices

- Meeslepende video, AI en de volgende fase in de detailhandel

- Hard draaien en cilindrisch slijpen zijn voor elkaar gemaakt

- Veelvoorkomende soorten freesmachines en wanneer ze elk moeten worden gebruikt