Determinisme van de opstartfase:multichipsynchronisatie gebruiken

De integratie van meerdere DSP-blokken (digital signal processing), breedband digitaal-naar-analoog-omzetters (DAC's) en breedband-analoog-naar-digitaal-omzetters (ADC's) in een enkele monolithische chip maakt het nu mogelijk om energieverslindende FPGA-bronnen te ontlasten aan zorgen voor een kleinere voetafdruk, een lager vermogen en een groter aantal kanalen, die met hogere snelheden kunnen samplen dan voorheen haalbaar was. Samen met deze nieuwe mogelijkheid komen nieuwe multichip-synchronisatie (MCS)-algoritmen binnen deze geïntegreerde circuits (IC's), waarmee gebruikers een bekende (deterministische) fase voor alle kanalen kunnen bereiken bij het voeden van het systeem of het anderszins aanbrengen van softwarewijzigingen aan het systeem. Deze deterministische fase vereenvoudigt daarom de bredere kalibratie-algoritmen op systeemniveau die nodig zijn om de synchronisatie van alle kanalen aan de uitgang of ingang naar de front-end-netwerken die aan deze IC's zijn gekoppeld, te bereiken. Dit artikel presenteert experimentele resultaten die deze MCS-mogelijkheid demonstreren bij gebruik van een 16-kanaals ontvanger/zenderplatform dat bestaat uit meerdere digitizer-IC's, klokbronnen en digitale interfaces.

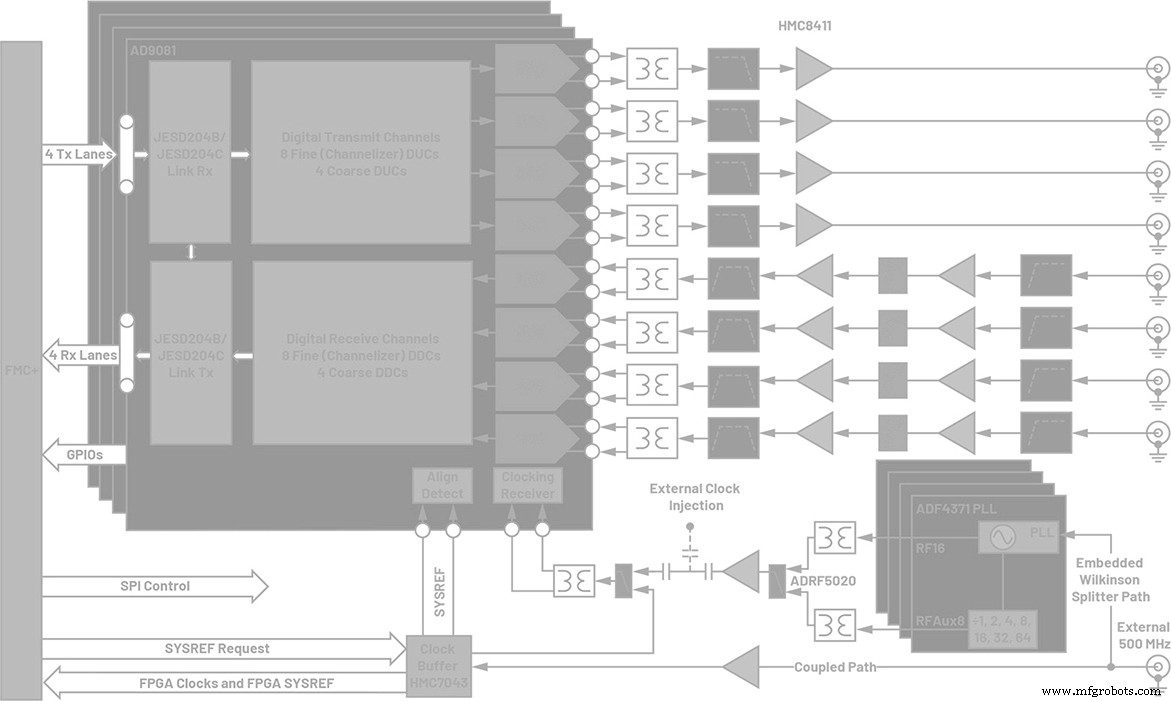

Systeemblokdiagram op hoog niveau

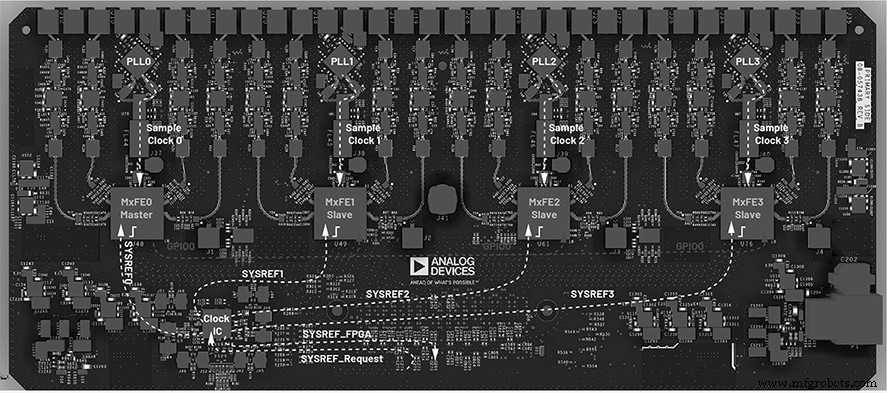

Een blokschema van het systeem dat voor deze test wordt gebruikt, wordt getoond in afbeelding 1 en bestaat uit vier geïntegreerde DAC/ADC/DSP IC's die elk bestaan uit vier 12 GSPS DAC's, vier 4 GSPS ADC's en 12 digitale upconverter (DUC) en 12 digitale downconverter (DDC) blokken.

klik voor afbeelding op volledige grootte

Figuur 1. Een blokschema op hoog niveau van het systeem dat wordt gebruikt om MCS en meerkanaals kalibratie-algoritmen te demonstreren. (Bron:Analoge apparaten)

De DUC's/DDC's maken frequentievertaling en/of interpolatie/decimering binnen het digitale domein mogelijk. Met behulp van een enkele 500 MHz-referentieklok die op het bord wordt geïnjecteerd, wordt vervolgens een referentie-vergrendelde klokbuffer gebruikt om de systeemreferentiesignalen te genereren die nodig zijn voor MCS, evenals de klokken die nodig zijn voor de digitale interface naar de basisbandprocessor (BBP). Het systeem bevat ook vier afzonderlijke PLL-synthesizers (phase-locked loop) die de 12 GHz-bronnen genereren die nodig zijn om elk digitaliserend IC te klokken vanuit de gemeenschappelijke referentie. Een RF-frontend is bevestigd aan elke digitizer-uitgang/-ingang, die een gefilterd en versterkt signaal creëert van/naar de edge-gelanceerde RF-connectoren. Er wordt een volledige stroomverdelingsoplossing geïmplementeerd. Alle spanningen die nodig zijn voor het systeem worden gegenereerd uit een enkele 12 V-bron. Alle zendsignalen planten zich voort aan de onderkant van het bord, terwijl alle ontvangstsignalen zich aan de bovenkant van het bord voortplanten om de meest optimale kanaal-naar-kanaal isolatie te bereiken.

Subarray klok boomstructuur

Zoals eerder vermeld, bestaat de subarray-klokboom uit een enkele 500 MHz-referentiebron die wordt gesplitst en verzonden naar de referentie-ingangen van vier afzonderlijke PLL-synthesizer-IC's, zoals hierboven weergegeven in figuur 1. Dit 500 MHz-signaal is ook 10 dB gekoppeld, versterkt , en verzonden naar een ander klokbuffer-IC dat verantwoordelijk is voor het genereren van de systeemreferenties (SYSREF's) en BBP-klokken die nodig zijn voor de digitale interface. Het doel van deze klokkenboom is drieledig, namelijk:

- Maakt SYSREF-vertragingen voor afzonderlijke kanalen mogelijk om eventuele mismatches in de trace-lengte tussen IC's te corrigeren.

- Maakt individuele PLL/synthesizer-faseaanpassing mogelijk en zorgt daardoor voor synchronisatie over de respectieve digitizer-IC-klokbronnen, om eventuele geïnduceerde thermische gradiënten binnen het systeem te compenseren.

- Hiermee kan de gebruiker voldoen aan de noodzakelijke setup-and-hold-vereisten voor de digitaliserende IC's.

De klokboom-IC's zijn gekozen om aan te tonen dat verschillende anomalieën van de kaartlay-out in software en/of hardware kunnen worden gecorrigeerd met behulp van digitale en analoge vertragingsblokken die in deze chips aanwezig zijn. Uiteindelijk is het resultaat een klokboom die een SYSREF-puls kan leveren aan alle vereiste IC's binnen dezelfde sampleklokcyclus van elk van deze IC's.

Digitale interface met basisbandprocessor

De vier digitaliserende IC's brengen elk een JESD204B of JESD204C digitale verbindingsinterface tot stand met de BBP. 1,2 Deze interface is verantwoordelijk voor het verzenden van de ADC- en DAC-codes over de fysieke sporen (SERDES) van en naar de BBP. Het aantal differentiële SERDES-sporen dat in deze interface wordt gebruikt, wordt het aantal rijstroken (L) voor deze link genoemd. De converterbitresolutie die via de link wordt verzonden, wordt beschouwd als N'. Het aantal gekanaliseerde datapaden, ook wel virtuele converters genoemd, wordt aangeduid als M. De resultaten in dit artikel gebruiken een JESD204C-link met M =16, N' =16, L =4 voor de DAC-side links en M =8 , N' =16, L =2 voor de ADC-zijlinks.

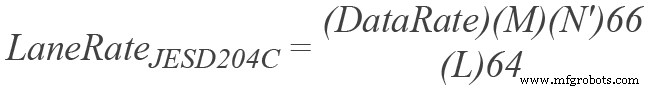

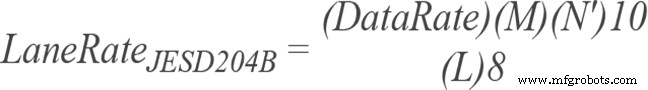

De snelheid waarmee gegevens worden verzonden en ontvangen tussen de digitizer-IC en de BBP wordt de rijstrooksnelheid genoemd. De DSP-blokken op silicium (dat wil zeggen de DDC's/DUC's) stellen de gebruiker in staat om de digitizers te samplen met een andere snelheid dan de gegevenssnelheid die over de fysieke rijstroken wordt verzonden. Als zodanig is de rijstrooksnelheid afhankelijk van de digitaal gedecimeerde/geïnterpoleerde datasnelheid voor elk datapad. Voor dit werk is een 250 MSPS I/Q-gegevenssnelheid gebruikt. Voor een JESD204C-interface is de rijstrooksnelheid gedefinieerd als:

terwijl voor een JESD204B-interface de rijstrooksnelheid is gedefinieerd als:

De resultaten die in dit artikel worden getoond, gebruiken een rijstrooksnelheid van 16,5 Gbps voor zowel de ADC- als de DAC-zijde JESD204C-links.

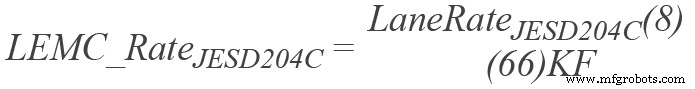

Elke JESD204B/JESD204C-link kan tot stand worden gebracht binnen verschillende subklassen. Deze subklassen worden gescheiden op basis van de vraag of multichipsynchronisatie of deterministische latentie vereist is. Voor dit werk gebruiken de getoonde gegevens een JESD204C Subklasse 1-modus en gebruiken daarom SYSREF-signalen om delen van de digitale gegevens die worden verzonden over de meerdere links in het systeem uit te lijnen. In deze JESD204C Subklasse 1-modus worden de SYSREF-signalen gebruikt om de lokale uitgebreide multiblokteller (LEMC) uit te lijnen, die zendt met een snelheid:

waarbij F het aantal octetten per JESD-frame per baan is en K het aantal frames per enkel multiframe is. Voor dit werk is F =8 en K =32, en daarom wordt een LEMC-snelheid van 7,8125 MSPS gebruikt. Kennis van deze LEMC-frequentie is belangrijk, aangezien elke succesvolle MCS-routine moet aantonen dat RF-frequenties die geen geheel veelvoud van de LEMC-frequentie zijn, in staat zijn om een deterministische opstartfase te bereiken.

Multichip-synchronisatiemethode

Binnen dit systeem bieden de breedband geïntegreerde ADC/DAC IC's MCS-schakelingen om deterministische power-up fase op alle zend- en ontvangst RF-kanalen mogelijk te maken, zelfs bij gebruik van de DUC/DDC DSP-blokken binnen de IC. Met deze MCS-functie kunnen gebruikers een opzoektabel (LUT) invullen tijdens een fabriekskalibratie om operationele uitvaltijd te minimaliseren. Elke succesvolle MCS-demonstratie moet in staat zijn om deterministische fase over alle kanalen binnen het systeem te bieden voor elke poging tot RF-frequentie, thermische gradiënt en systeemstroomcyclus.

De geïntegreerde ADC/DAC-IC's bevatten 12 DUC-blokken en 12 DDC-blokken, zoals hierboven weergegeven in afbeelding 1. Elk van deze blokken bevat een subblok voor interpolatie (DUC) of decimering (DDC) om de datasnelheid van het digitale DAC-ingangssignaal of ADC gedigitaliseerd uitgangssignaal, respectievelijk. Elke DUC/DDC bevat ook een complexe numeriek bestuurde oscillator (NCO), die frequentievertaling binnen het digitale domein mogelijk maakt. Elk van deze NCO's is in staat tot realtime complexe faseaanpassing, zodat het digitale signaal tussen de DAC/ADC en de BBP kan worden aangepast om te compenseren voor verschillende SERDES-tracelengte-mismatches.

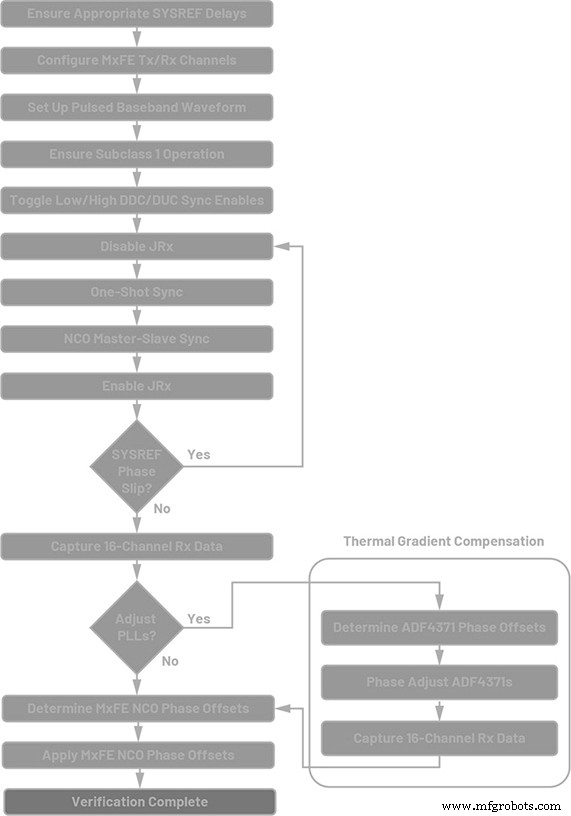

De MCS-functie voor deze ADC/DAC-IC's is verantwoordelijk voor het bereiken van fasedeterminisme in alle aspecten van het datapad van de digitizer-IC. De workflow om MCS te bereiken wordt getoond in figuur 2.

klik voor afbeelding op volledige grootte

Figuur 2. De MCS-workflow omvat afzonderlijke functies die verschillende delen van het datapad op elkaar afstemmen. (Bron:Analoge apparaten)

Het MCS-algoritme kan worden onderverdeeld in twee afzonderlijke functies:

- Eenmalige synchronisatie:deze functie is verantwoordelijk voor het afstemmen van de basisbandgegevens die over de fysieke rijen van alle digitizer-IC's binnen het subarraysysteem worden verzonden.

- NCO master-slave-synchronisatie:deze functie is verantwoordelijk voor het uitlijnen van alle NCO's in alle verschillende digitizer-IC's binnen het subarraysysteem.

De one-shot sync-functie vereist eerst dat de gebruiker de JESD-linkparameters definieert (zoals M, N', L, enz.) en vervolgens de synchronisatielogica configureert voor elke gewenste SYSREF-middeling (bij gebruik van continue SYSREF-pulsen). Bovendien kunnen gewenste LEMC-vertragingen worden gebruikt om te forceren dat de LEMC wordt gegenereerd met een bepaalde vertraging na de SYSREF-edge. Nadat dit is voltooid, schakelt de gebruiker het one-shot sync-bit in elke digitizer-IC in en verzoekt vervolgens dat SYSREF-pulsen binnen dezelfde klokcyclus naar elke IC worden verzonden, zoals weergegeven in afbeelding 3.

klik voor afbeelding op volledige grootte

Figuur 3. Het MCS-algoritme gebruikt SYSREF-signalen om one-shot sync te implementeren en GPIO-signalen om NCO master-slave sync te implementeren om deterministische fase te bereiken. (Bron:Analoge apparaten)

Voor dit systeem zijn analoge fijne vertragingen geïntroduceerd in de klokbuffer-IC om synchrone SYSREF's naar alle digitizer-IC's mogelijk te maken. Een volgende controle kan worden uitgevoerd om te verifiëren dat het eenmalige synchronisatieproces met succes is uitgevoerd door registers binnen elke IC op te vragen die informatie geven over de faserelatie tussen het SYSREF-signaal en de LEMC-grens van de link van elke IC.

Zodra een stabiele fase is gemeten (dat wil zeggen, zodra het SYSREF-LEMC-faseregister 0 aangeeft), weet de gebruiker dat de LEMC's van alle digitizer-IC's zijn uitgelijnd en kan de gebruiker vervolgens doorgaan naar het NCO-master-slave-synchronisatieproces. Voor deze activiteit zijn de subtaken die zijn beschreven voor de one-shot sync opgenomen in een Application Programming Interface (API) die door de chipfabrikant wordt geleverd.

De NCO master-slave-synchronisatiefunctie wijst eerst een van de digitizer-IC's in de subarray toe om als masterchip te fungeren, zoals hierboven weergegeven in afbeelding 3. Alle andere digitizers worden dan als slave-IC's beschouwd. Het master-IC is zo ingesteld dat de GPIO0-pin van dit apparaat wordt geconfigureerd als een uitgang en wordt gerouteerd naar de GPIO0-netten van de drie slave-digitizer-IC's. De slave GPIO0-netten zijn geconfigureerd als ingangen. De gebruiker kan er dan voor kiezen om de SYSREF-puls, de LEMC stijgende flank of de LEMC dalende flank te activeren. Voor de gegevens die in dit artikel worden getoond, wordt de stijgende flank van de LEMC gebruikt als de NCO master-slave sync-triggerbron en worden de GPIO-netten door de BBP geleid in plaats van lokaal op de subarray. Vervolgens worden de DDC-synchronisatiebits laag en vervolgens hoog geschakeld om het NCO-synchronisatiealgoritme aan de ADC-zijde in te schakelen. Evenzo wordt de uitlijnbit van de microprocessor van laag naar hoog geschakeld om het NCO-synchronisatiealgoritme aan de DAC-zijde in te schakelen.

Wanneer deze trigger wordt gevraagd, bevestigt het master-digitizer-IC bij de volgende LEMC-opgaande flank een hoog master-uit-signaal via zijn GPIO0-net. Dit signaal plant zich voort naar de GPIO0-ingangen van elk van de slave-apparaten. Bij de volgende LEMC-edge ervaren alle digitizer-IC's een NCO-resetalgoritme. Hierna worden eventuele LEMC-pulsen genegeerd met betrekking tot het NCO master-slave sync-algoritme. Net als bij de eenmalige synchronisatie, zijn deze NCO master-slave synchronisatie-subtaken opgenomen in API-functies voor gebruikersgemak.

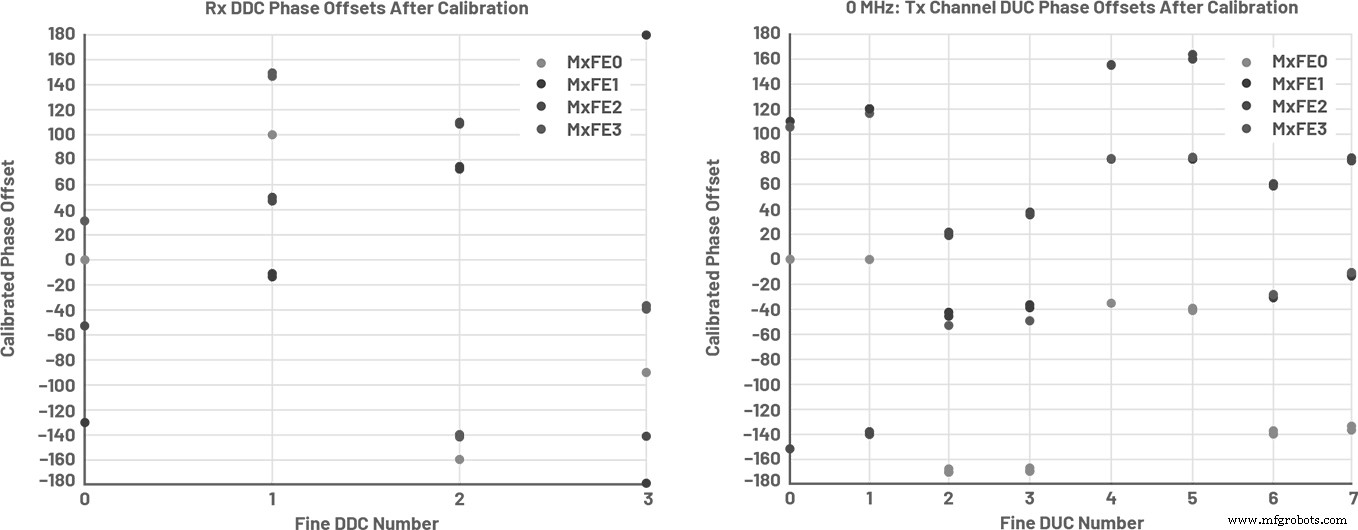

Door zowel de one-shot-synchronisatie als de NCO master-slave-synchronisatiefunctie te gebruiken, worden beide ingangen op elke DDC/DUC uitgelijnd, zodat de uitgangsfase-offset van elk ontvangst- en zendkanaal herhaalbaar is na meerdere stroomcycli, zoals weergegeven in afbeelding 4. De gegevens in figuur 4 worden de gekalibreerde fase-offsets weergegeven over 100 stroomcycli (aangegeven door meerdere ononderbroken stippen) voor elke kanalizer voor ontvangen en verzenden, terwijl het systeem tijdens elke herstart onder een statische thermische gradiënt werkt.

klik voor afbeelding op volledige grootte

Figuur 4. De ontvangst fijne DDC's (links) en de zend fijne DUC's (rechts) zijn correct uitgelijnd bij het uitvoeren van het MCS-algoritme. (Bron:Analoge apparaten)

Zoals te zien is aan de meerdere stippen in deze afbeelding, zijn de stippen van elke kleur voor een bepaalde DDC/DUC allemaal strak geclusterd op dezelfde positie na stroomcycli, waardoor de deterministische fase voor dat specifieke kanaal wordt weergegeven. Voor de gegevens in deze test zijn alle acht channelizer DUC's gebruikt aan de zendzijde, terwijl slechts vier van de acht channelizer DDC's worden gebruikt. Er is echter bevestigd dat inderdaad alle acht channelizer-DDC's een deterministische fase bieden terwijl ze ook het MCS-algoritme gebruiken.

Door dit algoritme bij het opstarten uit te geven, wordt een deterministische fase voor elk kanaal tot stand gebracht als de sampleklokken van de PLL-synthesizer en de klok-IC-SYSREF's dezelfde faserelatie behouden bij het opstarten. Elk systeem zal echter thermische gradiënten ondergaan, wat kan resulteren in PLL-klokdrift, en wat kan resulteren in een andere opstartfase als het niet wordt gecompenseerd. Om de thermische gradiëntdrift binnen het systeem te compenseren, maakt dit platform gebruik van PLL-synthesizerfase-aanpassingen.

In het volgende deel van deze serie artikelen zullen we de fase-aanpassingen van de PLL-synthesizer, schaalbaarheid naar meerdere subarrays en kalibratie-algoritmen op systeemniveau onderzoeken.

Referenties

1 Del Jones. "JESD204C Primer:wat is nieuw en zit erin voor u - deel 1." Analoge dialoog , vol. 53, nr. 2, juni 2019.

2 Del Jones. "JESD204C Primer:wat is nieuw en zit erin voor u - deel 2." Analoge dialoog , vol. 53, nr. 3, juli 2019.

Ingebed

- Faseverschuiving

- AC-fase

- Faserotatie

- Koekoeksklok

- C# met behulp van

- MACOM introduceert nieuwe versterker met ultralage faseruis

- Keysight lanceert nieuw faseruistestsysteem

- Het gebruik van meerdere inferentie-chips vereist een zorgvuldige planning

- Een uiterst nauwkeurige golfvorm genereren met behulp van een DAC en een aangepaste PCB

- Verilog-klokgenerator

- Een frees als draaibank gebruiken