De RISC-V-architectuur uitbreiden met domeinspecifieke accelerators

Toen de RISC-V-markt voor het eerst begon, was de eerste haast om de kosten te verlagen van ontwerpen die anders propriëtaire CPU-instructiesetarchitecturen (ISA's) in diep ingebedde applicaties zouden hebben gebruikt. Toen deze systemen op chips (SoC's) werden gefabriceerd in FinFET-halfgeleiderprocestechnologie, werden de maskerkosten zo duur dat veel eindige-toestandsmachines werden vervangen door programmeerbare microsequencers op basis van de RISC-V-instructieset. Deze zorgden voor de aanvankelijke opwinding en later voor de commoditisering van eenvoudige RISC-V-kernen van 2014 tot 2018.

Naarmate de RISC-V-architectuur volwassener werd en SoC-ontwerpers vertrouwd raakten met de ISA, vond deze toepassing in realtime-applicaties die hoge prestaties vereisten:met name als front-end voor zeer gespecialiseerde acceleratie-engines voor toepassingen zoals kunstmatige intelligentie . Een belangrijke reden voor deze adoptie is dat RISC-V een open architectuur is voor gebruikers om instructies toe te voegen, dus de RISC-V-processors hoefden de versnellers niet te behandelen als geheugen-toegewezen I/O-apparaten, zoals het geval was voor traditionele architecturen. . In plaats daarvan kunnen ze een co-processor met lage latentie gebruiken.

De beschikbaarheid van RISC-V-processors met vectorextensie stelde gespecialiseerde versnellers in staat om de lagen tussen de binnenste lussen van de kernel te verwerken voor toepassingen zoals kunstmatige intelligentie (AI), augmented reality/virtual reality (AR/VR) en computervisie. Maar dit is niet mogelijk zonder speciaal gebouwde uitbreidingen, zoals een aangepaste laadinstructie om gegevens van een externe versneller naar interne vectorregisters te brengen.

De drijvende kracht achter deze verschuiving is het programmeermodel dat door deze toepassingen wordt gevraagd. De accelerator voor speciale doeleinden - die een groot aantal vermenigvuldigers is - is zeer efficiënt, hoewel nogal inflexibel, zowel bij de bewerkingen die het uitvoert als bij het verplaatsen van gegevens. Vergelijk dit met een processor voor algemeen gebruik zoals de x86 die de programmeur de ultieme flexibiliteit geeft om te programmeren zonder rekening te houden met de beperkingen van de rekenmachine - als het ontwerp maar 100 W vermogen heeft om te verbranden, wat de meeste niet hebben.

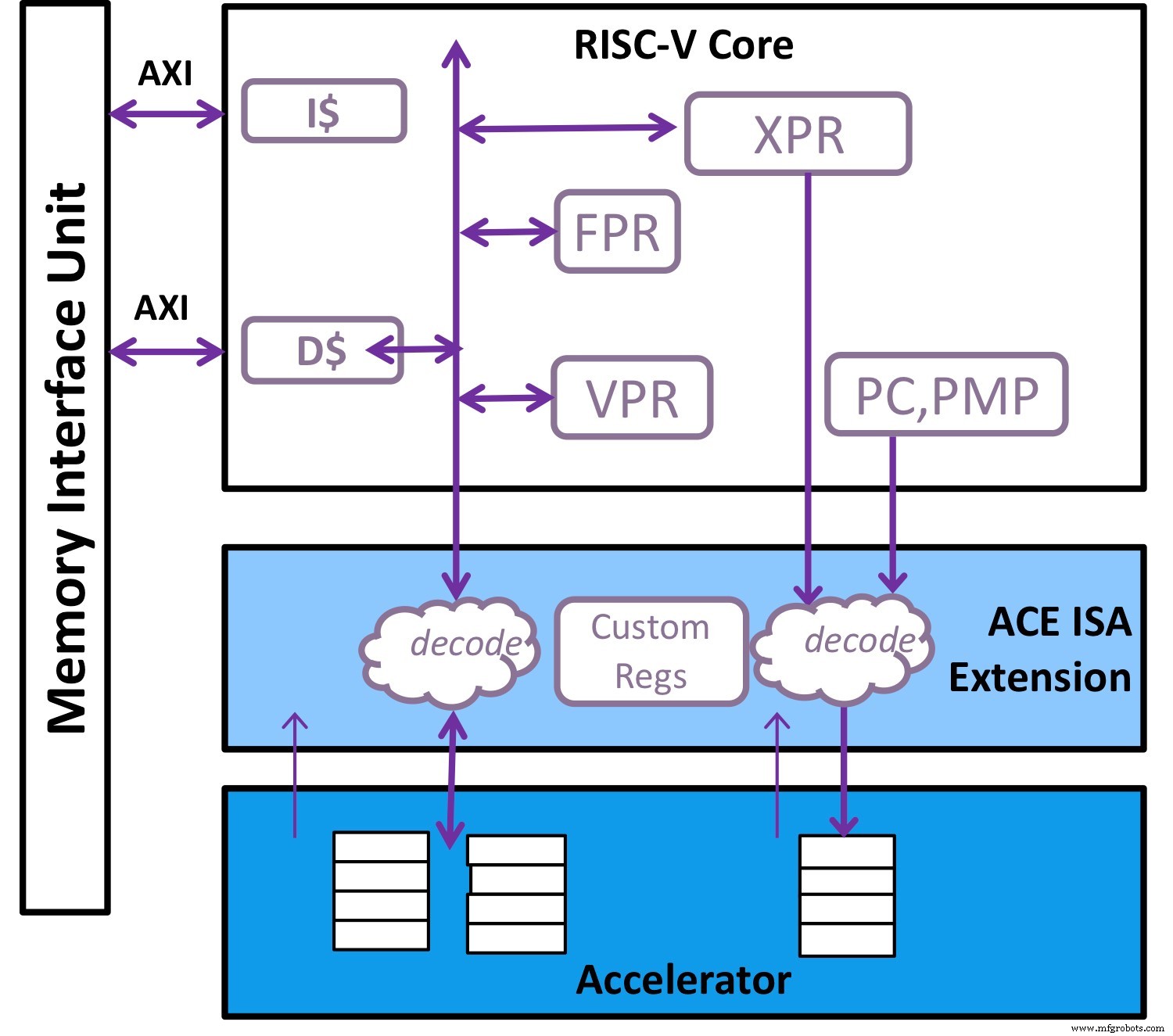

De standaard vectorextensie in RISC-V, aangevuld met gespecialiseerde aangepaste instructies, is een ideale aanvulling op de accelerator (Afbeelding:Andes Technology)

De voor de hand liggende oplossing is om de flexibiliteit van een CPU voor algemeen gebruik te combineren met een versneller die een zeer specifieke taak aankan (zie bovenstaande afbeelding). In RISC-V is de volwassen wordende standaard vectorextensie, aangevuld met gespecialiseerde aangepaste instructies, een ideale aanvulling op de accelerator, en deze acceptatie is de afgelopen 18 maanden duidelijk geworden naarmate oplossingen voor domeinspecifieke versnelling (DSA) convergeren naar RISC-V-platforms.

Om deze visie mogelijk te maken hebben we geconstateerd dat de accelerator in staat moet zijn om zijn eigen commandoset uit te voeren met eigen middelen, waaronder geheugen. Om de uitvoering van het gaspedaal te stroomlijnen, moet de RISC-V ook in staat zijn om de microcode zo breed als nodig te maken en alle vereiste besturingsinformatie in één commando naar het gaspedaal te sturen. Bovendien moet deze accelerator-commandoset op de hoogte zijn van de scalaire registers en vectorregisters van de RISC-V-processor, evenals van zijn eigen bronnen zoals besturingsregisterbestanden en geheugen.

Wanneer de versneller hulp nodig heeft om gegevens op speciale manieren opnieuw te ordenen of te manipuleren, behandelt de Andes-architectuur dit met een vectorverwerkingseenheid (VPU) om het gecompliceerde werk van gegevenspermutaties te verwerken - verschuiven, verzamelen, comprimeren en uitbreiden. Tussen de lagen zijn er enkele kernen die complicaties met zich meebrengen. Hier biedt de VPU de flexibiliteit om in die behoefte te voorzien. In deze sockets voeren zowel de accelerator als de VPU een enorme hoeveelheid parallelle berekeningen uit; daarom hebben we hardware toegevoegd om de bandbreedte van het geheugensubsysteem aanzienlijk te verhogen om aan de rekenvraag te voldoen, inclusief maar niet beperkt tot prefetch en niet-blokkerende transacties met een retour van buiten de orde.

De eerste RISC-V-vectorprocessor van Andes Technology die de nieuwste V-extensie 0.8-versie ondersteunt, de NX27V, voert elke berekening uit in de eenheid van 8-bits, 16-bits en 32-bits gehele getallen tot 16-bits en 32-bits drijvende komma's. Het ondersteunt ook het Bfloat16- en Int4-formaat om de opslag- en overdrachtsbandbreedte voor gewichtswaarden van de machine learning-algoritmen te verminderen. De RISC-V-vectorspecificatie is zeer flexibel waardoor de ontwerpers de belangrijkste ontwerpparameters kunnen configureren, zoals de vectorlengte, het aantal bits in elk vectorregister en de SIMD-breedte, het aantal bits dat elke cyclus door de vectorengine wordt verwerkt.

De NX27V heeft een vectorlengte tot 512 bits en kan worden uitgebreid tot 4096 bits door maximaal acht vectorregisters te combineren. Met toegevoegde meerdere functionele eenheden die in parallelle pijplijnen werken, kan het de rekendoorvoer ondersteunen die nodig is in gediversifieerde toepassingen. In een implementatie die is geconfigureerd met een 512-bit vectorlengte en dezelfde SIMD-breedte, bereikt deze in het slechtste geval een snelheid van 1 GHz in 7 nm binnen een gebied van 0,3 mm 2 . Voor ondersteuning bij softwareontwikkeling helpt Clarity, naast de compiler, de debugger, de vectorbibliotheken en de cyclussimulator, een visualisatietool voor de NX27V-pijplijn, bij het analyseren en optimaliseren van de prestaties van kritieke lussen. Deze oplossing is al beschikbaar in ons programma voor vroege toegang.

In de afgelopen 15 maanden hebben we een grote vraag naar hoge prestaties gezien met de toevoeging van een krachtige RISC-V-vectorextensie, die deze combineert met een geheugensubsysteem met hoge bandbreedte en de accelerator dichter bij de CPU brengt. Dit is het type computervereiste waarvan we denken dat het de vraag naar RISC-V en vectorverwerking zal stimuleren.

>> Dit artikel is oorspronkelijk gepubliceerd op onze zustersite, EE Times.

Ingebed

- Introductie van de IIC, nu met OpenFog!

- 2e versie van de industriële internetreferentiearchitectuur is uit met gelaagde databus

- Bestrijding van bosbranden met het IoT

- Het onbereikbare bereiken met satelliet-IoT

- Een gids voor het versnellen van applicaties met precies de juiste RISC-V aangepaste instructies

- De toekomst bouwen met robotica

- De zekering 1 afdrukken met de zekering 1

- Wat moet ik doen met de gegevens?!

- Edge computing:de architectuur van de toekomst

- De IoT-bedreigingsvector beveiligen

- Op pad met IoT