Een Case-When-statement gebruiken in VHDL

De Case-When-instructie zorgt ervoor dat het programma één van meerdere verschillende paden neemt, afhankelijk van de waarde van een signaal, variabele of uitdrukking. Het is een eleganter alternatief voor een If-Then-Elsif-Else-statement met meerdere Elsif's.

Andere programmeertalen hebben vergelijkbare constructies, waarbij trefwoorden worden gebruikt zoals een switch , case , of selecteer . Case-When-statements worden onder andere vaak gebruikt voor het implementeren van multiplexers in VHDL. Lees verder of bekijk de video om erachter te komen hoe!

Deze blogpost maakt deel uit van de serie Basic VHDL Tutorials.

De basissyntaxis voor de Case-When-instructie is:case <expression> is

when <choice> =>

code for this branch

when <choice> =>

code for this branch

...

end case;

De <expression> is meestal een variabele of een signaal. De Case-instructie kan meerdere when . bevatten keuzes, maar er wordt slechts één keuze geselecteerd.

De <choice> kan een unieke waarde zijn zoals "11" :when "11" =>

Of het kan een bereik zijn zoals 5 to 10 :when 5 to 10 =>

Het kan verschillende waarden bevatten, zoals 1|3|5 :when 1|3|5 =>

En het belangrijkste, de others keuze. Het wordt geselecteerd wanneer er geen andere keuze werd gevonden:when others =>

De others keuze is gelijk aan de Else vertakking in de If-Then-Elsif-Else-instructie.

Oefening

In deze video-tutorial leren we hoe we een multiplexer kunnen maken met behulp van het Case-When-statement in VHDL:

De laatste code die we in deze tutorial hebben gemaakt:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T14_CaseWhenTb is

end entity;

architecture sim of T14_CaseWhenTb is

signal Sig1 : unsigned(7 downto 0) := x"AA";

signal Sig2 : unsigned(7 downto 0) := x"BB";

signal Sig3 : unsigned(7 downto 0) := x"CC";

signal Sig4 : unsigned(7 downto 0) := x"DD";

signal Sel : unsigned(1 downto 0) := (others => '0');

signal Output1 : unsigned(7 downto 0);

signal Output2 : unsigned(7 downto 0);

begin

-- Stimuli for the selector signal

process is

begin

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= "UU";

wait;

end process;

-- MUX using if-then-else

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

if Sel = "00" then

Output1 <= Sig1;

elsif Sel = "01" then

Output1 <= Sig2;

elsif Sel = "10" then

Output1 <= Sig3;

elsif Sel = "11" then

Output1 <= Sig4;

else -- 'U', 'X', '-' etc.

Output1 <= (others => 'X');

end if;

end process;

-- Equivalent MUX using a case statement

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

case Sel is

when "00" =>

Output2 <= Sig1;

when "01" =>

Output2 <= Sig2;

when "10" =>

Output2 <= Sig3;

when "11" =>

Output2 <= Sig4;

when others => -- 'U', 'X', '-', etc.

Output2 <= (others => 'X');

end case;

end process;

end architecture;

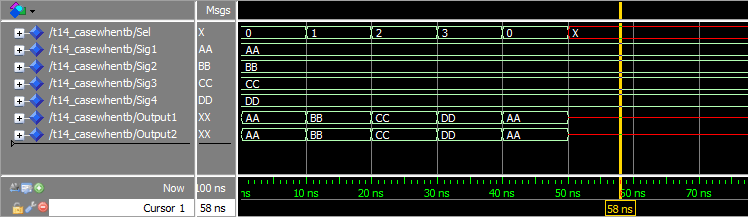

Het golfvormvenster in ModelSim nadat we op run hebben gedrukt en ingezoomd op de tijdlijn:

De uitvoer naar de simulatorconsole toen we op de run-knop in ModelSim drukten:

VSIM 2> run # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb

Analyse

Eerst hebben we een proces gemaakt met behulp van If-Then-Elsif-Else dat een van de signalen Sig1 zou doorsturen , Sig2 , Sig3 , of Sig4 , gebaseerd op de waarde van het selectorsignaal Sel .

Vervolgens hebben we een proces gemaakt dat precies hetzelfde deed, met behulp van de Case-When-instructie. We kunnen aan de golfvorm zien dat de uitgangssignalen van de twee processen, Output1 en Output2 , gedragen zich precies hetzelfde.

In ons voorbeeld is de Sel signaal heeft slechts vier wettelijke waarden. Maar als er een groter aantal mogelijkheden was geweest, kunnen we gemakkelijk zien dat de Case-When-instructie kan helpen om code leesbaarder te maken. Dit is de voorkeursmanier om zo'n component te maken door de meeste VHDL-ontwerpers.

Begrip van de multiplexer was het bonuspunt van deze oefening. Multiplexers, of kortweg MUX's, zijn centrale componenten in digitaal ontwerp. Het is gewoon een schakelaar die een van de verschillende ingangen selecteert en doorstuurt naar de uitgang.

Dit is een illustratie van hoe onze MUX het geselecteerde ingangssignaal doorstuurt:

We gebruikten de others clausule om alle waarden van Sel . op te vangen die geen enen of nullen waren. Zoals we hebben geleerd in de std_logic tutorial, kunnen deze signalen een aantal waarden hebben die niet '0' zijn. of '1' . Het is een goede ontwerppraktijk om met deze waarden om te gaan door 'X' . uit te voeren . Dit geeft een onbekende waarde aan op dit signaal, en het zal ook zichtbaar zijn in de stroomafwaartse logica.

We kunnen aan de golfvorm zien dat wanneer de Sel signaal werd rood, Output1 en Output2 ook gewijzigd in "XX" . Dit is when others => in actie.

Bovendien toont de console-uitvoer in ModelSim een waarschuwing vanwege de Sel signaal wordt ingesteld op "UU" . De berichten "** Waarschuwing:NUMERIC_STD."=":metawaarde gedetecteerd, terugkerende FALSE" verschijnen na een simulatietijd van 50 ns, precies wanneer de signalen rood worden.

Afhaalmaaltijden

- Case-When kan worden gebruikt in plaats van meerdere If-Then-Elsif-instructies

- De

when others =>kan worden gebruikt om een standaardkeuze te implementeren - Multiplexers worden bij voorkeur gemaakt met Case-When-statements

Ga naar de volgende tutorial »

VHDL

- Procedureverklaring - VHDL-voorbeeld

- Hoe gebruiken we molybdeen?

- Een lijst met strings maken in VHDL

- Simulatie stoppen in een VHDL-testbench

- Een PWM-controller maken in VHDL

- Hoe willekeurige getallen te genereren in VHDL

- Een procedure gebruiken in een proces in VHDL

- Een onzuivere functie gebruiken in VHDL

- Een functie gebruiken in VHDL

- Een eindige-toestandsmachine maken in VHDL

- Hoe een snijmolen te gebruiken