Inleiding tot Verilog

Verilog is een soort hardwarebeschrijvingstaal (HDL). Verilog is een van de twee talen die door het onderwijs en het bedrijfsleven worden gebruikt om FPGA's en ASIC's te ontwerpen. Als je niet bekend bent met hoe FPGA's en ASIC's werken, lees dan deze pagina voor een inleiding tot FPGA's en ASIC's. Verilog en VHDL zijn de twee meest gebruikte HDL's. In vergelijking met traditionele softwaretalen zoals Java of C, werkt Verilog heel anders. Laten we beginnen door naar een eenvoudig voorbeeld te kijken.

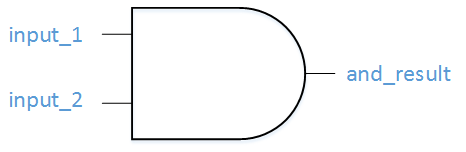

Eerst zullen we een Verilog-bestand maken dat beschrijft een En Poort. Als opfriscursus heeft een eenvoudige And Gate twee ingangen en één uitgang. De uitvoer is alleen gelijk aan 1 als beide ingangen gelijk zijn aan 1. Hieronder ziet u een afbeelding van de And Gate die we met Verilog zullen beschrijven.

An And Gate

An And Gate Laten we ernaartoe gaan! Een fundamentele eenheid van Verilog wordt een draad genoemd. Laten we voor nu aannemen dat een draad alleen een 0 of een 1 kan zijn. Hier is wat basisdraadlogica:

wire and_temp; assign and_temp = input_1 & input_2;

We maken een draad met de naam and_temp op de eerste regel code. Op de tweede regel van de code nemen we de draad die we hebben gemaakt en we toewijzen de draad. Om het toe te wijzen, gebruiken we de Booleaanse AND-functie die in Verilog de Ampersand (&) is. Als je de hierboven getoonde code zou beschrijven, zou je kunnen zeggen:"Het signaal and_temp krijgt input_1 AND-ed met input_2."

Input_1 en Input_2 zijn inputs voor dit stukje Verilog-code. Laten we de volledige lijst met in- en uitgangen tonen. Dit doe je in de module definitie. Module is een gereserveerd sleutelwoord in Verilog dat het maken van een codeblok met gedefinieerde in- en uitgangen laat zien.

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

Dit is je basismodule. Het definieert onze module genaamd example_and_gate en 3 signalen, 2 ingangen en 1 uitgang. Laten we alles samenvoegen om het bestand af te maken. Het enige wat we missen is de toewijzing van de output and_result . Een andere opmerking, // in Verilog wordt gebruikt voor een opmerking.

///////////////////////////////////////////////////////////////////////////////

// File Downloaded from http://www.nandland.com

///////////////////////////////////////////////////////////////////////////////

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

wire and_temp;

assign and_temp = input_1 & input_2;

assign and_result = and_temp;

endmodule // example_and_gate

Gefeliciteerd! U heeft uw eerste Verilog-bestand gemaakt.

Lijkt het alsof je veel code moest schrijven om een domme en poort te maken? Allereerst, en poorten zijn niet dom. Ten tweede heb je gelijk, HDL's hebben veel code nodig om relatief eenvoudige taken uit te voeren. U kunt enige troost putten uit het feit dat Verilog op zijn minst minder uitgebreid is dan VHDL. Wen er maar aan dat als je iets doet dat heel eenvoudig was in software, je aanzienlijk meer tijd nodig hebt in een HDL zoals Verilog of VHDL. Maar vraag gewoon een softwareman om te proberen een afbeelding te genereren voor een VGA-monitor die Conway's Game of Life weergeeft en kijk hoe hun hoofd ronddraait van verbazing! Die video is trouwens gemaakt met een FPGA. Dat lukt je snel genoeg!

Verilog