Impedantieregeling in PCB-ontwerp van snelle digitale schakelingen

Impedantiecontroletechnologieën zijn vrij belangrijk bij het ontwerpen van digitale schakelingen met hoge snelheid, waarbij effectieve methoden moeten worden toegepast om de uitstekende prestaties van hogesnelheidsprintplaten te garanderen.

Impedantieberekening en impedantieregeling van high-speed circuittransmissielijnen op PCB

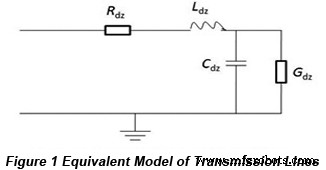

• Gelijkwaardig model op transmissielijnen

Figuur 1 toont het equivalente effect van transmissielijnen op PCB's, wat een structuur is met tandem en meervoudige condensator, weerstand en inductor (RLGC-model).

De typische waarde van tandemweerstand ligt in het bereik van 0,25 tot 0,55 ohm/voet en de weerstandswaarde van meerdere weerstanden blijft meestal vrij hoog. Met parasitaire weerstand, capaciteit en inductantie toegevoegd in PCB-transmissielijnen, wordt de algehele impedantie op transmissielijnen aangeduid als karakteristieke impedantie (Z0 ). De waarde van de karakteristieke impedantie is relatief klein op voorwaarde dat de lijndiameter groot is, de lijn dicht bij vermogen/aarde ligt of de diëlektrische constante hoog is. Figuur 3 toont het equivalente model van de transmissielijn met een lengte van dz, op basis waarvan de karakteristieke impedantie van de transmissielijn als formule kan worden afgeleid: . In deze formule verwijst L naar de inductantie van elke lengte-eenheid op de transmissielijn, terwijl C verwijst naar de capaciteit van elke lengte-eenheid op de transmissielijn.

. In deze formule verwijst L naar de inductantie van elke lengte-eenheid op de transmissielijn, terwijl C verwijst naar de capaciteit van elke lengte-eenheid op de transmissielijn.

• Impedantie- en vertragingsberekeningsformule van transmissielijnen op PCB

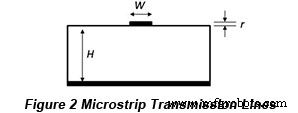

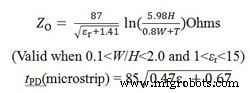

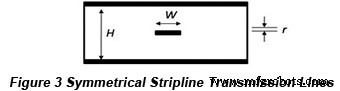

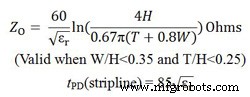

| Transmissielijnen op PCB | Formule voor impedantie- en vertragingsberekening |

|  |

|  |

In de bovenstaande formules, Z0 verwijst naar impedantie (Ohm), W verwijst naar de breedte van lijnen (inch), T verwijst naar de dikte van lijnen (inch), H verwijst naar de afstand tot de grond (inch), verwijst naar de relatieve diëlektrische constante van het substraat, en tPD verwijst naar de vertragingstijd (ps/inch).

• Lay-outregels voor impedantieregeling van transmissielijnen

Op basis van de bovenstaande analyse is de eenheidsvertraging van impedantie en signaal niet gerelateerd aan de frequentie van signalen, maar gerelateerd aan de bordstructuur, relatieve diëlektrische constante van bordmateriaal en fysieke kenmerken van routering. Deze conclusie is uiterst belangrijk om high-speed PCB te begrijpen en voor high-speed PCB-ontwerp. Bovendien is de transmissiesnelheid van de signaaltransmissielijn in de buitenste laag veel sneller dan die in de binnenste laag, dus met deze elementen moet rekening worden gehouden bij de opstelling van de lay-out van de belangrijkste lijnen.

Impedantieregeling is het belangrijke uitgangspunt voor de implementatie van signaaloverdracht. Volgens de kaartstructuur en de impedantieberekeningsformule van transmissielijnen is de impedantie echter alleen afhankelijk van het PCB-materiaal en de PCB-laagstructuur, waarbij de lijnbreedte en routeringskenmerken voor dezelfde lijn ongewijzigd blijven. Daarom zal de impedantie van een lijn niet veranderen op verschillende PCB-lagen, wat niet is toegestaan bij het ontwerpen van snelle circuits.

Voor dit artikel is een high-speed PCB met hoge dichtheid ontworpen en de meeste signalen aan boord hebben impedantie-eisen. De CPCI-signaallijn moet bijvoorbeeld een impedantie van 65 Ohm hebben, een differentieel signaal van 100 ohm en andere signalen van elk 50 ohm. Volgens de PCB-routeringsruimte moet een routering van ten minste tien lagen worden gebruikt en wordt een 16-laags PCB-ontwerpplan bepaald.

Aangezien de totale dikte van het bord niet groter mag zijn dan 2 mm, zijn er enkele problemen bij het stapelen, waarbij rekening wordt gehouden met enkele problemen:

1). Elke signaallaag heeft beeldvlakken ernaast om de impedantie en signaalkwaliteit te beschermen.

2). Elk krachtvliegtuig heeft een volledige grondlaag ernaast, zodat de prestaties van het vermogen goed kunnen worden gegarandeerd.

3). Het opstapelen van het bord vereist balans, waarbij kromtrekken van het bord wordt vermeden.

De diëlektrische constante van medium is ingesteld op 4,3. Op basis van het bovenstaande stapelontwerp moeten lijnbreedte en afstand tussen lijnen worden ingesteld op basis van het berekeningsresultaat om te zorgen voor de vereiste signaalimpedantie. De lijndikte wordt als volgt verkregen:

1). De breedte van de signaallijn op de oppervlaktelaag is 5mils met een impedantie van 58,7 Ohm.

2). De breedte van de CPCI-signaallijn op de oppervlaktelaag is 4,5 mils met een impedantie van 61,7 Ohm.

3). De breedte van de signaallijn in de binnenste laag is 4,5 mils met een impedantie van 50,2 Ohm.

4). De breedte van lijnen in het BGA-gebied in de binnenlaag en oppervlaktelaag is 4mils met een oppervlaktelaagimpedantie van 64,6 Ohm en een binnenlaagimpedantie van 52,7 Ohm.

5). De breedte van de differentiële microstriplijn in de binnenlaag is 5mils met de afstand tussen de lijnen 6mils en de impedantie 100,54Ohm.

6). De breedte van de differentiële striplijn in de binnenlaag is 4,5 mils met de afstand tussen de lijnen 10 mils en de impedantie 96,6 Ohm.

De afstand tussen de lijnen wordt als volgt ingesteld:

1). De afstand tussen signaallijnen (5mils) op de oppervlaktelaag is 5,0mils.

2). De afstand tussen CPCI-signaallijnen (4,5 mils) op de oppervlaktelaag is 9,0 mils.

3).. De afstand tussen signaallijnen (4,5 mils) op de binnenlaag is 7,0 mils.

4). De afstand tussen de lijnen op de oppervlaktelaag en de binnenlaag is 4,0 mils.

5). De afstand tussen differentiële signaallijnen op de binnenlaag en tussen hen en andere signaallijnen moet ten minste 25mils worden gehouden.

6). De afstand tussen differentiële signaallijnen op de oppervlaktelaag en tussen hen en andere signaallijnen moet ten minste 20 mils worden gehouden.

Na het printen van de PCB wordt de impedantie van het testbord getest door de POLAR-Cits500 impedantietester met resultaten in de volgende tabel. De gegevens geven aan dat de impedantie moet worden geregeld in het bereik van 50 Ohmۯ%, 60 Ohmۯ% en 100 Ohmۯ% tijdens het proces van high-speed PCB-ontwerp en fabricage.

| Vooraf ingestelde impedantie (Ohm) | Praktische impedantie (Ohm) |

| 50 | 47.52-52.33 |

| 60 | 57.65-61.35 |

| 100 | 93.65-106.35 |

LVDS en zijn impedantiecontrole op PCB's

• LVDS

LVDS is een type high-speed serieel signaaltransmissieniveau met voordelen van hoge transmissiesnelheid, laag stroomverbruik, sterk anti-interferentievermogen, lange transmissieafstand en haalbare matching. De toepassingsgebieden van LVDS omvatten computer, communicatie en consumptie.

• Impedantieontwerp van LVDS

LVDS heeft een spanningszwaai van slechts 350 MV met de langste transmissieafstand van meer dan 10 meter. Om ervoor te zorgen dat signalen niet worden beïnvloed door gereflecteerd signaal in het proces van signaaloverdracht in transmissielijnen, moet de impedantie van transmissielijnen onder controle zijn met een enkele lijnimpedantie van 50 Ohm en een differentiële impedantie van 100 Ohm. In de praktische toepassing kan de impedantie worden geregeld door een redelijke stapeldikte en mediumparameters in te stellen, de lijnbreedte en afstand tussen lijnen aan te passen en de impedantie van enkele lijnen en differentiële lijnen te berekenen met behulp van enkele snelle simulatie-analysetools.

Meestal is het echter relatief moeilijk om te voldoen aan de vereisten van enkellijnige impedantie en differentiële impedantie. Enerzijds wordt het instelbereik van lijnbreedte W en afstand tussen lijnen S geregeld door fysieke ontwerpruimte. De routing en lijnbreedte in de marginconnectoren met BGA of DIP wordt bijvoorbeeld beïnvloed door padgrootte en afstand. Aan de andere kant zal de verandering van W en S het resultaat van enkele lijn en differentiële impedantie beïnvloeden. Tot nu toe is het gemakkelijk en handig om de relatie tussen de vooraf ingestelde lijndikte en lijnafstand te achterhalen.

• LVDS-routeringsregels

Over het algemeen wordt differentiële signaalroutering geïmplementeerd volgens de ontwerpregels voor impedantie, die in staat zijn om LVDS-kwaliteit te garanderen. In de praktische routering moet LVDS voldoen aan de volgende regels:

1). Differentiële paren moeten zo kort mogelijk zijn, lijnen moeten recht zijn en het aantal doorgaande gaten moet worden verkleind. De afstand tussen signaallijnen in differentiële paren moet hetzelfde zijn. Al deze regels dragen bij aan het vermijden van lange routes en talrijke afslagen. Wat betreft afslagen, moet een afslag van 45 graden worden gebruikt in plaats van 90 graden.

2). De afstand tussen differentiële paren moet meer dan 10 keer worden gehandhaafd om de overspraak tussen lijnen te verminderen. Indien nodig kunnen doorlopende gaten tussen differentiële paren worden geplaatst voor isolatie.

3). LVDS kan niet over het oppervlak worden verdeeld. Hoewel twee differentiële signalen wederzijds terugkerende paden zijn, kan het signaalretourpad niet worden ingekort als gevolg van splitsing over het oppervlak. Niettemin zullen transmissielijnen mogelijk leiden tot impedantiediscontinuïteit als gevolg van een gebrek aan beeldvlakken.

4). Vermijd differentieel signaal tussen lagen. Tijdens de fabricage van PCB's is de nauwkeurigheid van de stapeluitlijning tussen lagen veel lager dan de nauwkeurigheid van de etsing in dezelfde laag plus het gemiddelde verlies tijdens het stapelen, wat allemaal leidt tot de verandering van de differentiële impedantie tussen differentiële paren.

5). Bij het ontwerp van de impedantie moet de koppelingsmethode worden gebruikt.

6). Er moet een geschikte PCB-stapelstructuur worden ingesteld om de isolatie tussen spanningsniveausignalen en LVDS te waarborgen. Waar mogelijk kunnen signalen zoals snelle TTL/CMOS op verschillende lagen worden ingesteld, geïsoleerd van LVDS-routering door grond- en stroomlagen.

7). Differentiële signaalparen moeten compatibel zijn met de lengte van de routering.

Handige bronnen

• Elementen die van invloed zijn op de karakteristieke impedantie van PCB's en oplossingen

• Overwegingen bij het impedantie-ontwerp voor flexibele PCB's

• Impedantie van high-speed PCB-vermogen analyseren en verbieden

• Impedantiecontrole van via's en de invloed ervan op signaalintegriteit in PCB-ontwerp

• Full Feature PCB-productieservice van PCBCart - Meerdere opties met toegevoegde waarde

• Geavanceerde PCB-assemblageservice van PCBCart - Start vanaf 1 stuk

Industriële technologie

- Motorbesturingscircuits

- PCB-layoutsoftware

- PCB Corrosie Oorzaken:

- Overwegingen bij PCB-layout

- Overwegingen bij impedantie-ontwerp voor flexibele printplaten

- Tegenslagen en oplossingen in RF PCB-ontwerp

- 3 routeringstechnieken op PCB high-speed signaalcircuitontwerp

- Tips voor snelle lay-out

- Signaalintegriteitsanalyse en PCB-ontwerp op high-speed digitaal-analoog gemengd circuit

- Uitdagingen bij het ontwerpen van high-speed PCB's voor signaalintegriteit en hun oplossingen

- Impedantiecontrole van via's en de invloed ervan op signaalintegriteit in PCB-ontwerp