Digital Ramp ADC

Ook bekend als de trap-oprit , of gewoon teller A/D-converter, dit is ook vrij eenvoudig te begrijpen, maar heeft helaas verschillende beperkingen.

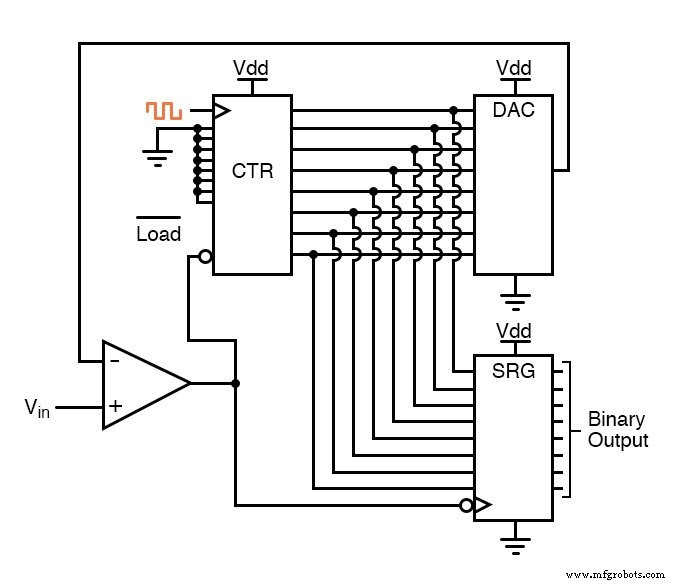

Het basisidee is om de uitgang van een vrijlopende binaire teller aan te sluiten op de ingang van een DAC, vervolgens de analoge uitgang van de DAC te vergelijken met het analoge ingangssignaal dat moet worden gedigitaliseerd en de uitgang van de comparator te gebruiken om de teller te vertellen wanneer hij moet stoppen tellen en resetten. Het volgende schema toont het basisidee:

Naarmate de teller bij elke klokpuls optelt, geeft de DAC een iets hogere (positievere) spanning af. Deze spanning wordt door de comparator vergeleken met de ingangsspanning.

Als de ingangsspanning groter is dan de DAC-uitgang, zal de uitgang van de comparator hoog zijn en zal de teller normaal blijven tellen. Uiteindelijk zal de DAC-uitgang echter de ingangsspanning overschrijden, waardoor de uitgang van de comparator laag wordt.

Dit zal ervoor zorgen dat er twee dingen gebeuren:ten eerste zal de overgang van hoog naar laag van de uitgang van de comparator ervoor zorgen dat het schuifregister de binaire telling die door de teller wordt uitgevoerd, "laadt", waardoor de uitgang van het ADC-circuit wordt bijgewerkt; ten tweede ontvangt de teller een laag signaal op de active-low LOAD-ingang, waardoor deze bij de volgende klokpuls wordt gereset naar 00000000.

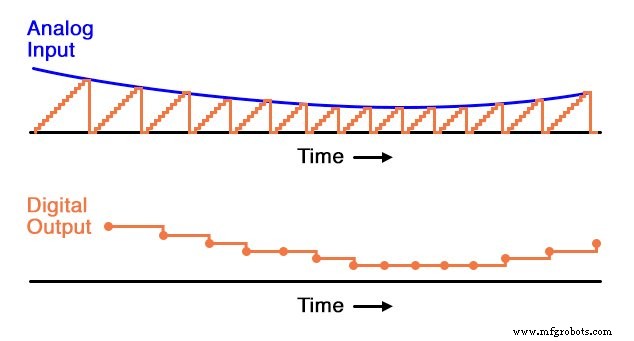

Het effect van dit circuit is om een DAC-uitgang te produceren die oploopt tot het niveau van het analoge ingangssignaal, het binaire getal dat met dat niveau overeenkomt, uit te voeren en opnieuw te beginnen. Uitgezet in de tijd ziet het er als volgt uit:

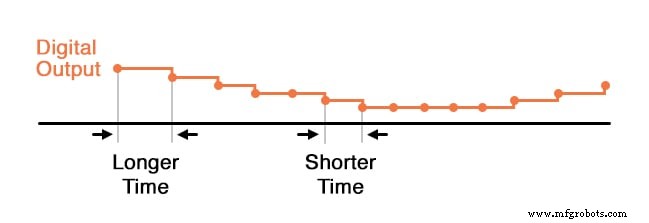

Merk op hoe de tijd tussen updates (nieuwe digitale uitgangswaarden) verandert afhankelijk van hoe hoog de ingangsspanning is. Voor lage signaalniveaus zijn de updates vrij dicht bij elkaar geplaatst. Voor hogere signaalniveaus staan ze verder uit elkaar in de tijd:

Voor veel ADC-toepassingen zou deze variatie in updatefrequentie (sampletijd) niet acceptabel zijn. Dit, en het feit dat de schakeling aan het begin van elke telcyclus helemaal vanaf 0 moet tellen, zorgt voor een relatief langzame bemonstering van het analoge signaal, plaatst de ADC met digitale helling in het nadeel ten opzichte van andere tellerstrategieën.

Industriële technologie