De lengte van de ontwerpcyclus in mede-ontworpen SoC's verkorten met Renode

In dit artikel leggen we uit hoe het gebruik van open-source functionele simulators zoals Antmicro's Renode een integraal onderdeel kan zijn van hardware-software co-design inspanningen .

In dit artikel leggen we uit hoe het gebruik van open-source functionele simulatoren zoals Antmicro's Renode een integraal onderdeel kan zijn van hardware-software co-design inspanningen.

Naarmate markten meer eisen van hun embedded systemen, worden SoC's van de volgende generatie complexer, wat leidt tot langere ontwerpcycli en stijgende kosten, volgens Semico Research.

De frustrerende realiteit voor apparaatfabrikanten is dat de enige manier om de nieuwe en innovatieve functies, betere beveiliging en betere prestaties te leveren waar hun klanten om vragen, is om deel te nemen aan "whole stack" co-design, evoluerende hardware, firmware, runtime (OS) en ontwikkelingstoolchain in tandem. Hierdoor kunnen hardware- en softwareteams complexe afwegingen maken rond waar in de stack om functionaliteit en optimalisaties te implementeren.

Helaas is co-design vaak de belangrijkste drijfveer voor het verlengen van ontwerpcycli - en dus ook van de kosten - wanneer de juiste simulatietools niet aanwezig zijn.

In dit artikel leggen we uit hoe het gebruik van open-source functionele simulators zoals Antmicro's Renode een integraal onderdeel kan zijn van hardware-software co-design inspanningen. Verder laten we u een voorbeeld zien van hoe Renode-gebruikers de tool kunnen gebruiken om de lengte van hun ontwerpcycli drastisch te verminderen, klanten een eenvoudige en effectieve manier te bieden om hun oplossingen te evalueren en om parallel softwaremateriaal aan te passen. met inspanningen voor hardware-integratie.

Waar softwaresimulators tekort kunnen schieten

Het belang van het kiezen van de juiste simulatietool wordt het best geïllustreerd in het geval van Dover Microsystems.

Dover's CoreGuard®-technologie is de enige oplossing die misbruik van softwarekwetsbaarheden voorkomt en processors in staat stelt zichzelf te verdedigen tegen netwerkgebaseerde aanvallen. Dover was in staat om dit te bereiken door acht jaar onderzoek en ontwikkeling - eerst als de grootste uitvoerder in het DARPA Crash Program en vervolgens bij Draper Labs - wat resulteerde in een unieke hardware/software hybride oplossing voor embedded systemen.

Deze hybride oplossing vereist een nauwe integratie tussen zowel hardware- als softwarecomponenten. CoreGuard silicon IP is een schildwachtprocessor die fungeert als lijfwacht en ingebedde systemen beschermt tegen cyberaanvallen. Het controleert elke instructie die door de hostprocessor wordt uitgevoerd om er zeker van te zijn dat het voldoet aan een gedefinieerde set beveiligings-, veiligheids- en privacyregels, micropolicies genaamd, de softwarecomponent van CoreGuard. Als een instructie een bestaande regel schendt, stopt CoreGuard de uitvoering ervan voordat er schade kan worden aangericht.

Om dit te bereiken, moet CoreGuard gelijke tred houden met de uitvoering van de hostprocessor. Dat wil zeggen dat het gemiddeld instructies moet kunnen terugtrekken (goedkeuren via microbeleid) met dezelfde snelheid als de hostprocessor die wordt beschermd. Het is ook wenselijk dat CoreGuard de hoeveelheid geheugen die nodig is voor het beheer van metagegevens minimaliseert.

Om te voldoen aan de prestatie-, kracht- en gebiedseisen is daarom een complex samenspel van optimalisaties van zowel hardware- als softwarelagen vereist.

Het hardwareteam van Dover gebruikt een standaard op SystemVerilog gebaseerd proces en toolchain. De eerste prototypes van het CoreGuard-systeem zijn gebouwd op op RISC-V gebaseerde SoC's. Omdat CoreGuard naast het hardware-IP een substantiële softwarecomponent heeft, was het belangrijk dat het softwareteam ruim voordat er hardware-prototypes beschikbaar waren, van start kon gaan.

Het softwareteam in Dover gebruikte aanvankelijk de Spike RISC-V ISA-softwaresimulator die beschikbaar is via de RISC-V GitHub-repo's. Ze ondervonden twee problemen bij het baseren van hun commerciële ontwikkeling van CoreGuard rond Spike:

- Spike biedt geen realistische randapparatuur; dat wil zeggen, Spike is een ISA-simulator, geen SoC-simulator. Het Dover-team begon randapparatuur zoals UART's en permanente opslag toe te voegen aan Spike, en dit was veel werk.

- Spike is per definitie RISC-V-specifiek, maar de eerste klanten van Dover Microsystems zijn zowel op RISC-V als op Arm gebaseerd.

Deze tekortkomingen benadrukten Dover's behoefte aan een flexibele multi-architectuursimulator met het concept van perifere modellen om te gebruiken in plaats van Spike.

Hoe Renode voorziet in belangrijke co-designbehoeften

Geconfronteerd met vergelijkbare heterogene hardware/software co-design engineering uitdagingen die voortvloeien uit het werken met open-source softcores, vroege software voor toonaangevende computerplatforms, FPGA SoC's en opkomende CPU-architecturen zoals RISC-V, Antmicro - een op open source gerichte technologie- en serviceprovider—ontwikkelde een flexibel simulatieraamwerk genaamd Renode.

Renode is een hiërarchisch, modulair simulatieraamwerk gericht op het uitvoeren van echte productie (dwz ongewijzigde) firmware in een verscheidenheid aan complexe systemen, waaronder onderling verbonden multi-node-, multi-architectuur-, heterogene, MCU-niveau en Linux-compatibele systemen.

Om deze verschillende niveaus van complexiteit aan te pakken, is Renode gebouwd rond een sterk begrip van abstractie en hanteert het een objectgeoriënteerde, modulaire benadering van systeemsimulatie. Kernen en randapparatuur worden gezien als bouwstenen die via interfaces in verschillende configuraties kunnen worden aangesloten, wat een weerspiegeling is van hoe echte SoC's worden gebouwd.

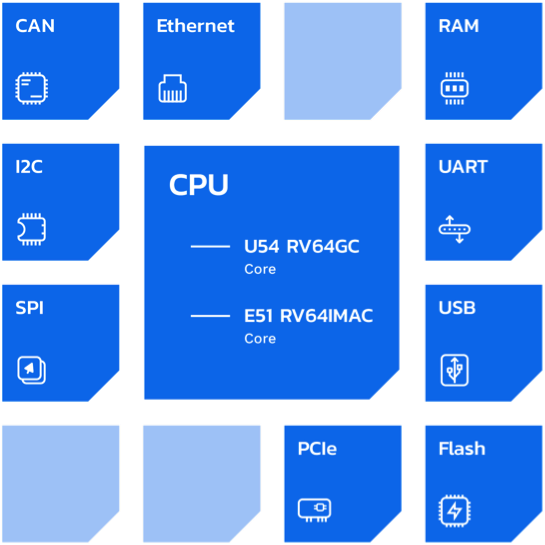

Figuur 1. Een voorbeeld van een gesimuleerde RISC-V SoC.

Figuur 1 toont een voorbeeld van een gesimuleerde RISC-V SoC. Elke bouwsteen, inclusief de CPU, heeft een set eigenschappen en API's die kunnen worden gebruikt om het simulatiemodel van de gehele SoC te construeren. Evenzo kunnen enkele knooppunten verder worden gecombineerd tot een systeem met meerdere knooppunten met behulp van gevirtualiseerde draadloze en bekabelde verbindingen (6LoWPAN, UART, Ethernet enz.). Dit alles vereist geen wijzigingen in de codebase van Renode, maar wordt gedaan via configuratie en scripting, waardoor de leercurve wordt verminderd en de fragmentatie van de codebase wordt beperkt.

Het flexibele karakter van het Renode-framework, de open-sourcebeschikbaarheid en het bestaan van commerciële ondersteuning door de auteurs maakten het voor Dover gemakkelijk om eerst een prototype-implementatie van hun gewenste workflow te bouwen en vervolgens Antmicro te contracteren om te implementeren (en vrij te geven in de open- source domain) functionaliteiten die Renode nog beter geschikt maakten voor hun use case, zoals uitvoering per instructie.

Met Renode kunnen de technici van Dover nu:

- Schakel tussen op Arm en RISC-V gebaseerde integratie-inspanningen met dezelfde setup.

- Prototype-SoC's (zowel referentie/minimaal als door de klant gedefinieerd) op verschillende niveaus van detail/getrouwheid.

Modelleer de hardware-architectuurspecificatie van de hardwaregroep van Dover en schrijf en test vervolgens firmware tegen die modellen, terwijl de hardware in ontwikkeling is.

Hoe Renode de ontwerpcyclus van Dover aanzienlijk verminderde

Dover's CoreGuard-technologie is een hybride cyberbeveiligingsproduct waarin zowel hardware- als softwareontwerpen evolueren. Daarom is het belangrijk dat het ontwikkelingsproces van Dover parallelle ontwikkeling en testen van zowel hardware als software mogelijk maakt.

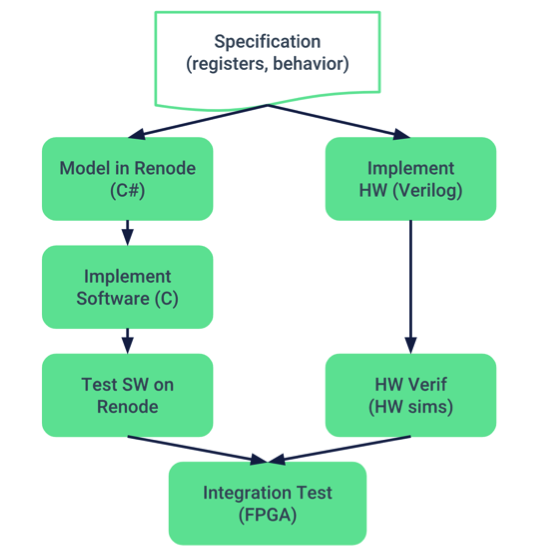

Figuur 2. Het ontwikkelingsproces dat door Dover wordt gebruikt.

Dover gebruikt het ontwikkelingsproces dat in figuur 2 is geschetst. De hardware- en softwareteams werken samen aan de hardware-interface (die uiteraard zal blijven evolueren). Terwijl het hardwareteam blokken begint te implementeren in SystemVerilog, maakt het softwareteam modellen van de nieuwe blokken in C#, de moedertaal die ten grondslag ligt aan Renode. Het softwareteam kan dan firmware schrijven die communiceert met de nieuwe hardware-interfaces, en die software testen onder Renode-simulatie. Uiteindelijk wordt de software uitgevoerd op een FPGA-emulator.

Dit ontwikkelingsproces, mogelijk gemaakt door Renode, heeft Dover geholpen bij het optimaliseren van zowel 'low fidelity'- als 'high fidelity'-simulaties.

Hoewel deze "low-fidelity"-simulatie alle hardwarelogica van CoreGuard wegneemt, vindt Dover deze opstelling nog steeds nuttig in de volgende contexten:

- Microbeleid-foutopsporing: Wanneer er nieuw CoreGuard-microbeleid wordt ontwikkeld, willen we snel verschillende softwaretests herhalen om het gedrag te controleren.

- Demo's en klantvoorbeelden: Voor CoreGuard-demonstraties is pure softwaresimulatie vaak voldoende om een potentiële klant te informeren over de mogelijkheden van CoreGuard® en om interesse voor verdere discussie te stimuleren. Bovendien zal Dover vaak een "SDK" aan klanten leveren, bestaande uit deze "low fidelity" -simulator met een paar vooraf gedefinieerde microbeleidsregels, zodat de klant kan "spelen" met CoreGuard, inclusief mogelijk het uitvoeren van CoreGuard-microbeleid tegen de software van de klant.

In 'high fidelity'-simulaties, die een nauwkeuriger hardwaremodel nabootsen, heeft het technische team van Dover een aantal voordelen van Renode kunnen herkennen, waaronder:

- Integreren met verschillende niet-ELF (bijv. scatter-load) binaire formaten die worden gebruikt door hardware-opstart-ROM's.

- Ontwikkelen en testen van het opstartproces; kopiëren van flash naar RAM, apparaten initialiseren.

- Foutopsporing in busverkeer met behulp van Renode-instrumentatie.

- Debuggen van randapparatuur (UART's, PIC's, de CoreGuard-interface zelf) door middel van instrumentatie.

- Spelen met de geheugenkaart.

- Implementatie van HDMI-videofirmware, voordat de hardware werkte.

Zoals eerder aangegeven, zijn er enkele uitdagende prestatie- en gebiedsbeperkingen die oplossingen van de volgende generatie, zoals CoreGuard, opleggen aan SoC-ontwerpteams tijdens de implementatie.

Om de prestaties te verhogen en het geheugengebruik te verminderen, is er een breed scala aan optimalisaties die moeten worden doorgevoerd, die vaak de grens tussen hardware en software overschrijden.

Het is van cruciaal belang dat ontwerpteams in staat zijn om een groot aantal mogelijke co-optimalisatietechnieken voor hardware/software en compromissen te verkennen, zonder een groot, geserialiseerd "eerst-hardware-dan-software-ontwikkelingsproces". Een flexibele software-functionele simulator zoals Renode stelt Dover-ingenieurs in staat samen te werken over de hardware-software kloof om optimale afwegingen te vinden tussen hardware- en softwarecomplexiteit, waardoor het een integraal onderdeel wordt van hun inspanningen.

Ga naar renode.io voor meer informatie over hoe Renode co-designprojecten kan stroomlijnen. Vraag een demo aan om CoreGuard in actie te zien voor meer informatie over hoe CoreGuard embedded systemen kan beschermen tegen netwerkgebaseerde aanvallen.

Dit artikel is mede geschreven door Michael Gielda, VP Business Development en mede-oprichter van Antmicro.

Industrieartikelen zijn een vorm van inhoud waarmee branchepartners nuttig nieuws, berichten en technologie kunnen delen met lezers van All About Circuits op een manier waarop redactionele inhoud niet goed geschikt is. Alle brancheartikelen zijn onderworpen aan strikte redactionele richtlijnen met de bedoeling de lezers nuttig nieuws, technische expertise of verhalen te bieden. De standpunten en meningen in brancheartikelen zijn die van de partner en niet noodzakelijk die van All About Circuits of zijn schrijvers.

Ingebed

- Wat is ingebed systeemontwerp:stappen in het ontwerpproces

- 4 uitdagingen op het gebied van additieve productie die met software kunnen worden opgelost

- Interview met expert:nTopology CEO over het bevorderen van AM-potentieel met generatieve ontwerpsoftware

- De toekomst bouwen met robotica

- Optimaliseren van de RF-feedline in PCB-ontwerp

- Ingesloten ontwerp met FPGA's:een project bouwen

- Hoe u de beste CAD-software voor sieradenontwerp kiest

- De productie van gendergevoelige en geïndividualiseerde producten met de zekering 1

- Overstappen naar CMMS-software met Steve Ricard (PODCAST)

- Hoe u het beheer van groothandelsorders onder de knie krijgt met de juiste software

- De juiste match vinden met uw cloudproductiesoftwaretechnologie