Ingesloten ontwerp met FPGA's:een project bouwen

Noot van de redactie:naarmate er steeds meer geavanceerde algoritmen verschijnen voor slimme productontwerpen, hebben ontwikkelaars vaak moeite om embedded systemen te implementeren die in staat zijn om aan de bijbehorende verwerkingsvereisten van deze algoritmen te voldoen. FPGA's kunnen de vereiste prestaties leveren, maar ontwerpen met FPGA's werd lang beschouwd als beperkt tot de bevoegdheid van FPGA-programmeerexperts. Tegenwoordig heeft de beschikbaarheid van krachtigere FPGA's en effectievere ontwikkelomgevingen FPGA-ontwikkeling echter breed toegankelijk gemaakt. In dit fragment, hoofdstuk 4 uit het boek Architecting High-Performance Embedded Systems, biedt de auteur een uitgebreid overzicht van FPGA-apparaten, implementatietalen en het FPGA-ontwikkelingsproces, evenals een gedetailleerd overzicht van hoe u aan de slag kunt gaan met het implementeren van FPGA's in uw eigen ontwerp. Het volledige fragment wordt gepresenteerd in de volgende reeks afleveringen:

Noot van de redactie:naarmate er steeds meer geavanceerde algoritmen verschijnen voor slimme productontwerpen, hebben ontwikkelaars vaak moeite om embedded systemen te implementeren die in staat zijn om aan de bijbehorende verwerkingsvereisten van deze algoritmen te voldoen. FPGA's kunnen de vereiste prestaties leveren, maar ontwerpen met FPGA's werd lang beschouwd als beperkt tot de bevoegdheid van FPGA-programmeerexperts. Tegenwoordig heeft de beschikbaarheid van krachtigere FPGA's en effectievere ontwikkelomgevingen FPGA-ontwikkeling echter breed toegankelijk gemaakt. In dit fragment, hoofdstuk 4 uit het boek Architecting High-Performance Embedded Systems, biedt de auteur een uitgebreid overzicht van FPGA-apparaten, implementatietalen en het FPGA-ontwikkelingsproces, evenals een gedetailleerd overzicht van hoe u aan de slag kunt gaan met het implementeren van FPGA's in uw eigen ontwerp. Het volledige fragment wordt gepresenteerd in de volgende reeks afleveringen:

1:Hardwarebronnen

2:Implementatietalen

3:Ontwikkelingsproces

4:Een project bouwen (dit artikel)

5:implementatie

Aangepast van het ontwerpen van hoogwaardige ingebedde systemen, door Jim Ledin.

Uw eerste FPGA-project ontwikkelen

In deze sectie zullen we een eenvoudig maar compleet project ontwikkelen en implementeren met behulp van een Xilinx Artix-7 FPGA-apparaat dat is geïnstalleerd op een Digilent Arty A7-ontwikkelbord. Dit bord is er in twee varianten, een goedkopere versie (US $129) met een modelnummer dat eindigt op-35T en een meer capabele, maar duurdere versie (US $249) met een modelnummer dat eindigt op -100T. Het enige verschil tussen de twee borden is het model van de Artix-7 FPGA dat op het bord is geïnstalleerd. Zoals je zou verwachten, heeft de -35T minder middelen beschikbaar dan de -100T.

U kunt voor dit project de -35T- of de -100T-variant gebruiken. Het enige verschil in het ontwikkelingsproces is het specificeren van het juiste bordmodel wanneer dat nodig is. In latere hoofdstukken is de -100T-variant echter vereist vanwege de resourcevereisten van het voorbeeldproject van een digitale oscilloscoop, dus het meer capabele bord wordt aanbevolen.

De Arty A7-borden zijn te koop op https://store.digilentinc.com/arty-a7-artix-7-fpga-development-board-for-makers-and-hobbyists/ en van andere bronnen, zoals Amazon.

Voor dit project zijn de bronnen op het bord van belang het FPGA-apparaat zelf, evenals de vier schakelaars, vier drukknoppen en vijf LED's. Dit project laat zien hoe je de Vivado-toolsuite installeert, een project maakt, HDL-code invoert, de code test en uiteindelijk een bitstream produceert en deze naar het bord downloadt. Nadat u de bitstream naar het bord hebt gedownload, kunt u de werking van het systeem handmatig testen. U zult ook zien hoe u het FPGA-beeld in het flashgeheugen op het Arty A7-bord programmeert, zodat het wordt geladen en uitgevoerd telkens wanneer het bord wordt ingeschakeld.

Projectbeschrijving

Dit project zal een vier-bits binaire opteller in de FPGA implementeren. Dit is met opzet een heel eenvoudig ontwerp omdat de focus hier ligt op het instellen van de tools en het leren gebruiken ervan, en niet op het implementeren van een complex HDL-model.

De vier schakelaars op het bord vertegenwoordigen een 4-bits binair getal en de vier drukknoppen vertegenwoordigen een ander 4-bits getal. De FPGA-logica voert continu een optelbewerking uit tussen deze twee getallen en geeft het resultaat weer als een 4-bits binair getal op vier LED's, waarbij een vijfde LED de carry-bit vertegenwoordigt.

De 4-bits optelcode is gebaseerd op het enkel-bits volledige optelcircuit dat wordt beschreven in de Hardware-ontwerptalen sectie van Hoofdstuk 1 , Architecten van hoogwaardige embedded systemen .

De Vivado-tools installeren

We zullen de Xilinx Vivado-suite met FPGA-ontwikkeltools gebruiken voor dit project en voor projecten in toekomstige hoofdstukken. Deze tools zijn gratis beschikbaar en worden ondersteund op Windows- en Linux-besturingssystemen. U kunt de tools op beide besturingssystemen installeren. De beschrijving in deze sectie behandelt de Windows-versie van de tools, maar als je op Linux installeert, zouden de verschillen duidelijk moeten zijn. Werken met de Vivado-tools zou bijna identiek moeten zijn op de verschillende besturingssystemen:

- Als je er nog geen hebt, maak dan een Xilinx-gebruikersaccount aan op https://www.xilinx.com/registration/create-account.html.

- Bezoek https://xilinx.com en log in op uw gebruikersaccount. Nadat u bent ingelogd, gaat u naar de downloadpagina voor hulpprogramma's op https://www.xilinx.com/support/download.html.

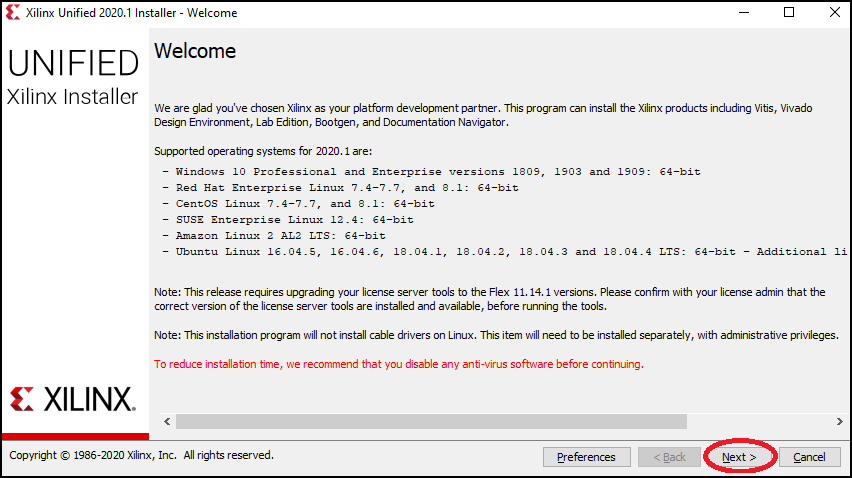

- Download het Xilinx Unified Installer:Windows Self-Extracting Web Installer . U moet waarschijnlijk de nieuwste beschikbare versie selecteren, maar als u de versie die in dit boek wordt gebruikt wilt volgen, selecteert u versie 2020.1 .

- Het installatiebestand heeft een naam die lijkt op Xilinx_ 1_0602_1208_Win64.exe. Zoek dit bestand in uw downloadmap en voer het uit. Als een dialoogvenster u waarschuwt voor het installeren van een app die niet door Microsoft is geverifieerd, klikt u op Toch installeren .

- Wanneer de Welkom scherm verschijnt, klik op Volgende :

Figuur 4.3 – Welkomstdialoogvenster Installateur

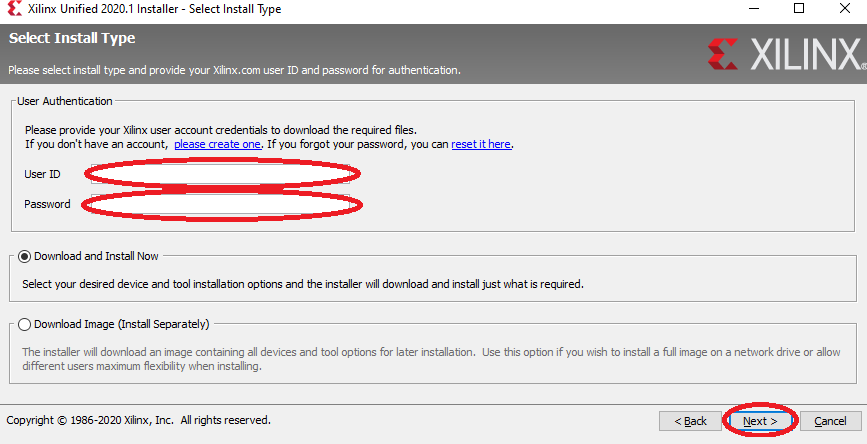

- Voer in het volgende scherm uw gebruikers-ID en wachtwoord voor xilinx.com in en klik vervolgens op Volgende :

Figuur 4.4 – Aanmeldingsdialoogvenster voor installateur

- In het volgende dialoogvenster wordt u gevraagd enkele licentieovereenkomsten te accepteren. Vink de vakjes aan met de tekst Ik ga akkoord en klik vervolgens op Volgende .

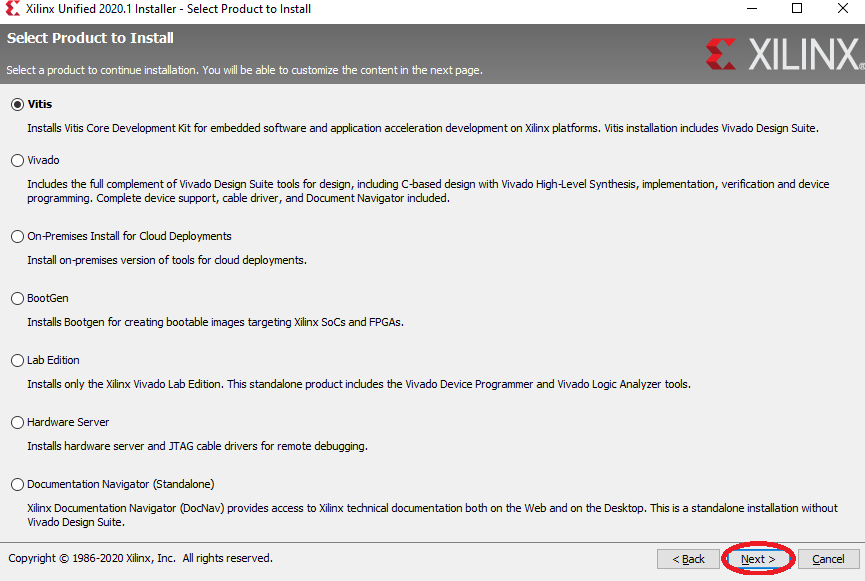

- Verlaat in het volgende dialoogvenster Vitis geselecteerd als het te installeren product en klik op Volgende . Vitis bevat de Vivado-toolsuite samen met een verzameling andere Xilinx-ontwikkeltools:

Figuur 4.5 – Dialoogvenster voor productselectie van installateur

- In het volgende dialoogvenster kunt u de te installeren softwarecomponenten selecteren. Laat de selecties op hun standaardwaarden staan en klik op Volgende .

- In het volgende dialoogvenster kunt u een doelmap selecteren en opties voor programmasnelkoppelingen specificeren. Een doelmap van C:\Xilinx is een geschikte locatie. Maak deze map aan als deze niet bestaat. Klik op Volgende .

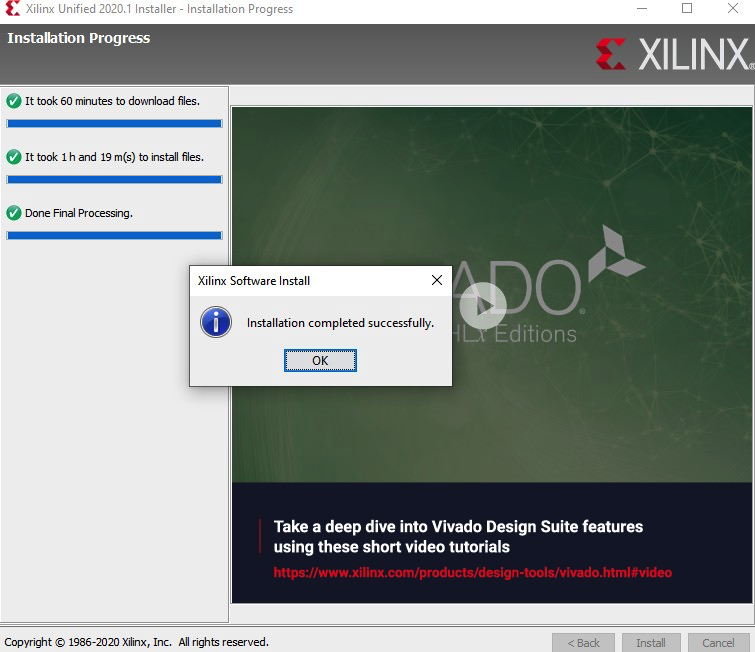

- Het volgende dialoogvenster toont een samenvatting van de installatie-opties. Klik op Installeren om verder te gaan met de installatie. Afhankelijk van de snelheid van uw computer en uw internetverbinding, kan de installatie enkele uren duren:

Figuur 4.6 – Dialoogvenster Installatie voltooid

Nadat de installatie is voltooid, zullen we ons eerste project maken.

Een project maken

Volg deze stappen om het 4-bits binaire optellerproject voor het Arty A7-bord te maken en te bouwen:

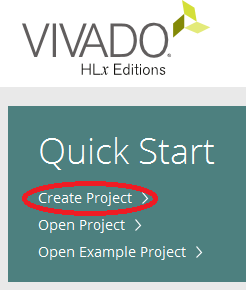

- Zoek het bureaubladpictogram met de titel Vivado 2020.1 (of zoek naar uw versienummer, indien anders) en dubbelklik erop.

- Als Vivado het hoofdscherm weergeeft, klik je op Project maken in de Snelstart sectie:

Figuur 4.7 – Vivado Quick Start-dialoogvenster

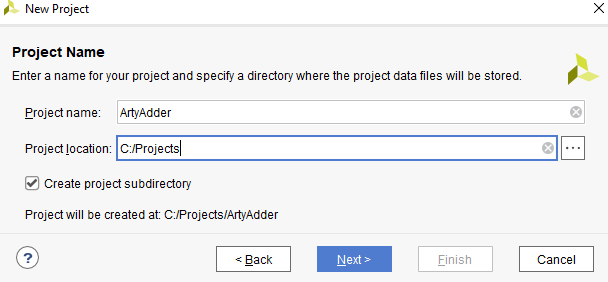

- Hiermee wordt het Creëer een nieuw Vivado-project . gestart tovenaar. Klik op Volgende om de Projectnaam . te bereiken pagina en voer ArtyAdder in als de projectnaam. Selecteer een geschikte maplocatie voor het project en vink het vakje aan om een submap te maken en klik vervolgens op Volgende . Voorbeelden in dit boek gebruiken de map C:\Projects als locatie voor alle projecten:

Figuur 4.8 – Dialoogvenster Projectnaam

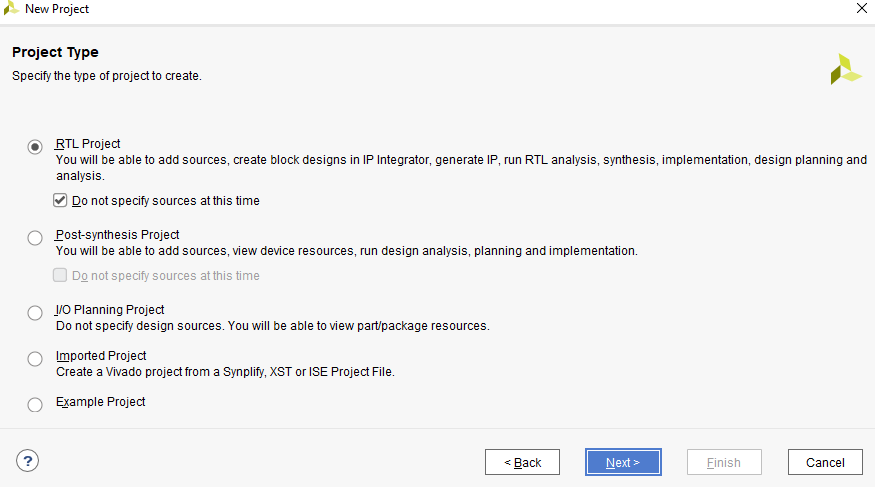

- In het Projecttype dialoogvenster, selecteer RTL-project en vink het vakje aan naast Geef op dit moment geen bronnen op . Klik op Volgende :

Figuur 4.9 – Dialoogvenster Projecttype

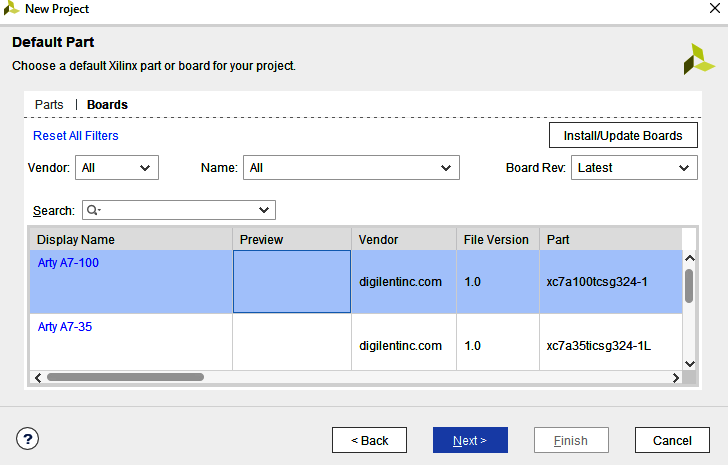

- In het Standaardgedeelte dialoogvenster, klik op de Boards en typ Arty in de Zoeken veld. Afhankelijk van het type board dat je hebt (of als je nog geen board hebt), selecteer je de Arty A7-100 of Arty A7-35 en klik op Volgende :

Figuur 4.10 – Standaard onderdeel dialoog

- In de Samenvatting van het nieuwe project dialoogvenster, klik op Voltooien .

We hebben nu een leeg project aangemaakt. In de volgende sectie zullen we VHDL-bronbestanden maken die het ontwerp van de logische schakelingen voor dit project bevatten.

VHDL-bronbestanden maken

De volgende stappen beschrijven het proces van het maken van VHDL-bronbestanden, het invoeren van de broncode en het compileren van het FPGA-ontwerp:

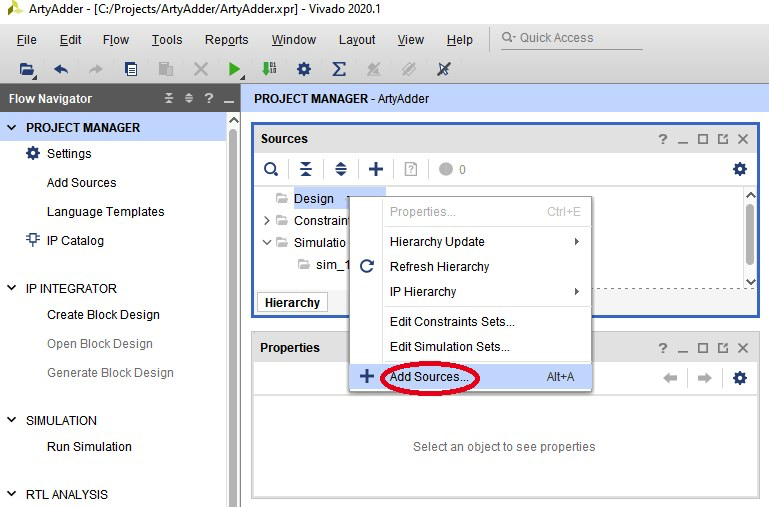

- In de Bronnen subvenster, klik met de rechtermuisknop op Ontwerpbronnen en selecteer Bronnen toevoegen... :

Figuur 4.11 – Bronnen toevoegen... menuselectie

- In de Bronnen toevoegen dialoogvenster, zorg ervoor dat Ontwerpbronnen toevoegen of maken is geselecteerd en klik vervolgens op Volgende .

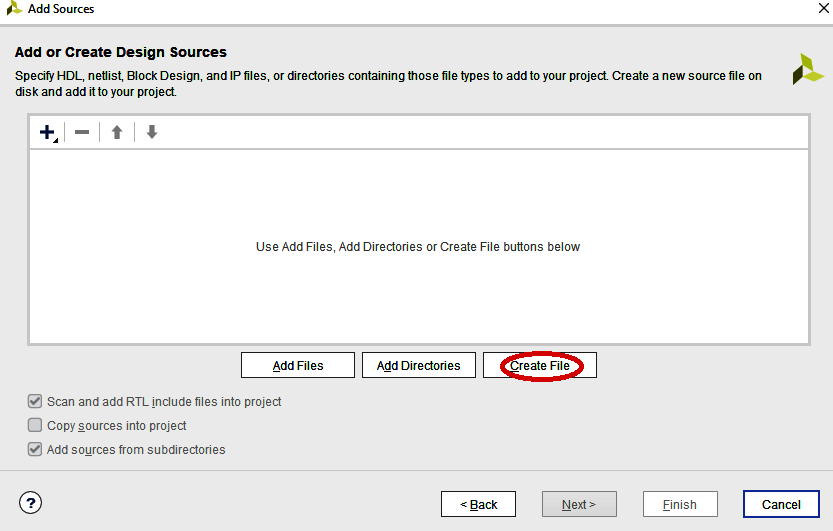

- In de Ontwerpbronnen toevoegen of maken dialoogvenster, klik op Bestand maken :

Figuur 4.12 – Dialoogvenster Ontwerpbronnen toevoegen of maken

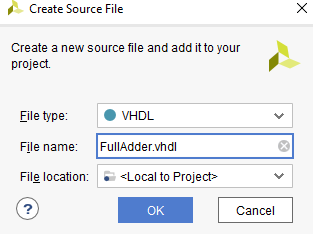

- Voer de bestandsnaam FullAdder.vhdl in en klik op OK :

Figuur 4.13 – Dialoogvenster Bronbestand maken

- Herhaal de vorige twee stappen om nog een bestand met de naam Adder4.vhdl te maken en klik vervolgens op Voltooien in de Ontwerpbronnen toevoegen of maken dialoog.

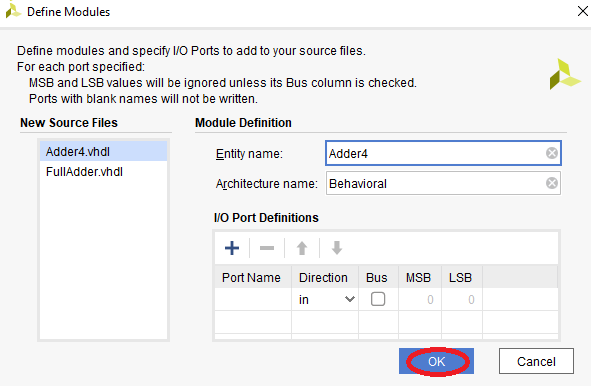

- De Define Modules dialoogvenster verschijnt hierna. We gaan hier niets invullen. Klik op OK om dit te sluiten U wordt gevraagd of u zeker weet dat u deze waarden wilt gebruiken. Klik op Ja :

Figuur 4.14 – Dialoogvenster Modules definiëren

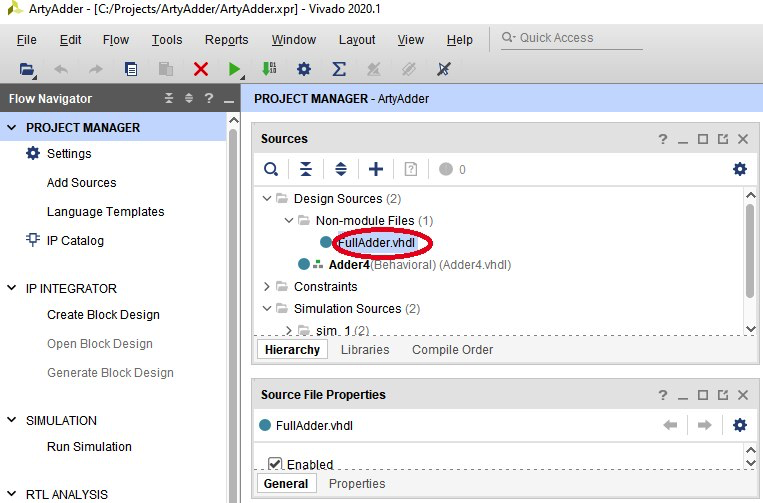

- Breid de Niet-module-bestanden uit onder Ontwerpbronnen en dubbelklik vervolgens op FullAdder.vhdl. Er wordt een editorvenster geopend met het lege FullAdder.vhdl-bestand:

Figuur 4.15 – Nieuw aangemaakt bronbestand

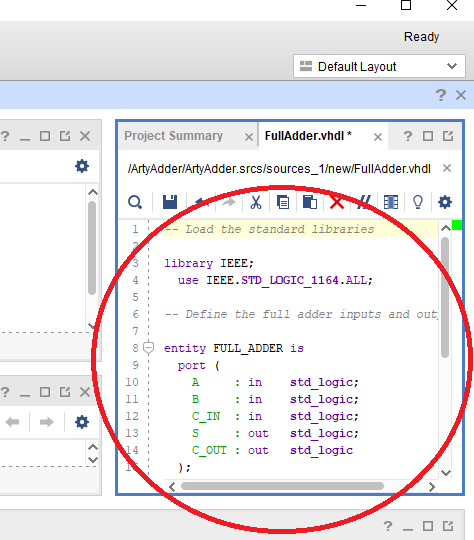

- Voer de volgende VHDL-code in het FullAdder.vhdl-editorvenster in:

-- Laad de standaardbibliothekenbibliotheek IEEE; gebruik IEEE.STD_LOGIC_1164.ALL;-- Definieer de volledige opteller in- en outputsentity FULL_ADDER is poort (A:in std_logic; B:in std_logic; C_IN:in std_logic; S:out std_logic; C_OUT:out std_logic); end entiteit FULL_ADDER; -- Definieer het gedrag van de volledige adderarchitectuur GEDRAG van FULL_ADDER isbegin S <=(A XOR B) XOR C_IN; C_OUT <=(A AND B) OR ((A XOR B) AND C_IN);end architectuur GEDRAG;

Dit is dezelfde single-bit full adder-code die we hebben onderzocht in de Hardware-ontwerptalen sectie van Hoofdstuk 1, Hoogwaardige ingebedde systemen ontwerpen . Figuur 4.16 toont de code in het Vivado-editorvenster:

Figuur 4.16 – FullAdder.vhdl broncode

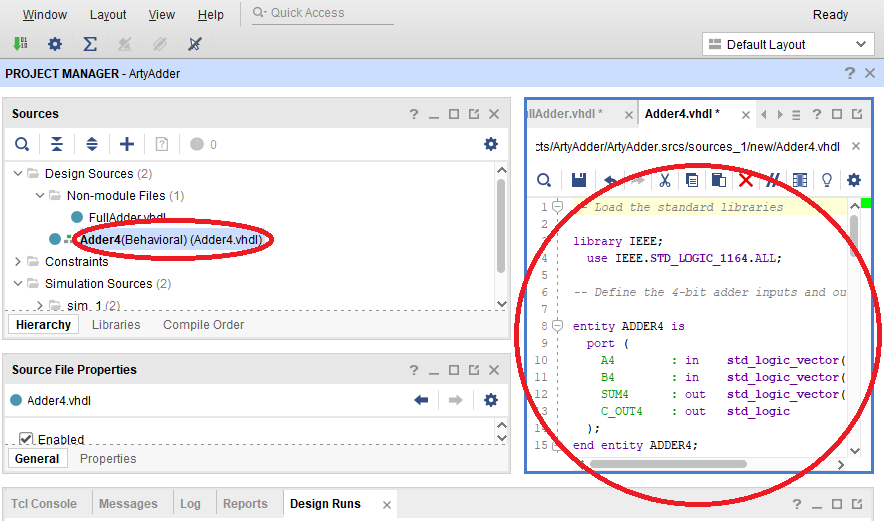

- Dubbelklik op dezelfde manier op Adder4(Behavioral) (Adder4.vhdl) onder Ontwerpbronnen . Verwijder de automatisch ingevulde inhoud van de Adder4.vhdl editorvenster en voer de volgende code in in de Adder4.vhdl redacteur:

-- Laad de standaardbibliothekenbibliotheek IEEE; gebruik IEEE.STD_LOGIC_1164.ALL;-- Definieer de 4-bits opteller inputs en outputsentity ADDER4 is poort (A4:in std_logic_vector (3 downto 0); B4:in std_logic_vector (3 downto 0); SUM4:out std_logic_vector (3 downto 0 ); C_OUT4 :out std_logic ); end entity ADDER4;-- Definieer het gedrag van de 4-bits adderarchitectuur GEDRAG van ADDER4 is -- Verwijs naar de vorige definitie van de volledige addercomponent FULL_ADDER is poort (A:in std_logic; B:in std_logic;C_IN:in std_logic;S:uit std_logic;C_OUT:uit std_logic); eindcomponent; -- Definieer de signalen die intern worden gebruikt in het 4-bits optellersignaal c0, c1, c2 :std_logic;begin -- De overdrachtsinvoer naar de eerste opteller is ingesteld op 0 FULL_ADDER0 :FULL_ADDER poortkaart ( A => A4 (0)), B => B4(0), C_IN => '0', S => SUM4(0), C_OUT => c0 ); FULL_ADDER1:FULL_ADDER poortkaart (A => A4(1), B => B4(1), C_IN => c0, S => SUM4(1), C_OUT => c1); FULL_ADDER2:FULL_ADDER poortkaart (A => A4(2), B => B4(2), C_IN => c1, S => SUM4(2), C_OUT => c2); FULL_ADDER3 :FULL_ADDER poortkaart (A => A4(3), B => B4(3), C_IN => c2, S => SUM4(3), C_OUT => C_OUT4 );end architectuur GEDRAG;

Deze code maakt vier exemplaren van de enkelbits volledige opteller. De carry naar de minst significante opteller wordt op nul gezet en de carry van elke opteller rimpelt naar de volgende meest significante opteller. Het resultaat van het optellen van twee 4-bits getallen is een 4-bits resultaat en een single-bit carry:

Figuur 4.17 – Adder4.vhdl broncode

In het volgende artikel wordt uitgelegd hoe u het ontwerp kunt testen en hoe u ons ontwerp voor het Arty-bord kunt implementeren.

Herdrukt met toestemming van Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin is de CEO van Ledin Engineering, Inc. Jim is een expert in het ontwerpen, ontwikkelen en testen van embedded software en hardware. Hij is ook bekwaam in het beoordelen van cyberbeveiliging van embedded systemen en het testen van penetratie. Hij heeft een B.S. graad in lucht- en ruimtevaarttechniek van Iowa State University en een M.S. graad in elektrotechniek en computertechniek aan het Georgia Institute of Technology. Jim is een geregistreerde professionele elektrotechnisch ingenieur in Californië, een Certified Information System Security Professional (CISSP), een Certified Ethical Hacker (CEH) en een Certified Penetration Tester (CPT).

Jim Ledin is de CEO van Ledin Engineering, Inc. Jim is een expert in het ontwerpen, ontwikkelen en testen van embedded software en hardware. Hij is ook bekwaam in het beoordelen van cyberbeveiliging van embedded systemen en het testen van penetratie. Hij heeft een B.S. graad in lucht- en ruimtevaarttechniek van Iowa State University en een M.S. graad in elektrotechniek en computertechniek aan het Georgia Institute of Technology. Jim is een geregistreerde professionele elektrotechnisch ingenieur in Californië, een Certified Information System Security Professional (CISSP), een Certified Ethical Hacker (CEH) en een Certified Penetration Tester (CPT). Verwante inhoud:

- Ingesloten ontwerp met FPGA's:hardwarebronnen

- Ingesloten ontwerp met FPGA's:implementatietalen

- Ingesloten ontwerp met FPGA's:ontwikkelingsproces

- Open-source tools helpen FPGA-programmering te vereenvoudigen

- Implementatie van drijvende-kommaalgoritmen in FPGA's of ASIC's

- Gebruik maken van FPGA's voor diepgaand leren

- Softwaretools migreren GPU-code naar FPGA's voor AI-toepassingen

- FPGA's verdringen ASIC's in op Subaru Eyesight gebaseerde ADAS

Abonneer u voor meer Embedded op de wekelijkse e-mailnieuwsbrief van Embedded.

Ingebed

- Productie van vloeibare additieven:3D-objecten bouwen met vloeistof

- Wat is ingebed systeemontwerp:stappen in het ontwerpproces

- Big data omzetten in slimme data met ingebouwde AI

- High-performance interconnects bouwen met meerdere PCIe-generaties

- Arrow Electronics lanceert Europese FPGA-ontwikkelaarswedstrijd

- Ontwerpkit meet bloeddruk met optische sensor

- Defensie-grade FPGA debuteert met vroege toegang

- Botten bouwen met Raspberry Pi en Python

- Een segway bouwen met Raspberry Pi

- GoPiGo v2 met Windows IoT

- All-in met additief