Neuromorfe AI-chips voor het versterken van neurale netwerken debuut

Innatera, de Nederlandse startup die neuromorfe AI-versnellers maakt voor het versterken van neurale netwerken, heeft zijn eerste chips geproduceerd, hun prestaties gemeten en details van hun architectuur onthuld.

Het bedrijf heeft ook aangekondigd dat de mede-oprichter van Cadence en Synopsys, Alberto Sangiovanni-Vincentelli, zich bij het bedrijf heeft gevoegd als voorzitter van de raad van bestuur. De veteraan in de sector is momenteel professor aan de University of California in Berkeley.

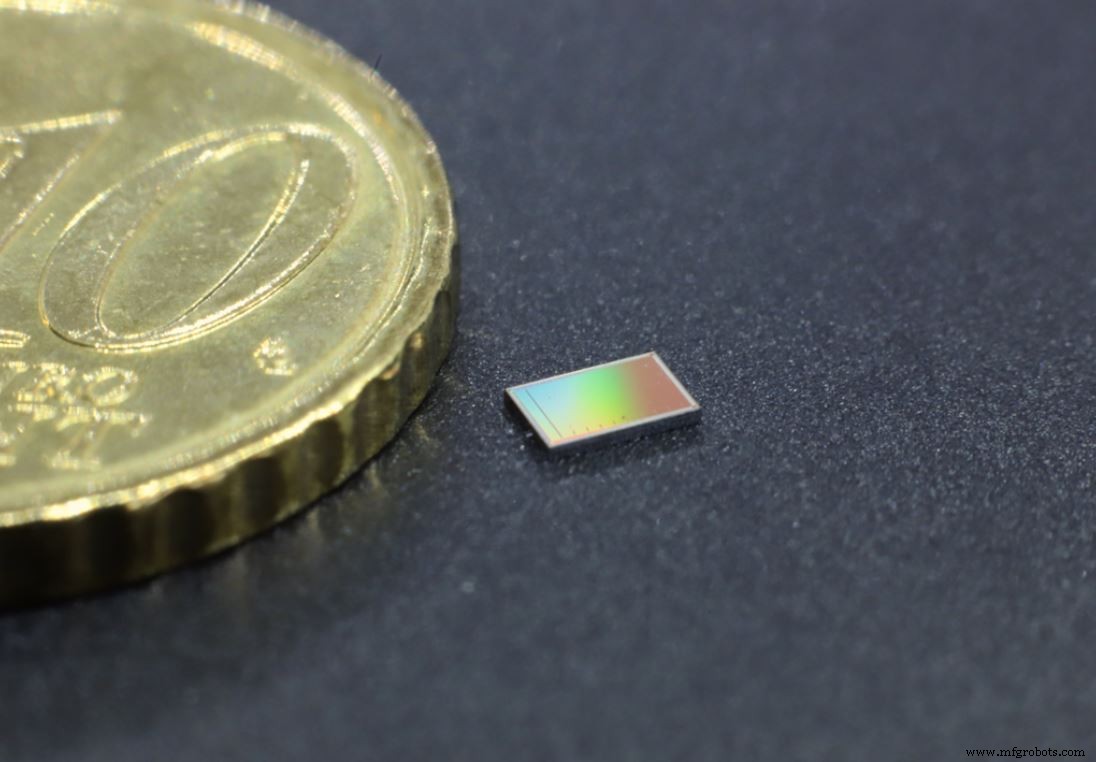

Innatera's chip is ontworpen om verschillende SNN's voor audio-, gezondheids- en radartoepassingen te versnellen (Afbeelding:Innatera)

De Innatera-chip is ontworpen om spiking neurale netwerken (SNN's) te versnellen, een type neuromorf AI-algoritme op basis van hersenbiologie dat de timing van spikes in een elektrisch signaal gebruikt om patroonherkenningstaken uit te voeren. SNN's hebben een compleet andere structuur dan de reguliere AI-algoritmen en vereisen daarom speciale hardware voor acceleratie, maar ze bieden doorgaans een aanzienlijk stroomverbruik en latentievoordelen voor sensoredge-toepassingen.

De meeste andere bedrijven die werken aan het verbeteren van neurale netwerkalgoritmen en hardware (bijvoorbeeld Prophesee) richten zich op afbeeldingen en videostreams. Innatera heeft besloten zich te concentreren op audio (geluids- en spraakherkenning), gezondheid (monitoring van vitale functies) en radar (voor gebruik door consumenten/IoT, zoals valsensoren voor ouderen die de privacy behouden).

Marco Jacobs (Afbeelding:Innatera)

"Deze sensoren hebben tijdreeksgegevens, in plaats van beelden die erg parallel zijn", zegt Marco Jacobs, Innatera VP marketing en bedrijfsontwikkeling, in een interview met EE Times . "Onze array is vooral goed in het verwerken van tijdreeksgegevens... het past goed bij de technologie. Ook vanuit marktperspectief zien we veel interessante toepassingen op dit gebied en niet zo veel oplossingen die daarop inspelen.”

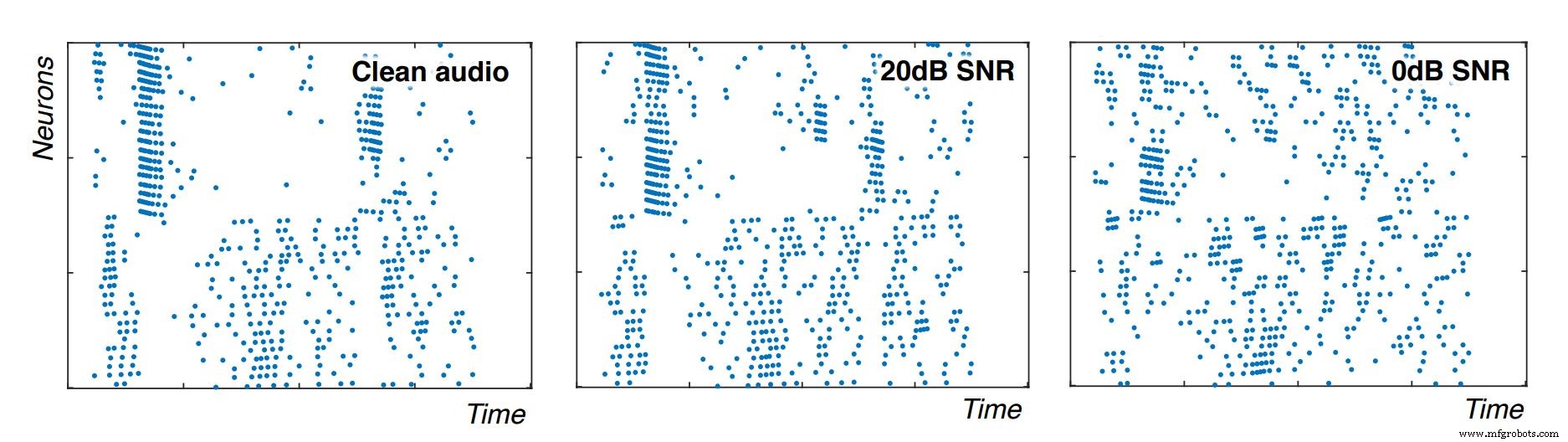

Een ander ding dat deze drie toepassingen gemeen hebben, is dat aangezien verwerking in het sensorknooppunt vereist is, de vermogensomhulling erg krap is. In de tests van Innatera vereiste elke piekgebeurtenis (elk neuron dat afvuurde als reactie op invoergegevens) minder dan een picoJoule aan energie - eigenlijk minder dan 200 femtoJoules in TSMC 28nm, bevestigde Innatera. Dit benadert de hoeveelheid energie die wordt gebruikt door biologische neuronen en synapsen. Een typische toepassing voor het spotten van trefwoorden voor audio vereist minder dan 500 piekgebeurtenissen per gevolgtrekking, wat resulteert in "diepe sub-milliWatt vermogensdissipatie", aldus Innatera's CEO, Sumeet Kumar. In dit geval vertegenwoordigen clusters van neuronen die samen vuren verschillende fonemen in spraak.

Clusters van neuronen die vuren (groepen stippen hier) vertegenwoordigen de detectie van fonemen in spraak. Omdat de invoergegevens meer ruis bevatten, zijn meestal dezelfde clusters aanwezig, hoewel ze moeilijker te herkennen zijn (Afbeelding:Innatera)

Verwerkingsarchitectuur

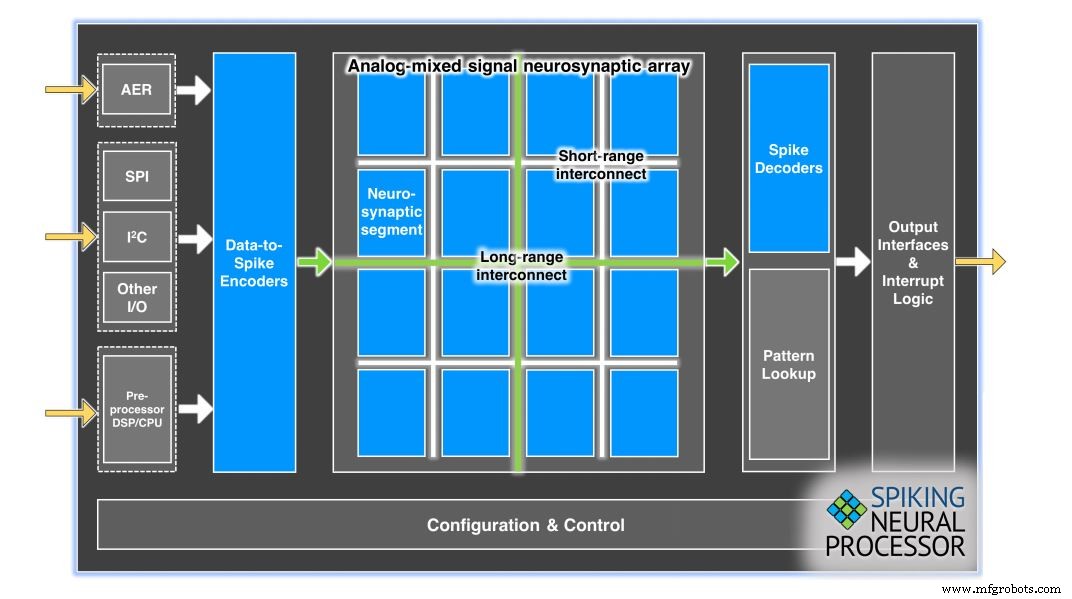

De spiking neurale processor van Innatera gebruikt een parallelle reeks spiking neuronen en synapsen om continue SNN's te versnellen met fijnkorrelige temporele dynamiek. Het apparaat is een versneller met analoog/gemengd signaal, ontworpen om gebruik te maken van het vermogen van SNN om het begrip tijd op te nemen in de manier waarop de gegevens worden verwerkt.

Innatera's krachtige neurale processor bevat een enorm parallelle neuro-synaptische array en spike-encoders en -decoders (Afbeelding:Innatera)

Een van de belangrijkste aspecten van de computerstructuren van Innatera is de programmeerbaarheid, wat om twee redenen belangrijk is.

Eerst verschillende SNN's op de chip programmeren. Neuronen moeten op een flexibele manier worden verbonden - de hersenen gebruiken zeer complexe neurale netwerktopologieën om dingen efficiënt te doen, waarvoor complexe verbindingen tussen neuronen nodig zijn, die opnieuw moeten worden gemaakt in silicium.

Sumeet Kumar (Afbeelding:Innatera)

Ten tweede om de prestaties te optimaliseren. In plaats van informatie als bits in woorden weer te geven, wordt informatie in een SNN weergegeven als nauwkeurig getimede pieken. De timing van de pieken moet op een zeer fijnmazig niveau worden gemanipuleerd om inzichten over de gegevens te extraheren. De neuronen en de verbindingen daartussen (de synapsen) moeten daarom complex timinggedrag vertonen. Dit gedrag kan worden aangepast via de SDK van Innatera om de prestaties te optimaliseren.

Innatera beschrijft zijn chip als analoog gemengd signaal of "digitaal ondersteunde analoog". Neuronen en synapsen zijn geïmplementeerd in analoog silicium om een ultralaag stroomverbruik te behouden. Analoge elektronica maakt ook continue tijdnetwerken mogelijk (digitale elektronica zou discretisatie vereisen). Dit is belangrijk voor SNN's omdat hun aard betekent dat ze inherent een notie van tijd hebben en in staat moeten zijn om bepaalde toestanden gedurende een bepaalde periode vast te houden.

"Dit doen is veel gemakkelijker in het analoge domein - je hoeft de complexiteit van het behouden van de status niet naar de netwerktopologie te verplaatsen," zei Kumar. “Onze compute-elementen behouden die staatsinformatie natuurlijk. Dit is de reden waarom we dingen in het analoge domein doen.”

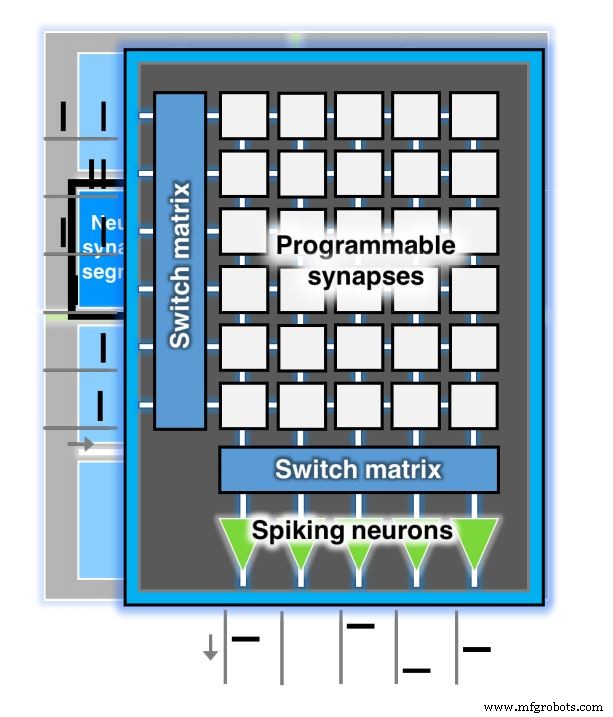

Een compute-segment in de array van Innatera, waar de neuronen zijn ontworpen om zorgvuldig op elkaar te worden afgestemd. Programmeerbare synapsen zijn gerangschikt in een kruisbalkstructuur met meerdere niveaus. (Zwarte lijnen/streepjes hier vertegenwoordigen input- en outputpieken) (Afbeelding:Innatera)

Kleine inconsistenties in fabricage tussen rekenelementen op de chip en tussen verschillende chips kunnen een probleem zijn voor het nauwkeurig implementeren van neurale netwerken in het analoge domein. De oplossing van Innatera is om neuronen te groeperen in wat het segmenten noemt, die zorgvuldig zijn ontworpen om de padlengtes en het aantal neuronen aan te passen.

Het segmentontwerp "stelt ons in wezen in staat om het beste van analoge circuits te gebruiken en tegelijkertijd deze niet-idealiteiten die je normaal gesproken in een analoog circuit zou hebben, te minimaliseren", zei Kumar. "Dit alles werd in wezen gedaan om ervoor te zorgen dat neuronen in een segment deterministisch gedrag vertonen en dat ze functioneren op een manier die vergelijkbaar is met hun directe buren."

Inconsistenties tussen verschillende chips kunnen problemen veroorzaken wanneer hetzelfde getrainde netwerk wordt uitgerold naar apparaten in het veld. Innatera lost dit op met software.

"Mismatch en variabiliteit worden diep in de SDK aangepakt", zei Kumar. "Als je een krachtige gebruiker bent, kunnen we je daar iets van vertellen, maar een typische programmeur hoeft zich daar geen zorgen over te maken."

Applicatiespecifiek

Innatera, een spin-out van de Technische Universiteit Delft, werkte al met omzetklanten aan haar SNN-algoritmen voordat ze overstapte naar hardware en tegen het einde van 2020 een seed-ronde van € 5 miljoen (ongeveer $ 6 miljoen) ophaalde.

"We werken met een aantal klanten samen sinds de tijd dat we het bedrijf zijn begonnen, en deze afspraken zijn nog steeds aan de gang - ze zijn aanzienlijk volwassener geworden", zei Kumar. "We hopen later dit jaar samen met een aantal van deze klanten meer demonstraties te kunnen geven."

Kumar zei dat het bedrijf zijn focus als bedrijf voor computeroplossingen behoudt, dat wil zeggen dat het kant-en-klare oplossingen zal leveren die zowel hardware- als applicatiespecifieke SNN-algoritmen bevatten.

De eerste chip van Innatera is geschikt voor audio-, gezondheids- en radartoepassingen. De roadmap van het bedrijf kan verder geoptimaliseerde chips voor elk van de toepassingen bevatten.

"We hebben het apparaat zo ontworpen dat we een breed scala aan spiking neurale netwerken konden versnellen," zei Kumar. “[Onze chip] kan deze netwerken in verschillende applicatiedomeinen implementeren. Maar als we dieper ingaan op domeinen, kan het nodig zijn om het hardware-ontwerp te optimaliseren, en dit is iets waar we in de toekomst naar zullen kijken. Op dit moment is de hardware niet al te gespecialiseerd in een specifieke klasse van applicaties of enige stijl van het versterken van neurale netwerken, het doel is om een verscheidenheid van hen over het algemeen binnen de architectuur te ondersteunen.”

Monsters van de eerste chip zijn op schema om voor eind 2021 beschikbaar te komen.

>> Dit artikel is oorspronkelijk gepubliceerd op onze zustersite, EE Tijden.

Verwante inhoud:

- AI-chip richt zich op low-power edge-apparaten

- Gereedschapsketen, sensorbord verbeteren AI-chip-ecosysteem

- Nieuwe AI-versnellingsmodules verbeteren edge-prestaties

- AI aan de rand:waar moet je op letten in 2021

- Hoe AI of Things (AIoT) op MCU's te implementeren

Abonneer u voor meer Embedded op de wekelijkse e-mailnieuwsbrief van Embedded.

Ingebed

- Co-simulatie voor op Zynq gebaseerde ontwerpen

- Renesas:autochips gebruikt door Nissan voor zijn nieuwe Skyline ProPILOT 2.0

- CEVA:tweede generatie AI-processor voor diepe neurale netwerkworkloads

- Pleidooi voor neuromorfe chips voor AI-computing

- Low-power radarchip maakt gebruik van spiking neurale netwerken

- Lanner:LTE-ready edge gateway gecertificeerd voor IoT en SD-WAN op mobiele netwerken

- IBM bij SPIE:zeven verbeteringen voor meer dan 7nm-chips

- NPE is Amerikaans debuut voor Campetella Robotic Center

- 3G is dood:wat nu voor productontwerpers?

- LoRaWAN vervangt tijdelijk 5G-netwerken voor IoT

- Lattice Semiconductor lanceert chips speciaal ontworpen voor industriële automatisering