Voordelige crossover-processor ondersteunt eindpuntinferentie

BRISTOL, VK — XMOS heeft zijn Xcore-processorkern aangepast voor machine learning, waardoor een crossover-processor voor AIoT-toepassingen is ontstaan. De Xcore.ai is beschikbaar vanaf $ 1.

Xcore.ai, de derde generatie producten gebouwd op het eigen kernontwerp van het bedrijf, is ontworpen voor realtime AI-inferentie en besluitvorming in eindpuntapparaten en kan ook signaalverwerkings-, controle- en communicatiefuncties aan.

Nieuw bij deze chip van de derde generatie is een vectorpijplijnmogelijkheid voor machine learning-toepassingen. Het is de enige crossover-processor in zijn soort die binaire (1-bit) neurale netwerken ondersteunt, die steeds belangrijker worden voor ultra-low power AI in de eindpunttoepassingen, omdat ze orde-van-grootte verbetering bieden in prestaties en geheugendichtheid. voor een bescheiden vermindering van de nauwkeurigheid (de Xcore.ai ondersteunt ook 32-bits, 16-bits en 8-bits nummers).

De Xcore.ai voegt zich bij een nieuwe klasse van AI-compatibel systeem op chips voor eindpunttoepassingen, de crossover-processor (Afbeelding:XMOS)

Xcore.ai voegt zich bij een opkomende klasse van eindpuntprocessors met AI-mogelijkheden, de crossover-processor. Deze term, bedacht door NXP, beschrijft een belangrijke nieuwe categorie apparaten met de prestaties van een applicatieprocessor gecombineerd met het gebruiksgemak, het lage stroomverbruik en de realtime werking van een microcontroller.

"Als je met klanten praat over 'microcontrollers', denken ze aan Cortex-M0-, M3- of M4-apparaten die binnenkomen voor 75 cent of minder, met relatief lage prestaties, honderd MIPS of zo. Dan zijn 'SoC's' misschien iets met quad-A53-kernen, dat draait op een gigahertz. Er is een groot gat voor dingen in het midden, zoals processors voor spraak, wat een bijzonder moeilijk wiskundig probleem is, waarvoor duizenden MIPS nodig zijn. Er is dus een grote kloof met een heel groot en belangrijk toepassingsgebied precies in het midden, en het verdient een naam”, zegt Mark Lippett, CEO van XMOS, in een exclusief interview met EETimes.

Spraakinterfaces

Het eerder aangekondigde product van de tweede generatie van het bedrijf, de XVF3510, werd in juli 2019 gelanceerd als een ASIC voor spraakinterfaces, maar onder de motorkap is het silicium ook gebaseerd op het eigen Xcore-ontwerp van het bedrijf, geleverd met firmware. Referentieontwerpen voor far-field spraakoplossingen op basis van de XVF3510 zijn gekwalificeerd voor Amazon's Alexa Voice Service.

Gezien de geschiedenis van XMOS in de spraaksector, is het geen verrassing dat de Xcore.ai-chip in eerste instantie gericht zal zijn op spraakinterface-applicaties die AI nodig hebben voor trefwoorddetectie of woordenboekfuncties.

“Laten we absoluut duidelijk zijn, spraak is de belangrijkste AI-workload op het eindpunt en zal dat waarschijnlijk nog geruime tijd blijven. Maar om spraakinterfaces beter te maken, zul je merken dat apparaten meer multimodaal zullen worden,” zei Lippett, die een trend beschrijft voor het gebruik van verschillende soorten sensoren om applicaties meer contextbewust te maken, of dat nu het detecteren van de aanwezigheid van een persoon is of het detecteren waar ze spreken van.

Mark Lippett (Afbeelding:XMOS)

"Er zijn veel mogelijkheden om gebruikerservaringen te verbeteren door niet alleen naar audio te luisteren, maar door meer te doen dan alleen dat," zei hij.

Veel toepassingen voor AI in IoT-apparaten hangen af van een combinatie van privacy, beveiliging en veiligheid die verwerking op het eindpunt vereist. Lippett beschreef veiligheidsvoorzieningen op apparaten die bijvoorbeeld stem en radar gebruiken om de oven uit te schakelen als er alleen kinderen in de keuken aanwezig zijn.

Xcore.ai zal daarom op de markt gaan met bibliotheken die zijn bedoeld voor het maken van spraakinterfaces, maar Lippett zei dat het reservecapaciteit heeft voor klanten om hun eigen systemen te bouwen. Een MIPI-interface is inbegrepen voor camera-invoer.

Xcore-architectuur

De Xcore.ai-chip levert tot 3200 MIPS, 51,2 GMACC's en 1600 MFLOPS. Het heeft 1 Mbyte ingebed SRAM plus een low power DDR-interface voor uitbreiding.

Vergeleken met een Cortex-M7-apparaat dat ongeveer hetzelfde integratieniveau biedt als Xcore.ai, met een vergelijkbare werkfrequentie, schatten de eigen cijfers van XMOS 32x de AI-verwerkingsprestaties en 15x de DSP-prestaties.

"In de wereld van het eindpunt moet het prijs-prestatie zijn, het heeft geen zin om over het een zonder het ander te praten", zei Lippett. "We zijn erg agressief geweest op het gebied van prijs, we kunnen voor dit deel [in volume] $ 1 krijgen. Over het algemeen zijn we ongeveer de helft van de kosten [van het vergelijkbare Cortex-M7-apparaat] en we blazen het uit het water in termen van prestaties."

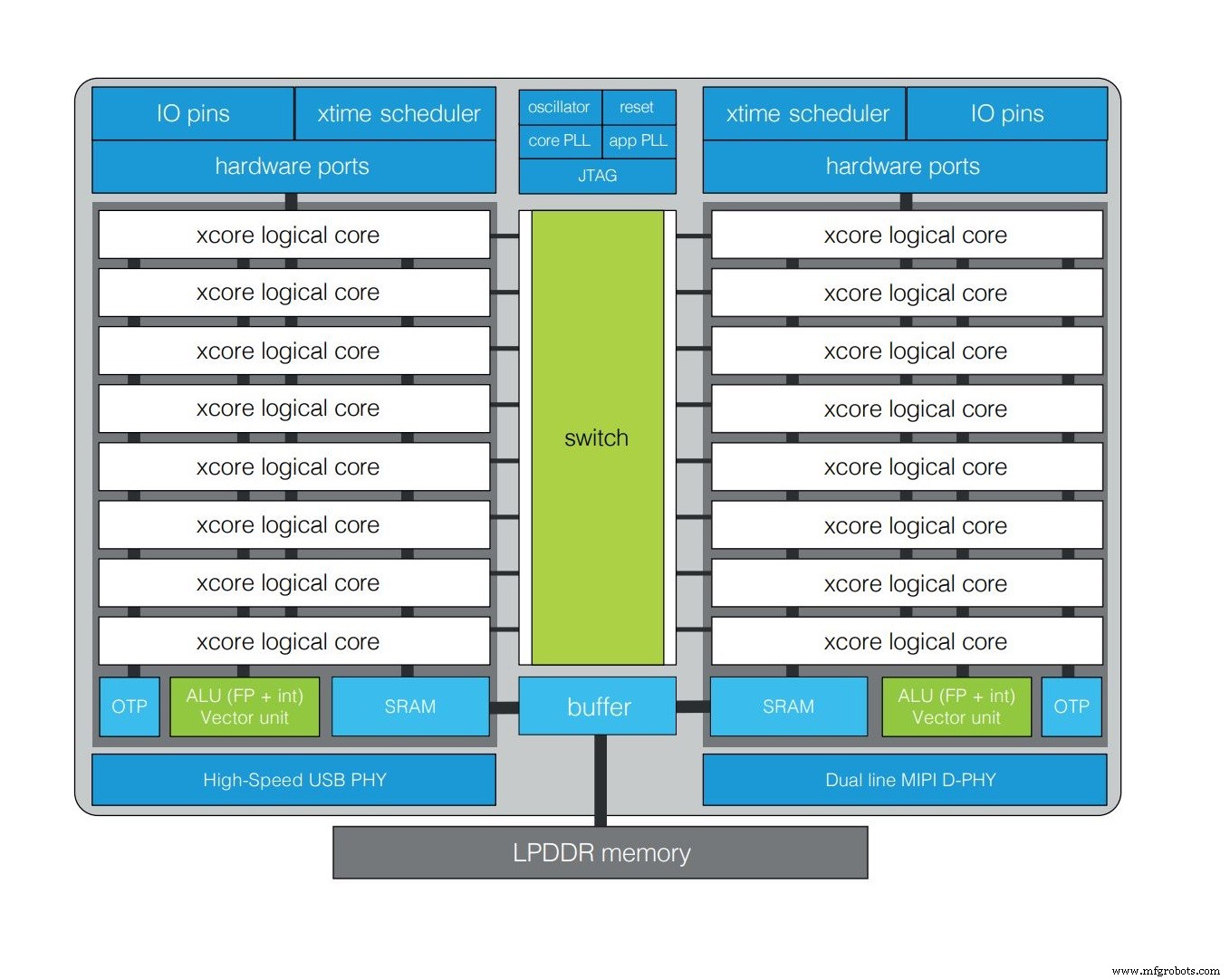

De Xcore is gebaseerd op logische kernen die zijn gerangschikt in tegels met geheugen,

ALU's en vectoreenheden (Afbeelding:XMOS)

Xcore.ai is gebaseerd op de eigen Xcore-architectuur van XMOS. De Xcore zelf is gebouwd op bouwstenen die logische kernen worden genoemd en die kunnen worden gebruikt voor I/O, DSP, besturingsfuncties of AI-versnelling. Er zijn acht logische kernen op elke tegel, met twee tegels in elke Xcore.ai-chip, en ontwerpers kunnen kiezen hoeveel kernen ze aan elke functie willen toewijzen. Elke tegel bevat ook geheugen, ALU's en een vectoreenheid waartoe de logische kernen toegang delen.

"Kritiek is dat ze [toegang delen] op een zeer voorspelbare manier", zei Lippett. “Dit is het bijzondere aan de Xcore. Aanvankelijk wilden we I/O-flexibiliteit leveren aan software-engineers, en hardware is niet erg tolerant als je deadlines mist. Dus de Xcore is multi-core, niet omdat we workloads willen uitbesteden en dingen heel snel willen doen - dat kunnen we doen - maar in werkelijkheid is het multi-core omdat we bepaalde delen van de applicatie hun eigen bronnen willen geven, zodat wanneer het is nodig, het is klaar. Het is van onderaf ontworpen om dat soort timingnauwkeurigheid te leveren."

Door verschillende functies (I/O, DSP, besturing, AI) toe te wijzen aan de logische kernen in firmware, kan een 'virtuele SoC' worden gecreëerd, volledig in software geschreven. In het onderstaande voorbeeld voert één kern taken uit die normaal in hardware zouden worden gedaan, zoals I 2 S, I 2 C- en LED-stuurprogramma's en sommige kernen verwerken het neurale netwerk, terwijl andere taken uitvoeren die normaal in software zouden worden gedaan. Dit alles in software definiëren is sneller, om te voldoen aan de tijdelijke eisen van IoT-apparaten. Ontwikkeling is ook goedkoper, zei Lippett, waardoor bedrijven oplossingen kunnen creëren die zelfs in kleinere marktsegmenten economisch zijn.

Een voorbeeldtoepassing die is toegewezen aan een Xcore.ai-apparaat (Afbeelding:XMOS)

"De manier waarop we de markt zien evolueren, is dat de markt meer diverse functies eist en dat bedrijven sneller moeten reageren", zei Lippett. “Het is erg moeilijk om voor twee jaar te wedden op het IoT zonder een heel generiek platform te bouwen dat [uiteindelijk] voor geen enkel segment goed genoeg is. [Met de Xcore.ai] is het veel gemakkelijker om apparaten veel sneller op de markt te brengen, met minder kapitaaluitgaven, en om effectief kleinere weddenschappen te plaatsen op kleinere markten en die markten economisch te maken."

Hoe zal XMOS concurreren met de grote makers van microcontrollers die deze crossover-processorruimte betreden?

“Niet door op ARM gebaseerde SoC's te bouwen! Omdat ze dat heel goed doen', zei Lippett. "De enige manier om tegen die jongens te concurreren, is door een architectonisch voordeel te hebben. Dat gaat over de intrinsieke mogelijkheden van de Xcore op het gebied van prestaties, maar ook de flexibiliteit.”

Ingebed

- Renesas benadrukt endpoint intelligence op embedded world 2019

- MCU's richten zich op veilige IoT-eindpunten en edge-ontwerpen

- Vooraf gecertificeerde draadloze processormodules met Bluetooth mesh-connectiviteit

- Het gebruik van meerdere inferentie-chips vereist een zorgvuldige planning

- PMIC vereenvoudigt multi-rail processorontwerpen

- Kleine haptische IC ondersteunt low-power wearables

- Multicore-processor integreert neurale verwerkingseenheid

- 60-GHz radar-op-chip ondersteunt de vereisten van de auto-industrie

- Energiebeheer-IC ondersteunt toepassingsprocessorfamilie

- Gespecialiseerde processors versnellen eindpunt AI-workloads

- 30 fps automotive imaging radarprocessor debuteert