Asynchrone reset-synchronisatie en distributie - ASIC's en FPGA's

Gebrek aan coördinatie tussen asynchrone resets en synchrone logische klokken leidt tot intermitterende storingen bij het opstarten. In deze serie artikelen bespreken we de vereisten en uitdagingen van asynchrone reset en verkennen we geavanceerde oplossingen voor ASIC versus FPGA-ontwerpen.

Asynchrone resets worden traditioneel gebruikt in VLSI-ontwerpen om synchrone schakelingen in een bekende staat te brengen na het opstarten. Asynchrone reset-vrijgavebewerking moet worden gecoördineerd met het synchrone logische kloksignaal om synchronisatiefouten als gevolg van mogelijke conflicten tussen de reset en de klok te elimineren. Een gebrek aan een dergelijke coördinatie leidt tot intermitterende storingen bij het opstarten. Het probleem verergert wanneer grote domeinontwerpen met meerdere klokken worden overwogen. Naast de synchronisatieproblemen, is de distributie van een asynchrone reset naar miljoenen flip-flops een uitdaging, waarvoor technieken nodig zijn die vergelijkbaar zijn met CTS (Clock Tree Synthesis) en waarvoor vergelijkbare oppervlakte- en routeringsbronnen nodig zijn.

De vereisten en uitdagingen van asynchrone reset worden beoordeeld, met de nadruk op synchronisatie- en distributieproblemen. De nadelen van klassieke oplossingen voor reset-synchronisatie (reset tree source-synchronisatie) en distributie (reset tree-synthese) worden besproken. Geavanceerde oplossingen voor snellere en eenvoudigere timingconvergentie en betrouwbaardere resetsynchronisatie en distributie worden gepresenteerd. Verschillende benaderingen voor ASIC- versus FPGA-ontwerpen worden gedetailleerd.

Deel 1 beschrijft de problemen rond asynchrone resets en schetst benaderingen om deze problemen op te lossen. Deel 2 (dit artikel) bespreekt aanvullende oplossingen voor een correcte asynchrone reset in ASIC en FPGA. Enkele nuttige speciale gevallen worden besproken in deel 3.

Een van de belangrijkste problemen die in deel 1 werden besproken, was de complexiteit van reset-release voor grote ontwerpen (met een resetdistributienetwerk met hoge latentie), vooral wanneer een korte klokcyclus wordt gebruikt. De timingconvergentie op basis van standaard STA-optimalisatie leidt tot een duur ontwerp en is in sommige gevallen zelfs onmogelijk. Hier bespreken we twee technieken die dit timingprobleem verminderen. Beide technieken zijn toepasbaar voor ASIC- en voor FPGA-ontwerpen.

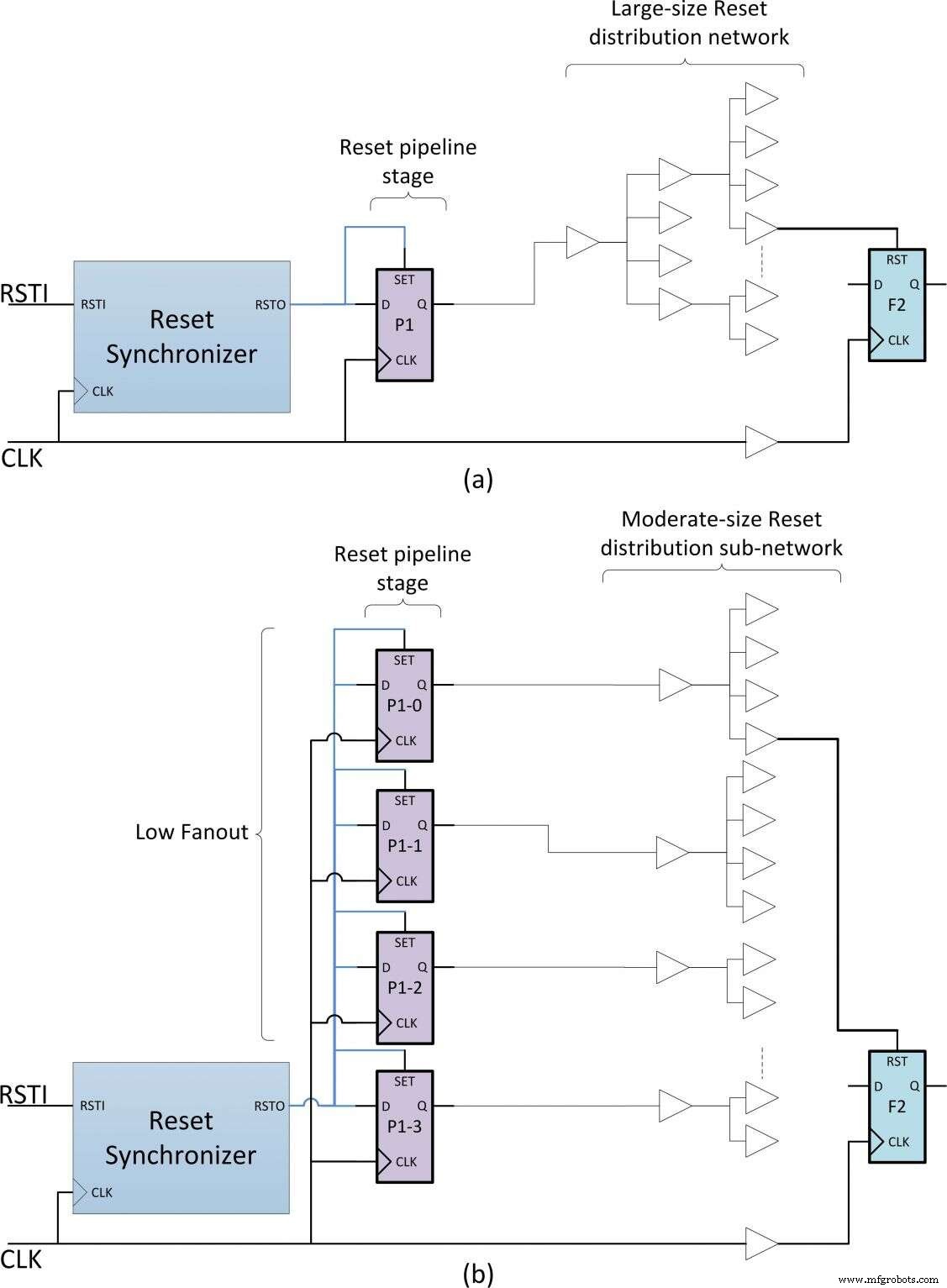

Een manier om het timingprobleem van asynchrone reset-release aan te pakken, is door de reset-release-latentie in te ruilen voor een meer ontspannen timing. Dit kan worden bereikt door de reset-boom op de volgende manier te pipelinen. Na elke synchronisator wordt een extra asynchrone set-flip-flop-trap P1 op de reset-lijn opgenomen (Figuur 6a). Zowel de SET- als de D-ingangen van de flip-flop zijn verbonden met de actieve high-reset RSTO die afkomstig is van de reset-synchronizer. Bij de RSTO-release is voldaan aan de setup- en hold-voorwaarden voor P1 D- en SET-ingangen, aangezien deze zijn beperkt als reguliere synchrone paden.

klik voor grotere afbeelding

Figuur 6:Asynchrone reset met pipelining (Bron:vSync Circuits)

De functionele werking van het nieuwe schema is vergelijkbaar met het reguliere schema beschreven in deel 1 (Figuur 3d), behalve een extra latentie van een enkele cyclus bij de reset-release. De hogere reset-latentie die deze techniek met zich meebrengt, is meestal acceptabel voor de meeste toepassingen, aangezien deze slechts één keer per keer opstarten optreedt.

Een aanvullend onderdeel van deze techniek omvat ontwerpbeperkingen. Terwijl de synchronisator-flip-flops moeten worden beperkt tegen duplicatie om problemen met het herconvergentiepad te voorkomen, zoals beschreven in deel 1, is de pijplijntrap P1 onderhevig aan MAX_FANOUT-beperking. Een voorbeeld van maximale fanout-beperking wordt getoond in figuur 6b. De P1 flip-flop is automatisch gedupliceerd door synthesetool, waardoor vier subnetwerken worden gecreëerd voor de resetdistributie. Elk subnetwerk heeft een lagere latentie dan het oorspronkelijke netwerk en voldoet aan de timingvereiste voor de reset-release. Bovendien voldoet de output van de reset-synchronisator gemakkelijk aan fanout van acht.

Deze asynchrone reset-pipeliningtechniek is schaalbaar voor elke ontwerpgrootte en vereist geen wijzigingen wanneer het ontwerp verandert, omdat de synthesetool automatisch de P1-fase dupliceert, waardoor het reset-subnet met matige latentie begrensd blijft. De gedupliceerde fanout van de P1-trap voor de uitvoer van de synchronisator is meestal klein en veroorzaakt geen timingovertredingen. Wanneer een enkele pijplijnfase echter niet leidt tot timingconvergentie, kunnen aanvullende pijplijnfasen P2 - PN worden opgenomen en beperkt met verschillende MAX_FANOUT-beperkingen.

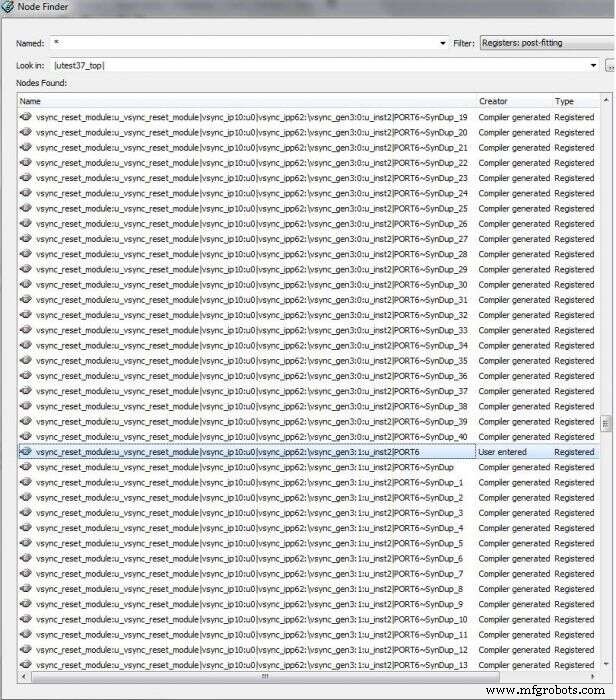

Een voorbeeld van deze techniek toegepast op een echt ontwerp wordt getoond in figuur 7. Het P1-trapregister, genaamd PORT6, werd automatisch ongeveer 40 keer gedupliceerd door de synthesetool [6] om te voldoen aan de MAX_FANOUT-beperking. Elk van de 40 subnetten voldeed aan de timing voor zijn lokale fanout.

klik voor grotere afbeelding

Figuur 7:Voorbeeld van asynchrone reset-pipelining (Bron:vSync Circuits)

Ingebed

- Structuren en klassen in C++

- Mailboxen:introductie en basisservices

- Semaphores:introductie en basisdiensten

- Anvo-Systems en Mouser ondertekenen distributieovereenkomst

- Mouser en Inventek Systems kondigen wereldwijde distributieovereenkomst aan

- Rutronik en AP Memory ondertekenen wereldwijde distributieovereenkomst

- Albis Plastics gescheiden distributie en samengestelde bedrijven

- De kunst en wetenschap van het selecteren van distributiesites

- Zes manieren om emissies in magazijnbeheer en distributie te verminderen

- RG Group sluit distributie- en integratiepartnerschap met AutoGuide Mobile Robots

- 20 productieblogs die elke productie-, supply chain-, distributie- en logistiekprofessional zou moeten lezen