Asynchrone resetsynchronisatie en distributie - uitdagingen en oplossingen

Gebrek aan coördinatie tussen asynchrone resets en synchrone logische klokken leidt tot intermitterende storingen bij het opstarten. In deze serie artikelen bespreken we de vereisten en uitdagingen van asynchrone reset en verkennen we geavanceerde oplossingen voor ASIC versus FPGA-ontwerpen.

Asynchrone resets worden traditioneel gebruikt in VLSI-ontwerpen om synchrone schakelingen in een bekende staat te brengen na het opstarten. Asynchrone reset-vrijgavebewerking moet worden gecoördineerd met het synchrone logische kloksignaal om synchronisatiefouten als gevolg van mogelijke conflicten tussen de reset en de klok te elimineren. Een gebrek aan een dergelijke coördinatie leidt tot intermitterende storingen bij het opstarten. Het probleem verergert wanneer grote domeinontwerpen met meerdere klokken worden overwogen. Naast de synchronisatieproblemen is de distributie van een asynchrone reset naar miljoenen flip-flops een uitdaging, waarvoor technieken nodig zijn die vergelijkbaar zijn met CTS (Clock Tree Synthesis) en waarvoor vergelijkbare oppervlakte- en routeringsbronnen nodig zijn.

De vereisten en uitdagingen van asynchrone reset worden beoordeeld, met de nadruk op synchronisatie- en distributieproblemen. De nadelen van klassieke oplossingen voor reset-synchronisatie (reset tree source-synchronisatie) en distributie (reset tree-synthese) worden besproken. Geavanceerde oplossingen voor snellere en eenvoudigere timingconvergentie en betrouwbaardere resetsynchronisatie en distributie worden gepresenteerd. Verschillende benaderingen voor ASIC- versus FPGA-ontwerpen worden gedetailleerd.

Deel 1 (dit artikel) beschrijft de problemen rond asynchrone resets en schetst benaderingen om deze problemen op te lossen. Deel 2 bespreekt aanvullende oplossingen voor een correcte asynchrone reset in ASIC en FPGA. Enkele nuttige speciale gevallen worden besproken in deel 3.

Een resetfunctie is normaal gesproken opgenomen in digitale VLSI-ontwerpen om de logica in een bekende staat te brengen. Resetten is meestal vereist voor de besturingslogica en kan worden geëlimineerd uit de gegevenspadlogica, waardoor het logische gebied wordt verkleind. Reset kan synchroon of asynchroon zijn ten opzichte van het kloksignaal.

Synchrone reset vereist een actieve klok, brengt bepaalde klokcyclus-gerelateerde latentie met zich mee en kan de timing van de datapaden beïnvloeden. Aan de andere kant zijn synchrone resets deterministisch en veroorzaken ze geen metastabiliteit.

Asynchrone reset vereist geen actieve klok om flip-flops in een bekende staat te brengen, heeft een lagere latentie dan een synchrone reset en kan gebruikmaken van speciale flip-flop-ingangspinnen die de datapadtiming niet beïnvloeden. Asynchrone resets hebben echter een aantal nadelen:

Ze kunnen metastabiliteit in flip-flops veroorzaken, wat leidt tot niet-deterministisch gedrag.

Asynchrone resets moeten direct toegankelijk worden gemaakt om DFT in te schakelen.

De asynchrone resets kunnen betrouwbaarheidsproblemen veroorzaken in rad-hard applicaties, omdat ze vatbaar zijn voor Single Event Transient (SET) fenomenen [1].

Afgezien van de discussie over welk type reset beter is [2], concentreren we ons in dit artikel op problemen en oplossingen met betrekking tot asynchrone resets. Sommige van de technieken die in dit artikel worden gepresenteerd, zijn van toepassing op zowel asynchrone als synchrone resets.

Asynchrone resets worden veel gebruikt in digitale ontwerpen. De typische drivers van asynchrone resets zijn externe poorten, afhankelijk van de voedingsstatus (RC-circuits, watchdog-apparaten), handmatige resetknoppen en externe masters, zoals microprocessors.

In veel gevallen kunnen asynchrone resets worden vervangen door synchrone, maar er zijn situaties waarin de asynchrone reset-functionaliteit verplicht is. Een voorbeeld is een synchroon ontwerp dat geen actieve klok krijgt bij het opstarten (de klok is ofwel onstabiel of gepoort voor stroomreductie), maar vereist een bepaalde bekende status voor zijn externe interfaces. Een ander voorbeeld is een ontwerp met laag energieverbruik dat vereist is om het vermogen tijdens het opstarten te minimaliseren, zonder actieve klokken.

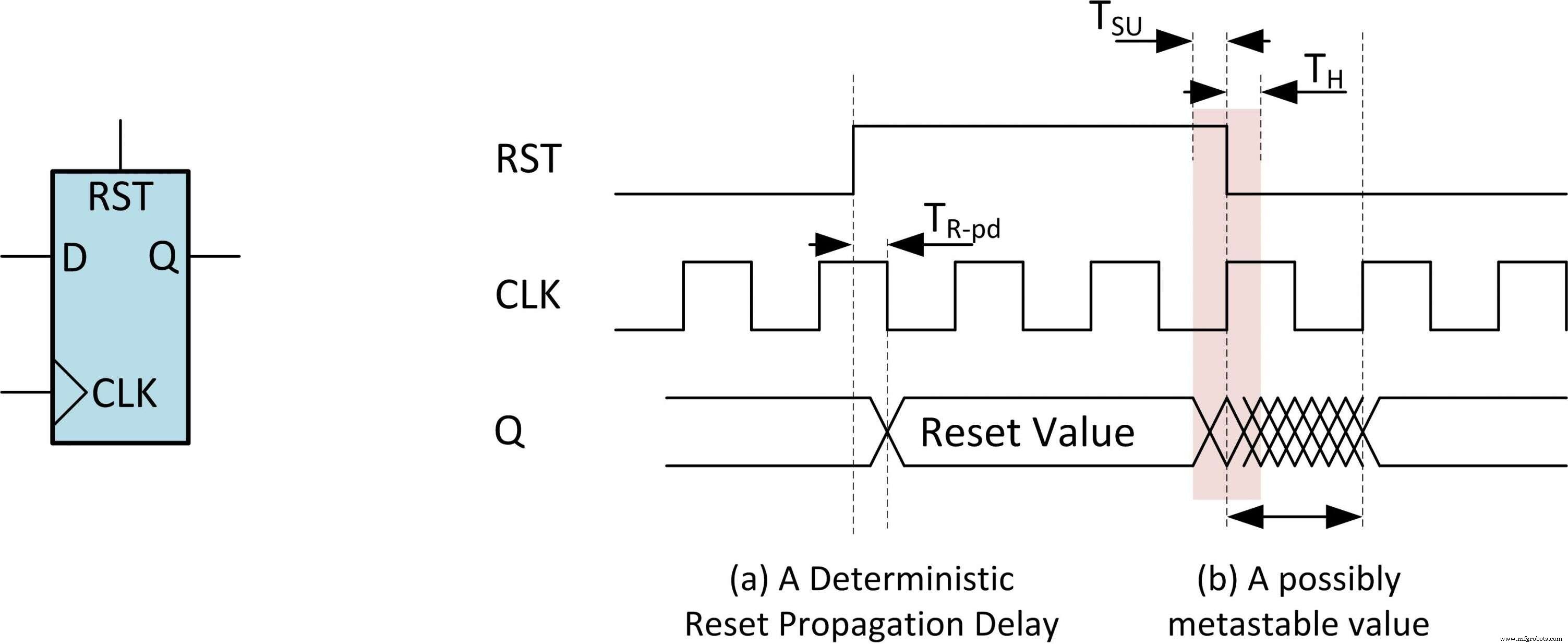

Het gebruik van asynchrone reset is niet eenvoudig. Hoewel de relatieve timing tussen klok en reset kan worden genegeerd tijdens resetbevestiging, moet de reset-release worden gesynchroniseerd met de klok. Het vermijden van de synchronisatie van de reset-releaserand kan leiden tot metastabiliteit. Verwijzend naar figuur 1 wordt een actieve hoge asynchrone reset getoond. De reset-bewering (a) beïnvloedt de flip-flop-uitgang Q binnen een deterministisch begrensde tijd (voortplantingsvertraging, TR-pd ) en ongeacht het kloksignaal CLK. Tijdens reset-release (b) moet worden voldaan aan de voorwaarden voor setup en hold-timing voor de RST-poort ten opzichte van de klokpoort CLK. Een schending van de setup- en hold-voorwaarden voor de RST-poort (ook bekend als reset-herstel- en verwijderingstijdstip) kan ertoe leiden dat de flip-flop metastabiel wordt, waardoor het ontwerp mislukt als gevolg van het overschakelen naar een onbekende status. Merk op dat deze situatie vergelijkbaar is met de schending van de setup- en hold-voorwaarden voor de flip-flop datapoort, D.

klik voor grotere afbeelding

Figuur 1:Actieve hoge asynchrone reset-bevestiging en release. (a) Een asynchrone reset-bewering (b) Een asynchrone reset-release met timingovertreding. (Bron:vSync Circuits)

Ingebed

- Over-the-air updates:vijf typische uitdagingen en oplossingen

- Belangrijkste PCB-trends en -uitdagingen

- Anvo-Systems en Mouser ondertekenen distributieovereenkomst

- Swissbit:op hardware gebaseerde beveiligingsoplossingen om gegevens en apparaten te beschermen

- Rutronik en AP Memory ondertekenen wereldwijde distributieovereenkomst

- IIoT-trends en uitdagingen om te bekijken

- Prestatiebewaking:uitdagingen, oplossingen en voordelen

- Industriële IoT-beveiliging:uitdagingen en oplossingen

- Uitdagingen in de automobielindustrie en IoT-oplossingen

- Top 5 logistieke uitdagingen en oplossingen voor de maakindustrie

- Uitdagingen bij het ontwerpen van high-speed PCB's voor signaalintegriteit en hun oplossingen