CPU plus FPGA-ontwerpstroom voor softwareontwikkelaars:een nieuwe tastbare realiteit

Onlangs organiseerde Brian Bailey een rondetafelgesprek dat resulteerde in een tweedelig artikel genaamd Supporting CPUs Plus FPGAs . De experts bespraken de veranderende realiteit van systeemontwerp op basis van FPGA's en CPU's. Deze discussie gaat in op recente ontwikkelingen in ontwerpstroom en hoe het gebruik van nieuwe technologie softwareontwikkelaars kan helpen bij het bereiken van een snellere time-to-market voor CPU plus FPGA-platforms.

Inleiding

Als we kijken naar de groeiende belangstelling voor kunstmatige intelligentie (AI), de opkomst van verbonden objecten (IoT) en de trend van datacenterversnelling, vragen we ons allemaal af:wat is de gemeenschappelijke noemer tussen de drie?

Softwareontwikkelaars staan centraal in al deze trends en ze willen hun programmering en berekeningen versnellen. De nieuwste technologische doorbraken, waaronder lage communicatielatentie tussen FPGA's en CPU's, in combinatie met het relatief lage stroomverbruik van de huidige FPGA's, maken FPGA- en CPU-gebaseerde systemen de juiste keuze om de gewenste prestaties te bereiken. In het centrum van deze convergentie worden softwareontwikkelaars echter gehinderd door de onderliggende complexiteit van FPGA-technologie.

De afgelopen jaren zijn de High Level Synthesis (HLS)-tools sterk verbeterd om de huidige systeemcomplexiteit aan te pakken en de time-to-market te verkorten. HLS-tools richten zich echter vooral op IP-blokkades (d.w.z. ze zijn IP-centrisch). Er is een breed scala aan beslissingen/optimalisaties op systeemniveau die niet kunnen worden ondersteund door HLS-tools om aan de vereisten te voldoen. Enkele van deze vereisten zijn het vinden van de juiste balans tussen softwaretaken en hardwareversnellers, het vergelijken van pijplijn- versus parallelle uitvoering, het bereiken van de gewenste gegevensgranulariteit, het beoordelen van communicatiemechanismen en nog veel meer.

Om deze complexe systemen te bouwen, hebben softwareontwikkelaars een ontwerpstroom nodig die zowel hardware als software gezamenlijk ondersteunt. Zo'n stroom moet eenvoudig genoeg zijn om het gebruik (zoals de stroom voor softwareontwikkelaars) en acceptatie door softwareontwikkelaars te rechtvaardigen. De stroom moet ook inzichtelijke feedback geven over de beschikbare optimalisatiekeuzes om de vereiste prestatiedoelen te bereiken. Sommige bedrijven hebben onlangs de weg vrijgemaakt om de taak voor softwareontwikkelaars te vergemakkelijken door de technologische details van de hardware-ontwerpstroom te abstraheren. Deze bedrijven zijn geïnspireerd door de ontwerpbenaderingen op systeemniveau die worden beschreven in ESL-modellen en hun toepassing:elektronisch ontwerp en verificatie op systeemniveau in de praktijk .

De ontwerpstroommethode op systeemniveau begrijpen

Ontwerpen op systeemniveau is gericht op zorgen op een hoger abstractieniveau. Hoewel het nodig is om je op het grotere geheel te concentreren, worden verschillende abstractieniveaus gebruikt om verschillende delen van het systeem te valideren, verifiëren, verfijnen en integreren voordat het daadwerkelijk wordt ontwikkeld. Hoewel de technische gemeenschap het niet eens is over een gemeenschappelijke taal om te gebruiken, begint de meerderheid van de ontwerpingenieurs op het algoritmische niveau. Ontwerpers valideren niet-functionele en functionele systeemspecificaties door uitvoeringsmodellen te maken die zijn geschreven in C/C++/SystemC-, MATLAB-, Simulink- en LabVIEW-omgevingen. Deze talen op hoog niveau worden gebruikt om het gedrag van het hele systeem te modelleren.

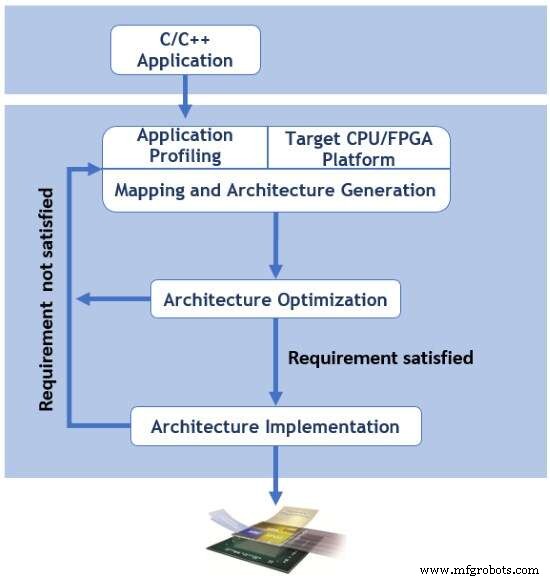

Voor deze discussie hebben we ons gericht op een ontwerpstroom op systeemniveau op basis van C/C++-specificaties (Afbeelding 1). Het eerste blok is opgedeeld in drie stappen. De eerste van deze stappen vertegenwoordigt toepassingsprofilering (d.w.z. hardware-software-partitionering) waarbij wordt aangenomen dat stukjes C/C++-code (functies, lussen, enz.) naar de hardware (FPGA) worden verplaatst. De volgende stap is de specificatie van het CPU/FPGA-platform (bijv. ARM53/FPGA, POWER8/FPGA) en de configuratie van de hardwareplatformelementen (systeemklok, processorcache, onderlinge verbindingen, enz.). De volgende stap is het in kaart brengen van de applicatietaken (op basis van de geprofileerde applicatie) tussen hardware en software (d.w.z. harde en/of zachte CPU) en - helemaal aan het einde - het genereren van een uitvoerbare architectuur.

Figuur 1. Typische ontwerpstroom op systeemniveau voor CPU/FPGA

(Bron:Space Codesign Systems, Inc.)

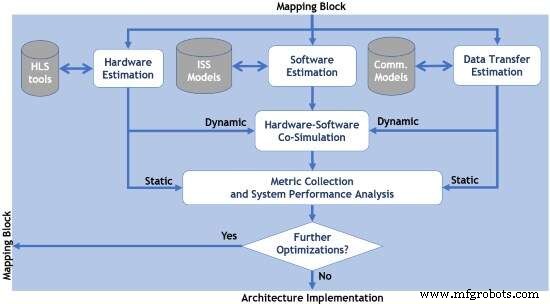

Het tweede blok van figuur 1 omvat architectuuroptimalisatie (ook bekend als architecturale verkenning of prestatieverificatie). Dit wordt in meer detail weergegeven in figuur 2.

Figuur 2. Het architectuuroptimalisatieproces

(Bron:Space Codesign Systems, Inc.)

Het architectuuroptimalisatieproces richt zich op de volgende schatters:

- Hardwareschatting beoordeelt metrische gegevens over hardware-partitionering (d.w.z. C/C++-code verplaatst op de FPGA). Het kan worden uitgesplitst naar bronnen, prestaties (bijvoorbeeld luslatentie) en vermogensschattingen. De schatting van hardware wordt aangestuurd door HLS-tools (High-Level Synthesis).

- Softwareschatting evalueert statistieken voor de C/C++-partitiecode die op de CPU wordt uitgevoerd (d.w.z. harde en/of zachte CPU). Dit proces is complementair aan de stap voor het schatten van hardware. Voorbeelden van prestatiestatistieken zijn processorbelasting, schakelen tussen taken en ontbrekende cache.

- Geschatte gegevensoverdracht bestaat uit het modelleren van de interfaces (d.w.z. memory-mapped en streaming-interfaces) waarmee de hardware en software communiceren. Voorbeelden van verzamelde statistieken zijn busprestaties (bijv. latentie en doorvoer), wachtrij en geheugengebruik.

Deze schattingen worden samengevoegd in een database en een analyse van de systeemprestaties wordt aan de ontwikkelaar gepresenteerd om te beoordelen of aan de vereisten van het systeem wordt voldaan. Architecturen die voldoen aan de eisen gaan door naar het architectuurimplementatieproces; anders worden aanvullende optimalisatiepogingen op systeemniveau verwerkt.

Het laatste blok van figuur 1 heeft betrekking op de architectuurimplementatie waarbij systeemarchitecturen worden geconverteerd naar een bitstream (voor FPGA-implementatie) met behulp van implementatietools zoals Xilinx Vivado of Intel Quartus Prime om de uiteindelijke en volledige systeemgeneratie uit te voeren op het specifieke fysieke platform. Deze stap moet kwaliteitscode opleveren en moet transparant zijn voor de softwareontwikkelaar.

Optimalisatie op systeemniveau

Het ontbreken van geautomatiseerde tools voor architecturale optimalisatie wordt lange tijd gezien als een belangrijke zwakte van op FPGA gebaseerde computing. De ontwikkeling van dergelijke tools was moeilijk vanwege de complexiteit en de uitdagingen.

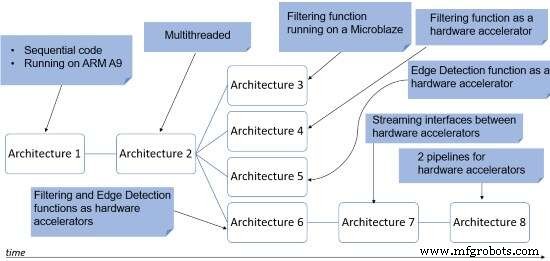

Om deze uitdagingen te illustreren, toont figuur 3 een typisch optimalisatieproces op systeemniveau tijdens een architecturale verkenning voor een beeldverwerkingstoepassing die bestaat uit zes functies (stukken C/C++-code) die moeten worden geïmplementeerd op een Zynq-7000-platform. Hier sommen we acht potentiële architecturen op die op het platform kunnen worden geïmplementeerd. Omdat de time-to-market niet de implementatie van elke architectuur toelaat, moet snel worden bepaald welke architectuur het beste kan worden geïmplementeerd. Deze reeks optimalisaties kan een uitdaging zijn, zelfs voor ervaren hardwareontwerpers.

Figuur 3. Architectuurverkenning met blauw weergegeven beslissingen op systeemniveau

(Bron:Space Codesign Systems, Inc.)

FPGA-softwareontwikkelingstools zoals SDSoC/SDAccel (Xilinx), Merlin Compiler (Falcon Computing Solutions) en SpaceStudio (Space Codesign Systems) zijn commerciële oplossingen die softwareontwikkelaars helpen bij het ontwerpen van FPGA/CPU-systemen en tegelijkertijd optimalisatie op systeemniveau bereiken. Deze tools hanteren een vergelijkbare stroom als beschreven in de figuren 1 en 2, en daarmee demonstreren ze het bestaan van een nieuwe generatie tools op systeemniveau met verschillende benaderingen.

SDSoC schat de systeemprestaties in een benadering in twee stappen. Aanvankelijk schat SDSoC latenties voor de hardwarefuncties (van HLS-tools) en interne karakterisering (d.w.z. gegevensoverdracht) van het beoogde fysieke platform en zijn communicatie-interfaces. Later wordt deze schatting vergeleken met een softwareversie van de applicatie die op het fysieke platform draait.

Merlin Compiler stelt bron-naar-bron transformatie voor. Het doel van bron-naar-brontransformatie is om de ontwerpabstractiekloof tussen software/algoritme-ontwikkeling en bestaande HLS-ontwerpstromen te verkleinen of te elimineren. De Merlin Compiler vertrouwt op vier pragma's om specifieke FPGA-ontwerpen af te leiden. Naast de vier belangrijkste optimalisaties die worden geactiveerd door expliciete pragma's, bevat de Merlin-compiler ook verschillende impliciete optimalisaties (dwz transformatiepassages van de compiler) die samen met de pragma's worden uitgevoerd om de resultaten van de pijplijn en parallellisatie te helpen verbeteren.

SpaceStudio genereert naadloos een uitvoerbaar virtueel platform (VP) voor elke architectuurkandidaat (mapping). Een typische VP bestaat uit processorkernsimulators die zijn aangesloten op verschillende busmodellen, geheugencontrollers en andere datarandapparatuur. Het modelleert het beoogde platform samen met gegevensoverdracht in een co-gesimuleerde omgeving die specifiek is afgestemd op de toepassing. Dit betekent dat de uitvoerbare VP een nauwkeurigere prestatievoorspelling en algoritmevalidatie van de applicatie mogelijk maakt. Het integreert ook monitoring- en analysemogelijkheden voor niet-intrusieve prestatieprofilering van zowel hardwarefuncties als softwaretaken. VP vertrouwt op HLS-tools voor hardwareschatters, terwijl vertragingen (bijv. latenties) van hardwaretoewijzingsfuncties automatisch worden geannoteerd om de nauwkeurigheid van het simulatieproces te vergroten. De VP kan worden geïnspecteerd door de softwareontwikkelaar om te begrijpen hoe de optimalisatietaken worden geïmplementeerd. Dergelijke feedback helpt de softwareontwikkelaar om het beoogde ontwerp voor de specifiek toegepaste optimalisaties te bereiken.

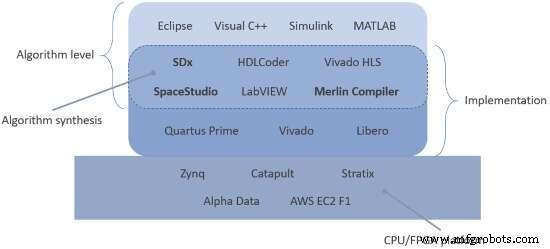

Een manier om het commerciële ecosysteem te bekijken

Afbeelding 4 geeft een beeld van het commerciële ecosysteem dat de wereld van platformgebaseerd ontwerp van CPU's en FPGA's aantrekt. Het eerste (bovenste) vak presenteert de hoofdontwerpinvoer op algoritmeniveau. Het tweede vak bevat omgevingen die algoritmische synthese ondersteunen (d.w.z. van algoritme tot implementatie). De vetgedrukte tools ondersteunen C/C++-ontwerpinvoer en voeren optimalisaties op systeemniveau uit. Het derde vak vertegenwoordigt tools die worden gebruikt om de architecturale implementatie te bereiken, voornamelijk tools van FPGA-leveranciers die de synthese op laag niveau en de bitstream-generatie uitvoeren. Onderaan de afbeelding worden voorbeelden van CPU/FPGA-platforms geïllustreerd.

Figuur 4. Commercieel ecosysteem voor CPU/FPGA-platforms

(Bron:Space Codesign Systems, Inc.)

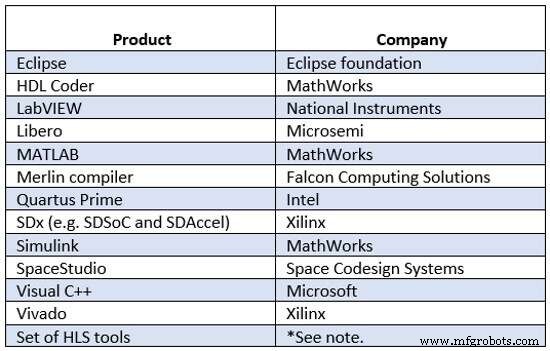

Bovendien somt Tabel 1 enkele van de belangrijkste commerciële tools op die worden gebruikt bij het ontwerpen van CPU/FPGA-platforms.

Tabel 1. Commerciële automatiseringstools (*Opmerking:in deze recensie wordt een lijst voorgesteld)

Conclusie

Het uiteindelijke doel is om de ontwikkeling van CPU plus FPGA-platforms te democratiseren voor een grotere groep gebruikers, zoals de gemeenschap van softwareontwikkelaars. Kijkend naar de analogie van programmeertalen, kostte het de IT-industrie meer dan 50 jaar om programmeertalen te ontwikkelen tot vriendelijke talen zoals Python of, meer recentelijk, Swift. Een soortgelijk evolutieproces vindt plaats in de FPGA-programmeerindustrie. De acceptatie van HLS-tools kostte enige tijd om te worden goedgekeurd door systeemontwerpers. Met de komst van oplossingen op systeemniveau voor softwareontwikkelaars gaan we vandaag een nieuwe fase in. Commerciële tools zoals SpaceStudio, SDSoC en Merlin Compiler getuigen van dit acceptatieproces. Toch moet er nog veel werk worden verzet om een volledig geautomatiseerd en geoptimaliseerd proces te hebben voor alle compilers die zich richten op CPU- en FPGA-platforms.

Guy Bois, Ing., PhD is de oprichter van Space Codesign Systems en hoogleraar aan de afdeling Software en Computer Engineering van Polytechnique Montréal. Guy heeft deelgenomen aan vele R&D-projecten in samenwerking met marktleiders zoals STMicroelectronics, Grass Valley, PMC Sierra, Design Workshops Technologies en Cadabra Systems. Guy's onderzoeksexpertise op het gebied van hardware/software co-design leidde tot de commercialisering van de oplossing en de oprichting van SpaceStudio van Space Codesign Systems Inc.

Ingebed

- Interview met expert:AMendate over zijn geautomatiseerde topologie-optimalisatiesoftware voor 3D-printen

- Expertinterview:Altair's Ravi Kunju over simulatiesoftware voor 3D-printen

- 5 vragen voor Stefan Ferber, de nieuwe CEO van Bosch Software Innovatons

- Project onderzoekt betrouwbare ontwerp- en verificatiestroom voor IoT-beveiliging

- Nieuwe op ML gebaseerde tool biedt geautomatiseerde optimalisatie van de chipontwerpstroom

- FPGA-versneller voor embedded vision MIPI-camera's

- Cadence en UMC werken samen aan certificering van analoge/gemengde signaalstroom voor 28HPC+-proces

- Automatisering:nieuwe hardware en software voor goedkope robots

- Cool IoT-gebruiksscenario's:nieuwe beveiligingsmechanismen voor netwerkauto's

- Omron lanceert nieuwe software voor zijn mobiele robots

- Aanpassen aan een nieuwe realiteit voor productie