Geïntegreerde Logic Analyzer (ILA) en virtuele invoer/uitvoer (VIO) gebruiken

Deze tutorial behandelt het gebruik van de Integrated Logic Analyzer (ILA) en Virtuele invoer/uitvoer (VIO) cores voor het debuggen en bewaken van uw VHDL-ontwerp in de Xilinx Vivado IDE.

In veel gevallen moeten ontwerpers verificatie op de chip uitvoeren. Dat wil zeggen, toegang krijgen tot het gedrag van een intern signaal in hun FPGA-ontwerp voor verificatiedoeleinden.

Een optie is om deze signalen naar de FPGA-pinnen te brengen en ze te verbinden met LED's om hun gedrag visueel te zien. Deze optie is gemakkelijk, snel en werkt goed voor eenvoudige gevallen, maar is niet flexibel, schaalbaar of realistisch.

Een andere optie is om een externe logische analysator te hebben met geavanceerde functies die het gedrag van deze signalen kan weergeven en weergeven, maar hiervoor is externe en relatief dure apparatuur nodig.

De Integrated Logic Analyzer (ILA) is een alternatief dat de voordelen van beide voorgaande opties combineert. Het is gemakkelijk, snel, flexibel en heeft veel geavanceerde functies waarmee ontwerpers snel het gedrag van de gekozen signalen kunnen bekijken en controleren.

Overzicht

Dit artikel bevat meerdere screenshots van de Vivado GUI. Klik op de afbeeldingen om ze groter te maken!

Gebruik de zijbalk om door de omtrek te navigeren voor deze zelfstudie, of scrol omlaag en klik op de pop-upnavigatieknop in de rechterbovenhoek als u een mobiel apparaat gebruikt.

ILA en VIO

De ILA en VIO zijn gratis aanpasbare IP's van Xilinx. Het ILA IP helpt je om gemakkelijk interne signalen in je FPGA te onderzoeken en ze naar een simulatie-achtige omgeving te brengen om ze te monitoren en hun gedrag te verifiëren.

In tegenstelling tot ILA kunt u met de VIO IP virtueel interne signalen in uw FPGA aansturen om uw ontwerp te stimuleren of te controleren, zoals het RESET-signaal.

- Intellectueel eigendom van Xilinx:Integrated Logic Analyzer (ILA)

- Intellectueel eigendom van Xilinx:virtuele invoer/uitvoer (VIO)

Vereisten

- Een Xilinx FPGA-bord

- De Vivado Design Suite

- Basis VHDL-kennis

Ik gebruik de Kintex-7 FPGA KC705 Evaluation Kit, maar de methoden die in deze tutorial worden getoond, zouden op elk modern Xilinx FPGA-bord moeten werken.

Download het voorbeeldproject

U kunt het voorbeeldproject en de VHDL-code downloaden via onderstaand formulier. Het zou moeten werken in Vivado versie 2020.2 of nieuwer.

Pak de zip uit en open de ila_tutorial.xpr bestand in Vivado om het voorbeeldontwerp te bekijken, of lees de rest van dit artikel om het helemaal opnieuw te maken.

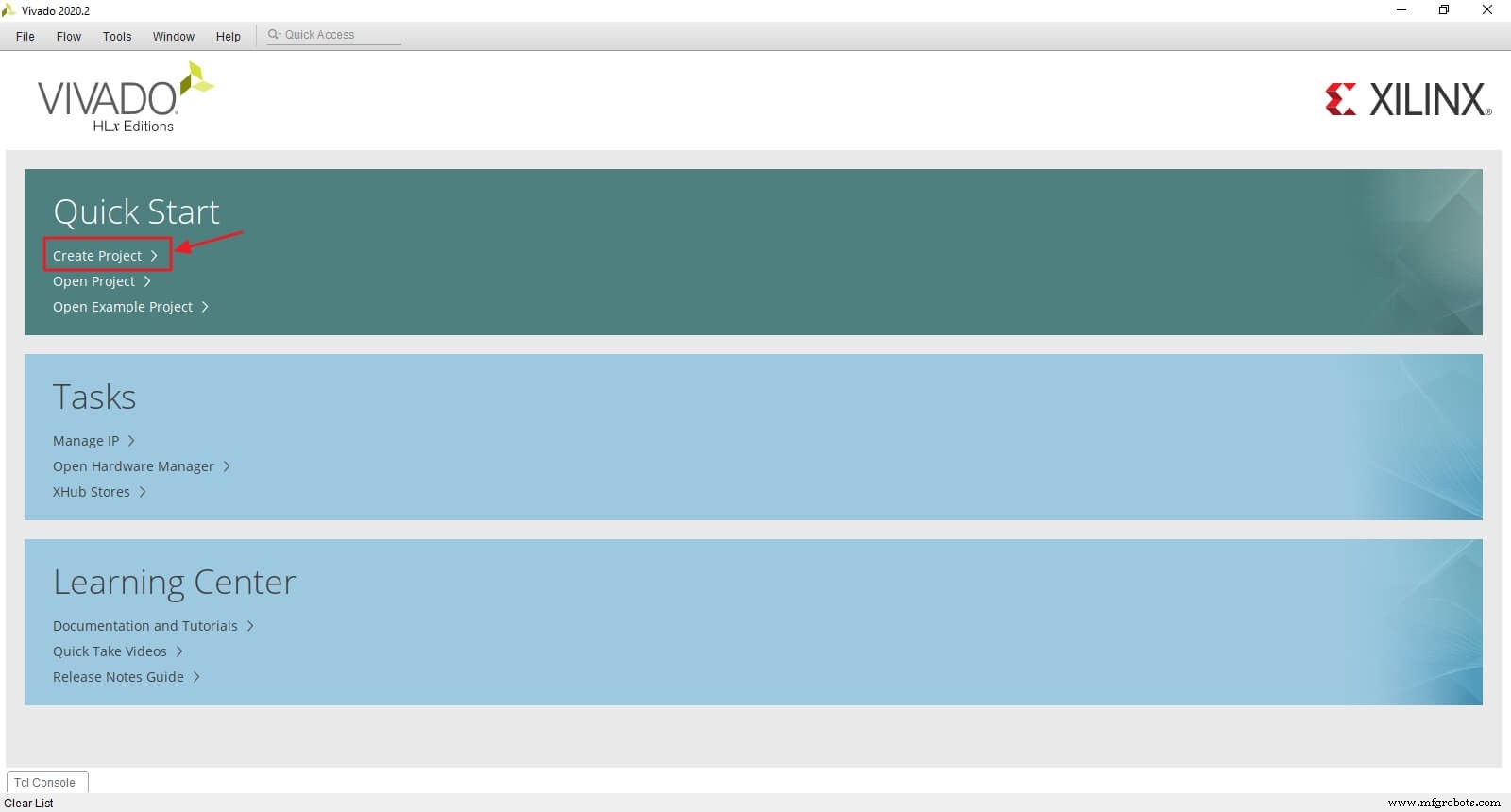

Maak een project met Vivado

Begin met het openen van Vivado. Klik in het welkomstscherm van Vivado op Project maken knop.

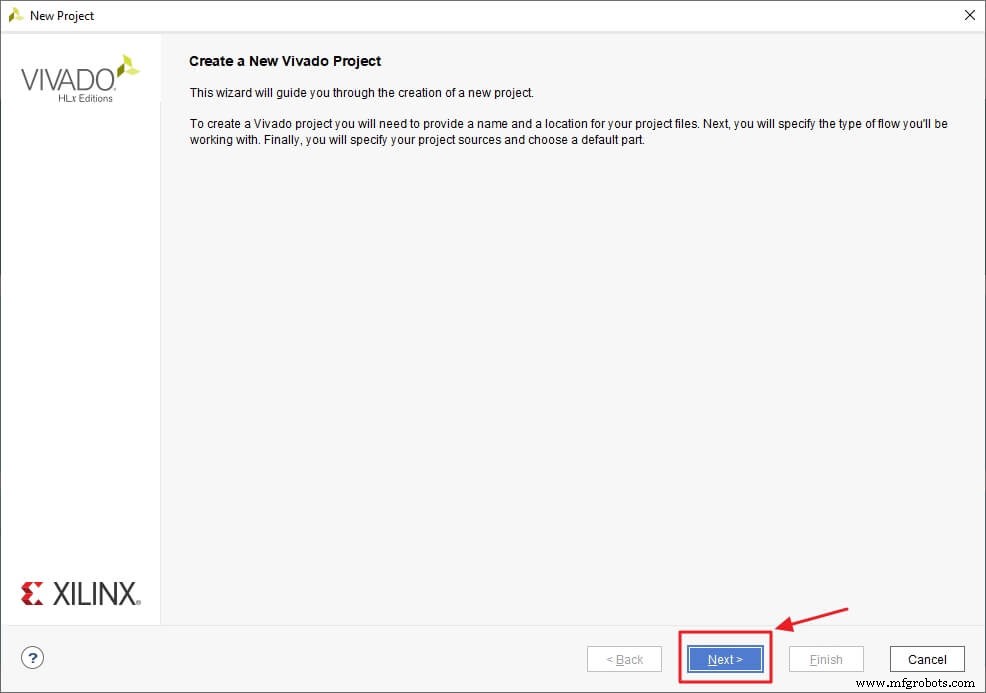

Klik op Volgende om door te gaan.

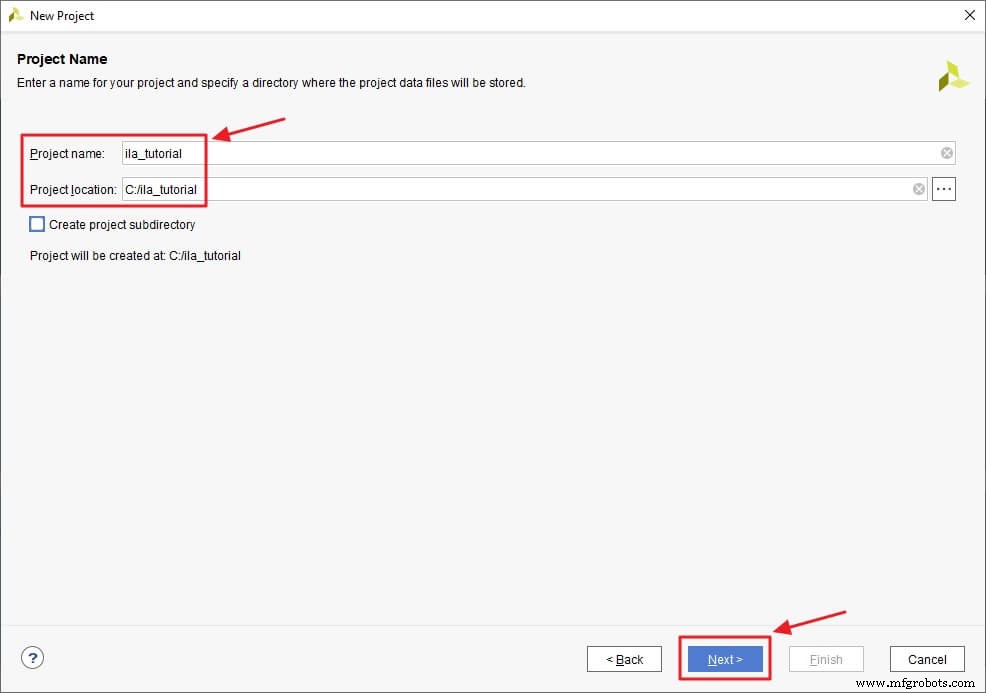

Verander de naam van het project in ila_tutorial en klik op Volgende.

Opmerking: Gebruik geen spaties in de projectnaam. Gebruik in plaats daarvan een onderstrepingsteken of streepje.

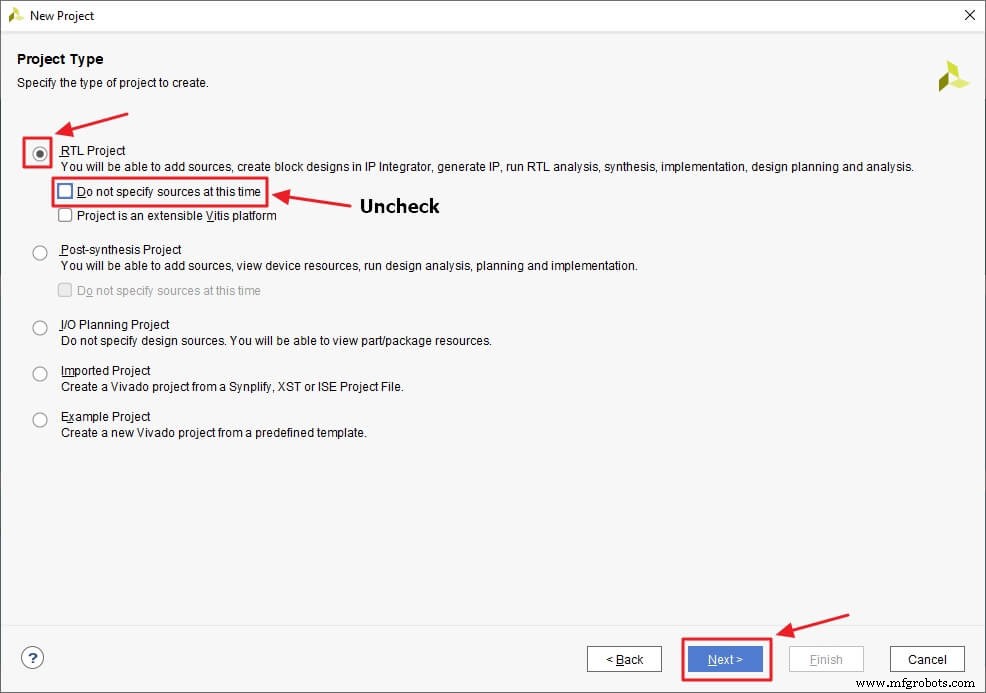

Kies RTL-project en verwijder het vinkje bij Geef op dit moment geen bronnen op en klik op Volgende om door te gaan.

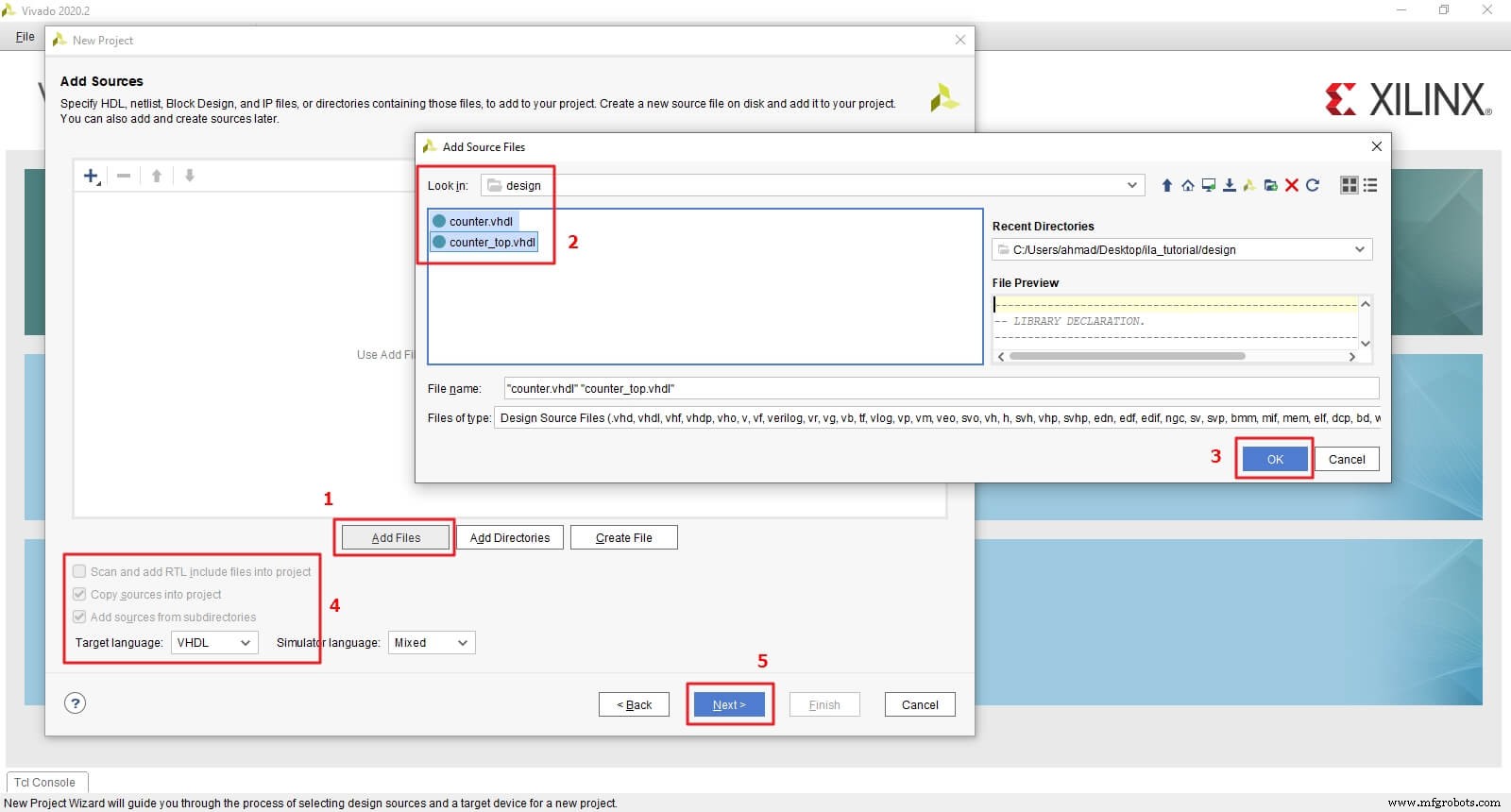

Voeg de bronbestanden toe; teller.vhdl en counter_top.vhdl uit de ontwerpmap. Kies VHDL voor de doeltaal. Vink Bronnen kopiëren naar project . aan en klik op Volgende om door te gaan.

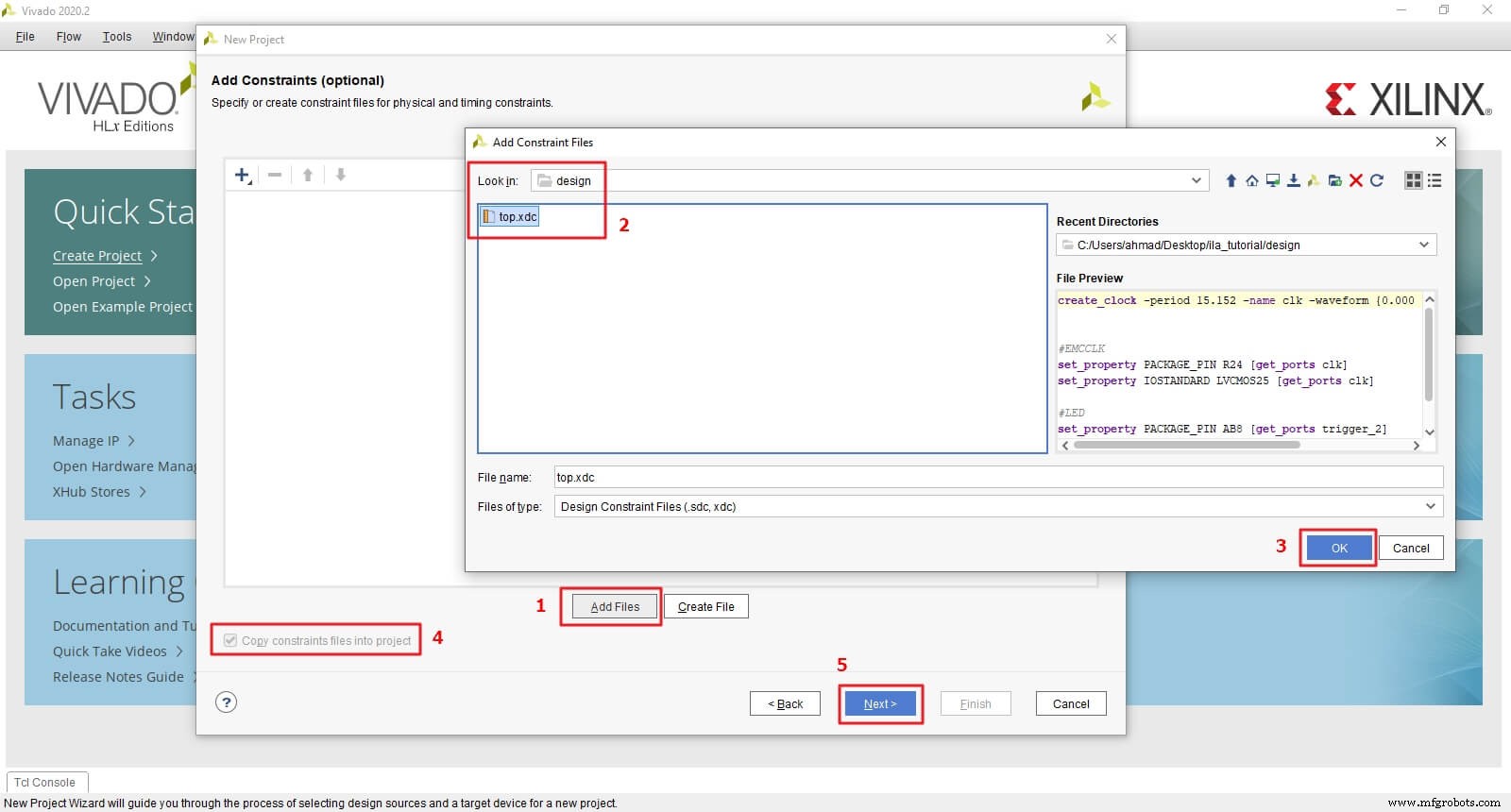

Voeg het beperkingsbestand toe top.xdc uit de ontwerpmap. Vink Beperkte bestanden kopiëren naar project . aan en klik op Volgende om door te gaan.

Opmerking: dit beperkingsbestand is specifiek voor het KC705-bord. U moet de clk-pin . wijzigen en de led-pin volgens je bord. En ook de -periode van je bordklok.

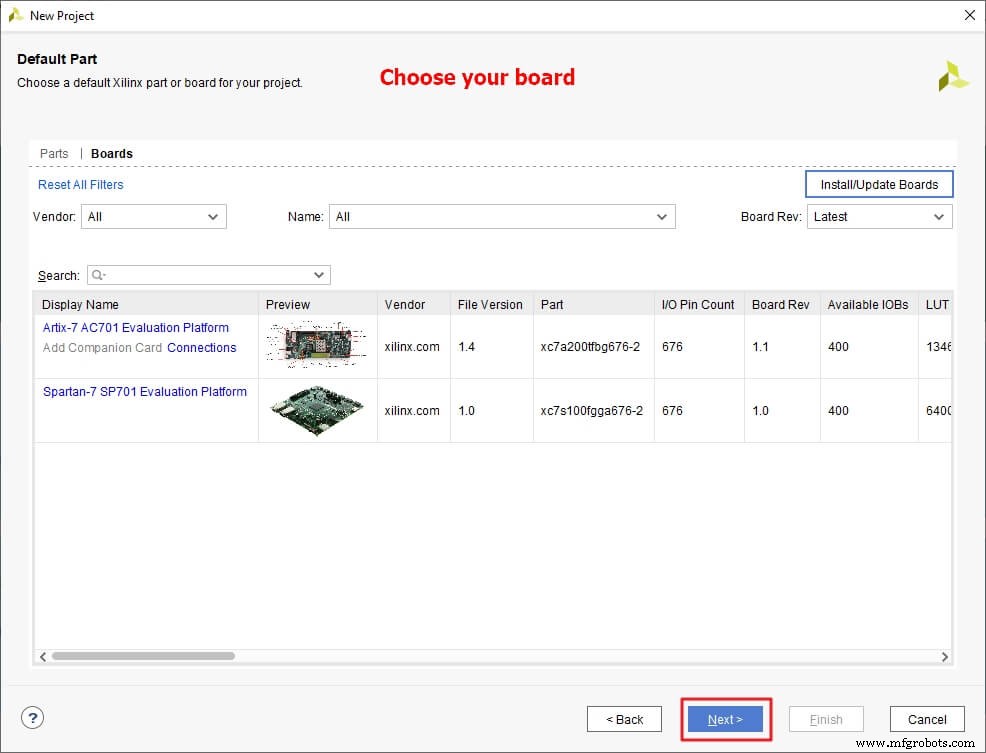

Zoek naar je bord en selecteer het in de lijst. Klik op Volgende om door te gaan.

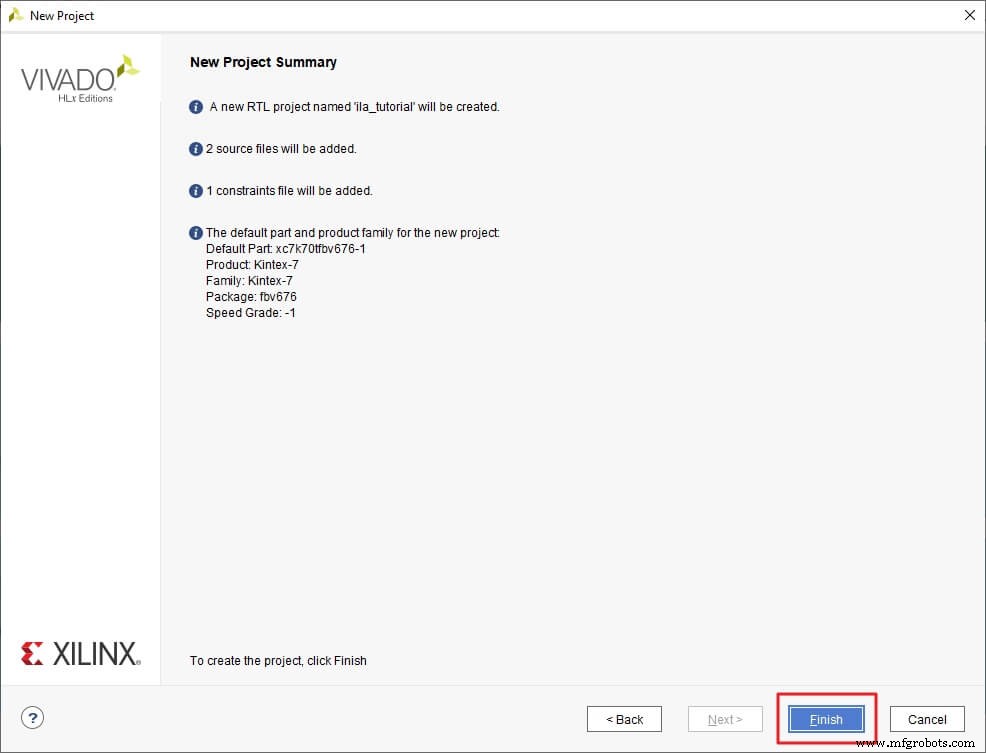

Dit is het laatste scherm van de wizard Nieuw project. Klik op Voltooien om uw project te openen.

De uitleg van het ontwerpvoorbeeld

We zullen een eenvoudig voorbeeld van een ketting met twee tellers gebruiken voor deze tutorial.

De teller.vhdl bestand bevat de RTL-code voor een triviale 4-bits teller die telt van 0 tot 15 indien ingeschakeld. Het bevestigt de 1-bits uitvoer wanneer het aantal tussen 12 en 15 ligt. Voor alle andere waarden blijft de uitvoer lage '0' .

Hier is de entiteitsinterface voor de tellermodule.

----------------------------------------------------------------------------

-- ENTITY DECLARATION.

----------------------------------------------------------------------------

ENTITY counter IS

PORT(clk : IN STD_LOGIC; -- Main clock

reset : IN STD_LOGIC; -- reset, active_high

enable : IN STD_LOGIC; -- enable the next counter

trigger : OUT STD_LOGIC -- trigger the next counter

);

END ENTITY;

Het tellerontwerp heeft twee interne signalen:count en trigger_o .

– tel wordt gebruikt om de telfunctie te implementeren.

– en trigger_o is een tussensignaal voor het aansluiten van de uitgangspoort trigger .

Maak je geen zorgen over ATTRIBUTE , wordt later uitgelegd.

----------------------------------------------------------------------------

-- ARCHITECTURE DECLARATION.

----------------------------------------------------------------------------

ARCHITECTURE rtl OF counter IS

-- INTERNAL SIGNALS DECLARATION --

SIGNAL count : UNSIGNED(3 DOWNTO 0) := (OTHERS => '0');

SIGNAL trigger_o : STD_LOGIC := '0';

-- ATTRIBUTE DECLARATION --

ATTRIBUTE MARK_DEBUG : STRING;

ATTRIBUTE MARK_DEBUG OF count : SIGNAL IS "true";

In de onderstaande lijst zien we de implementatie voor de teller. De seq_proc proces wordt geactiveerd op de stijgende flank van de invoerpoort clk en is in reset-modus wanneer de invoerpoort reset is hoog '1'.

De telling signaal wordt verhoogd wanneer de ingangspoort enable is hoog '1', en de trigger_o signaal is hoog wanneer de waarde van het signaal count is tussen 12 en 15.

seq_proc: PROCESS (reset, clk)

BEGIN -- for seq_proc

IF (reset = '1') THEN

count <= (OTHERS => '0');

trigger_o <= '0';

ELSIF rising_edge(clk) THEN

IF (enable = '1') THEN

count <= count + 1;

IF (count > x"B" AND count <= x"F") THEN

trigger_o <= '1';

ELSE

trigger_o <= '0';

END IF;

END IF;

END IF;

END PROCESS;

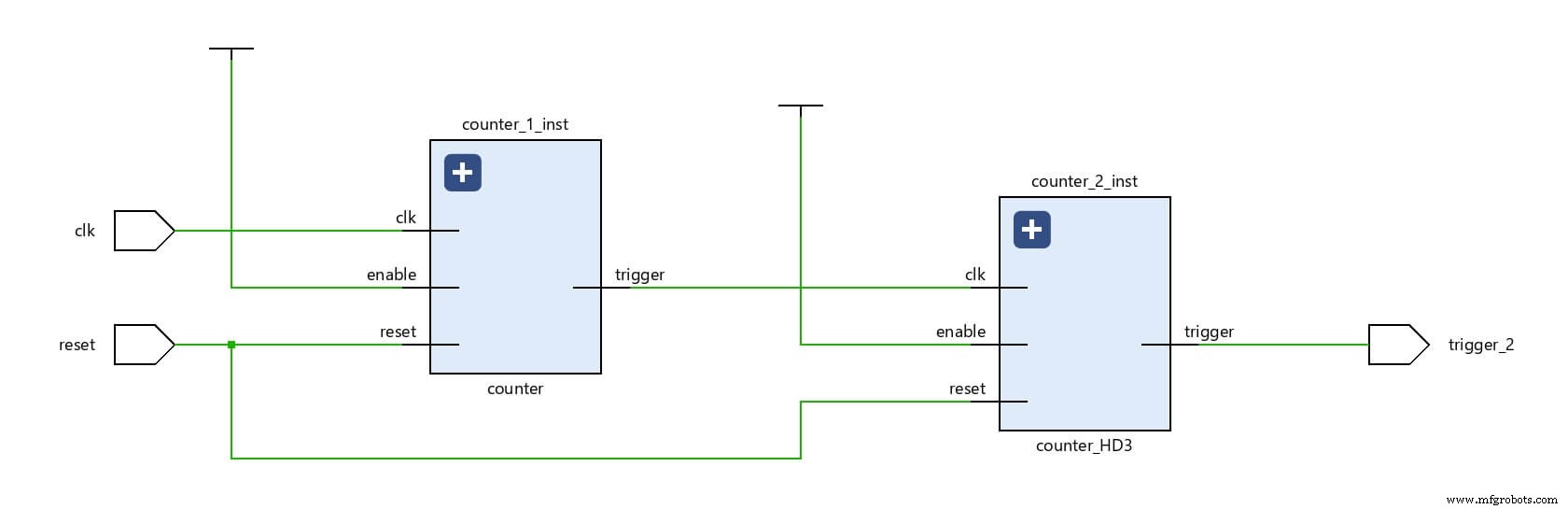

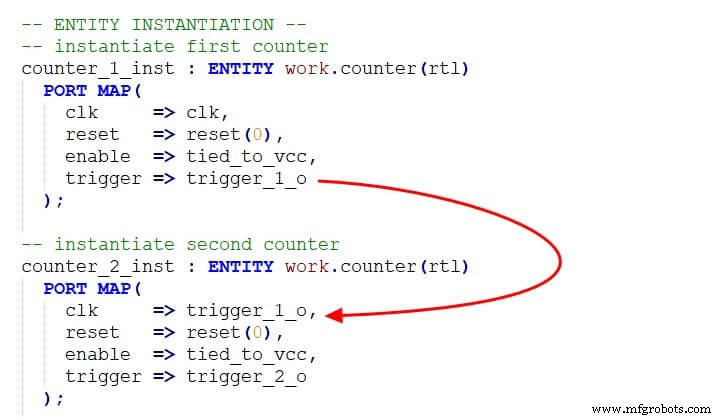

Het bestand counter_top.vhdl bevat twee opeenvolgende tijdstippen van de teller.

– De counter_1_inst is altijd ingeschakeld en klokt de counter_2_inst . Dat wil zeggen, de uitvoerpoort trigger van counter_1_inst is verbonden met de invoerpoort clk van counter_2_inst .

– Het resulterende gedrag is dat counter_1_inst activeert counter_2_inst slechts 4 van de 16 klokcycli. Dus counter_2_inst zal zijn teller vier keer per 16 tellen verhogen.

De VIO-kern maken voor RESET

Nu je het ontwerpvoorbeeld begrijpt, gaan we een VIO maken om de invoerpoort te bedienen reset . Dat geeft ons de mogelijkheid om de reset van Vivado IDE te manipuleren (wisselen), zodat we handmatig kunnen bepalen wanneer de tellers moeten worden gestart/stopt.

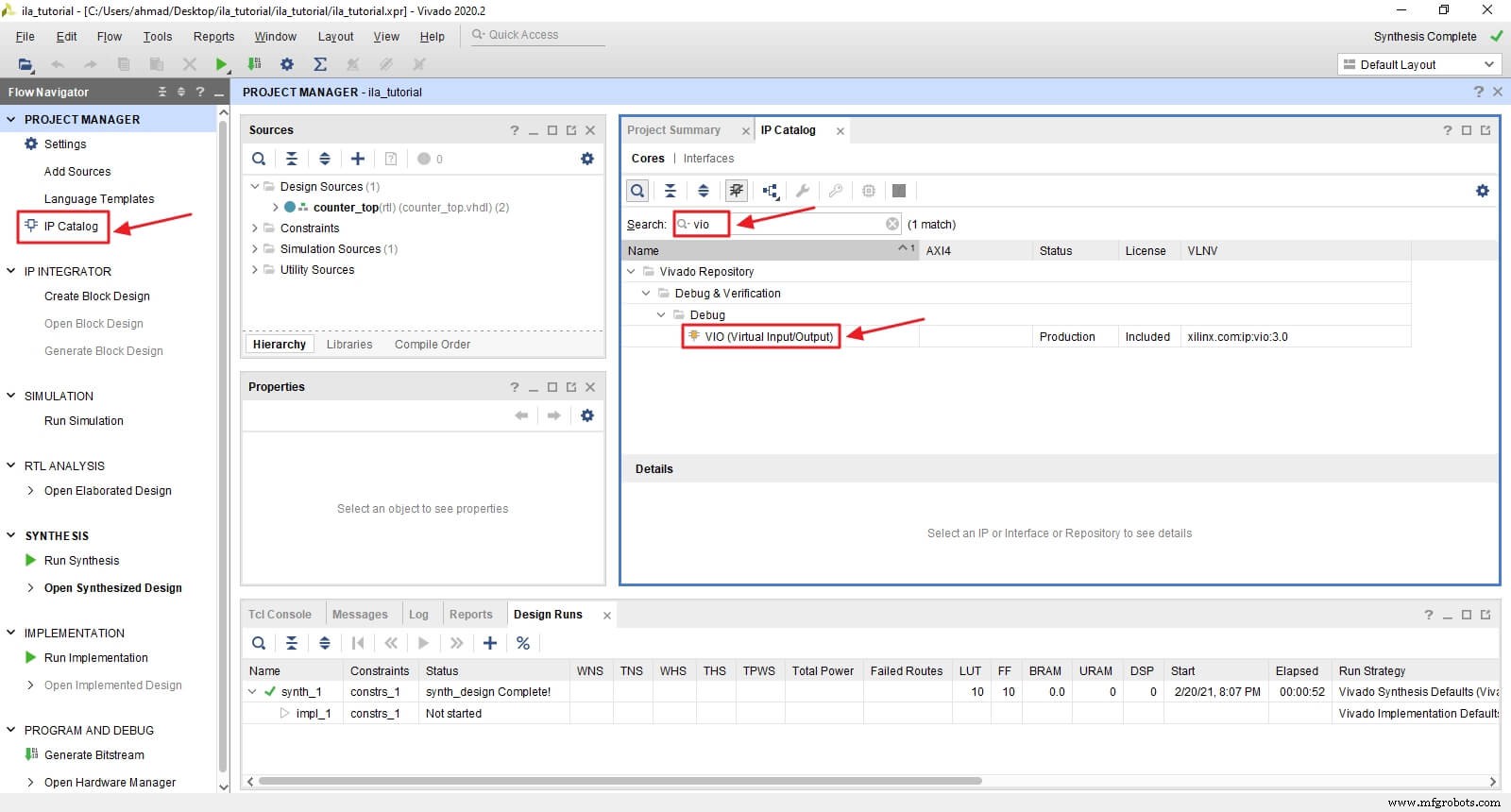

Klik op IP-catalogus en zoek vervolgens naar VIO en dubbelklik vervolgens op VIO (virtuele invoer/uitvoer) .

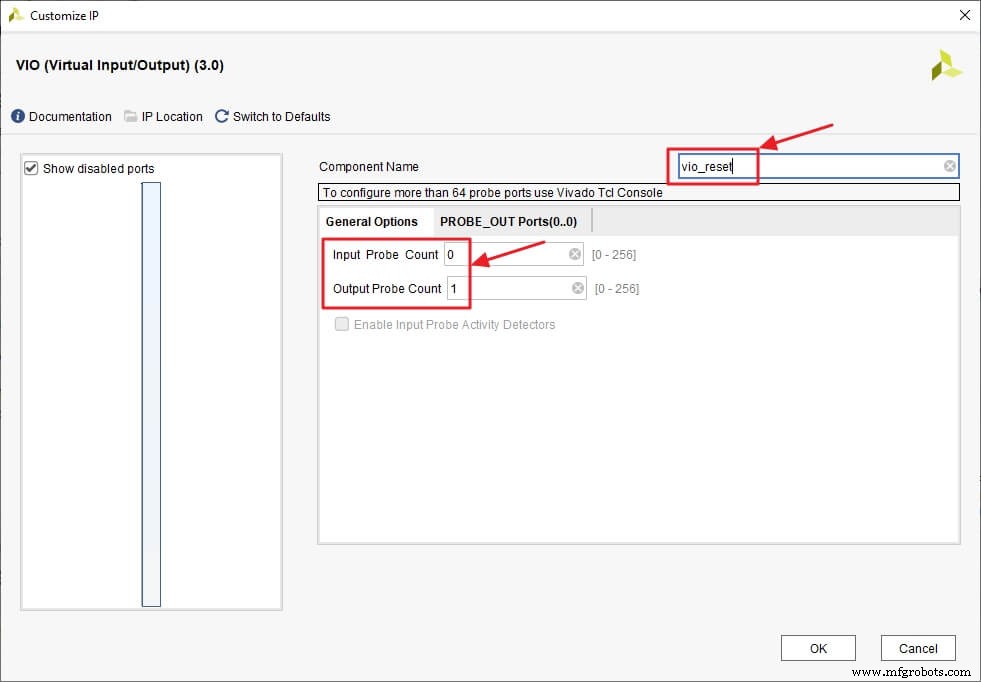

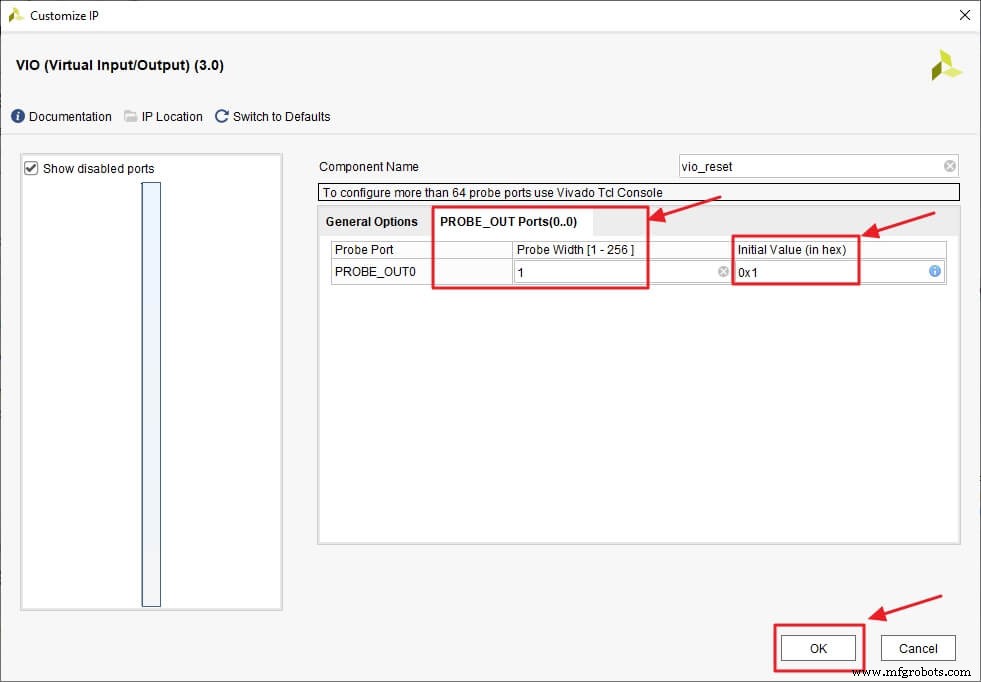

Eerst veranderen we de naam in vio_reset .

Ten tweede hebben we alleen een uitvoerpoort nodig voor de reset, dus we zetten 0 in het invoervak voor het aantal sondes, en we zetten 1 in het veld voor het tellen van de uitvoersonde .

Klik op de PROBE_OUT tabblad poort. Omdat reset een 1-bit-signaal is, plaatsen we 1 in het vak probe_width, en we zetten ook 0x1 in het vak voor beginwaarde dus het begint met een hoge '1'. Klik vervolgens op OK en Genereren . Vivado begint nu met het synthetiseren van de VIO.

Nadat Vivado de synthese van de VIO heeft voltooid, moeten we deze aan ons ontwerp toevoegen door er een component voor te declareren en deze te instantiëren in de counter_top.vhdl bestand zoals hieronder.

Voeg eerst een componentdeclaratie toe voor de vio_reset in de componentdeclaratiesectie in de counter_top.vhdl bestand.

-- Declare vio_reset

COMPONENT vio_reset

PORT(

clk : IN STD_LOGIC;

probe_out0 : OUT STD_LOGIC_VECTOR(0 DOWNTO 0)

);

END COMPONENT;

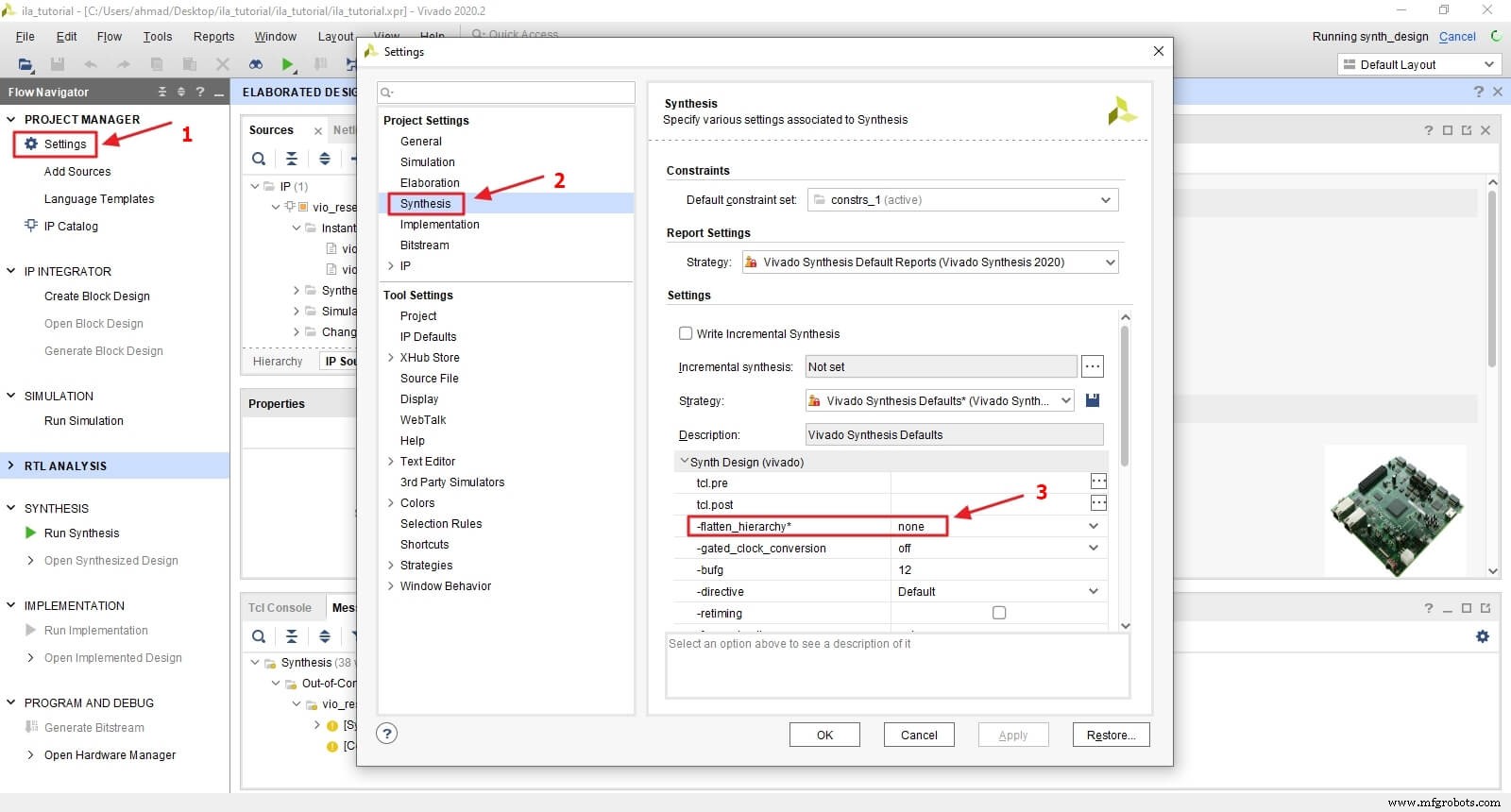

Nu is de VIO voltooid en zijn we klaar om het ontwerp te synthetiseren. Maar daarvoor moeten we de synthese-instelling flatten_hierarchy . wijzigen tot Geen .

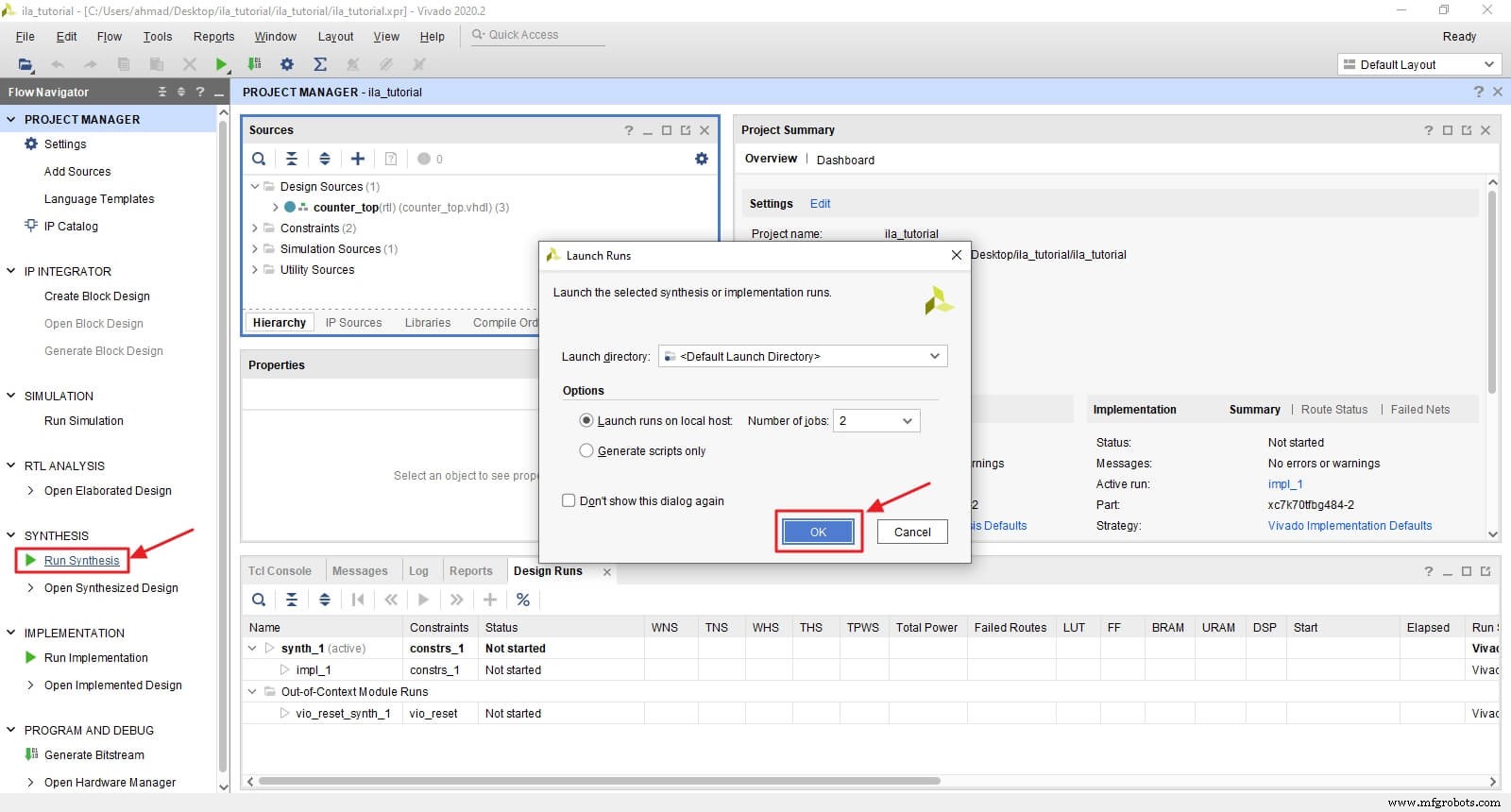

Klik op Synthese uitvoeren en dan op OK .

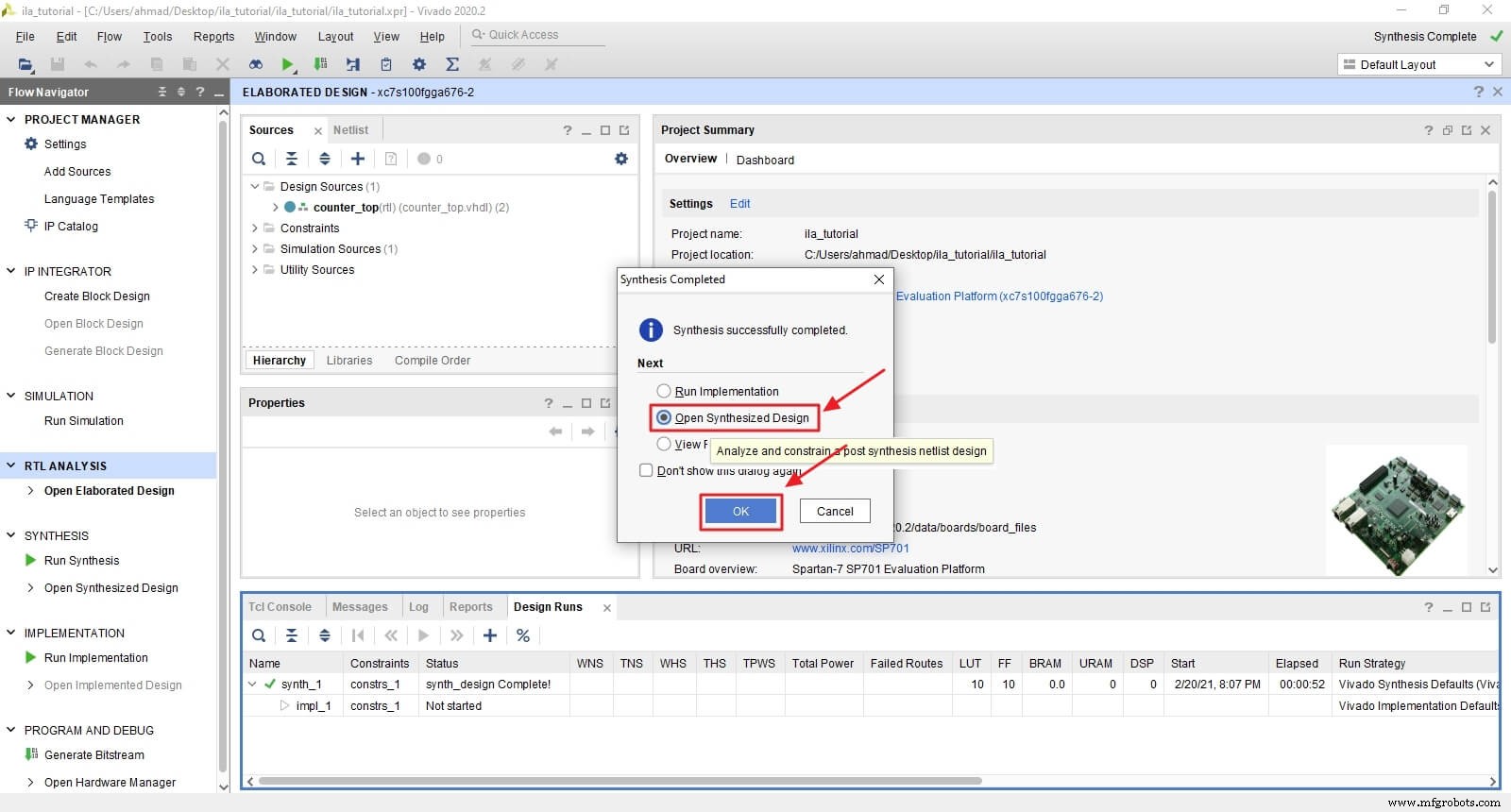

Wanneer Vivado de synthese voltooit, klikt u op Open synthetisch ontwerp .

Wijzig de lay-out in debug door te klikken op Indeling en dan Debuggen .

Debuggen van sondestroom invoegen

Ons gesynthetiseerde ontwerp bevat nu de vio_reset bijvoorbeeld, en het is tijd om de signalen te specificeren die we willen onderzoeken. Er zijn drie manieren om dat te doen:

- Invoegen uit VHDL-bestand

- Invoegen uit de netlijst

- Invoegen uit xdc/tcl-bestand

We gebruiken de eerste twee methoden en laten de derde over voor een latere tutorial.

Invoegen uit VHDL-bestand

Deze methode is de gemakkelijkste en snelste manier om een sonde in te brengen, vooral als het een composiettype is (array of record). Maar het vereist het toevoegen van code aan de ontwerpbestanden, VHDL-code die overbodig is in het echte product.

We kunnen een sonde in het VHDL-ontwerpbestand invoegen door:

- Het declareren van een speciaal kenmerk genaamd MARK_DEBUG

- Bevestig het signaal dat we willen onderzoeken met dit attribuut

- En activeer het door het de waarde "true" te geven, zoals hieronder:

-- ATTRIBUTE DECLARATION --

ATTRIBUTE MARK_DEBUG : STRING;

ATTRIBUTE MARK_DEBUG OF count : SIGNAL IS "true";

Opmerking: we hoeven het attribuut maar één keer in elk VHDL-ontwerpbestand te declareren, zodat we het aan meerdere signalen kunnen koppelen.

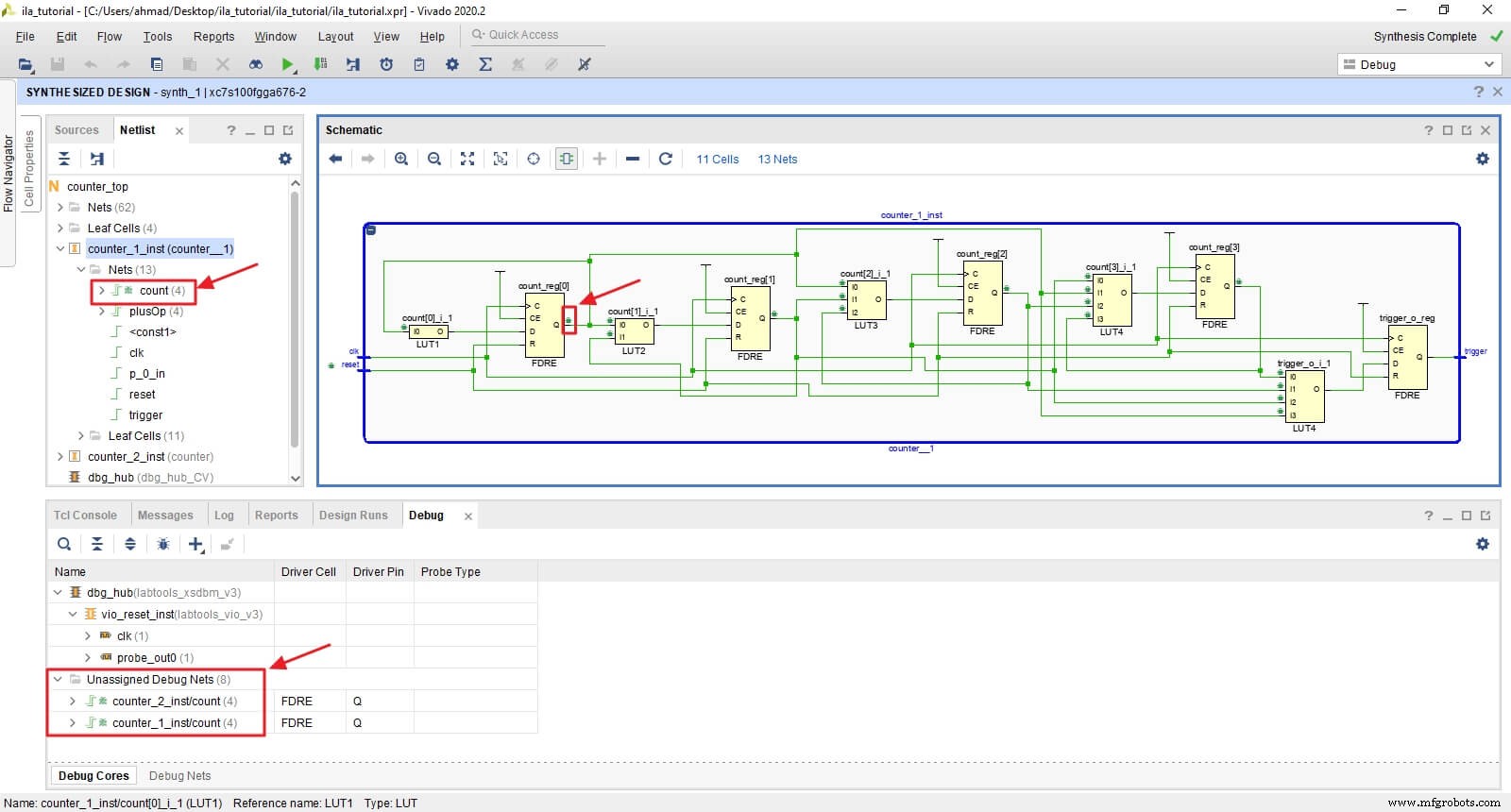

We kunnen aan het gesynthetiseerde ontwerp zien dat het signaal telt in beide counter_1_inst en counter_2_inst worden vermeld onder Niet-toegewezen foutopsporingsnetten en gemarkeerd met een bugpictogram in zowel de Netlijst en het Schema .

Invoegen uit de netlijst

Deze invoegmethode is ook eenvoudig, maar vereist dat u eerst het ontwerp synthetiseert en vervolgens handmatig op elk signaal klikt om het te markeren voor foutopsporing. Het kan vermoeiend zijn als het ontwerp groot is en je veel signalen wilt monitoren.

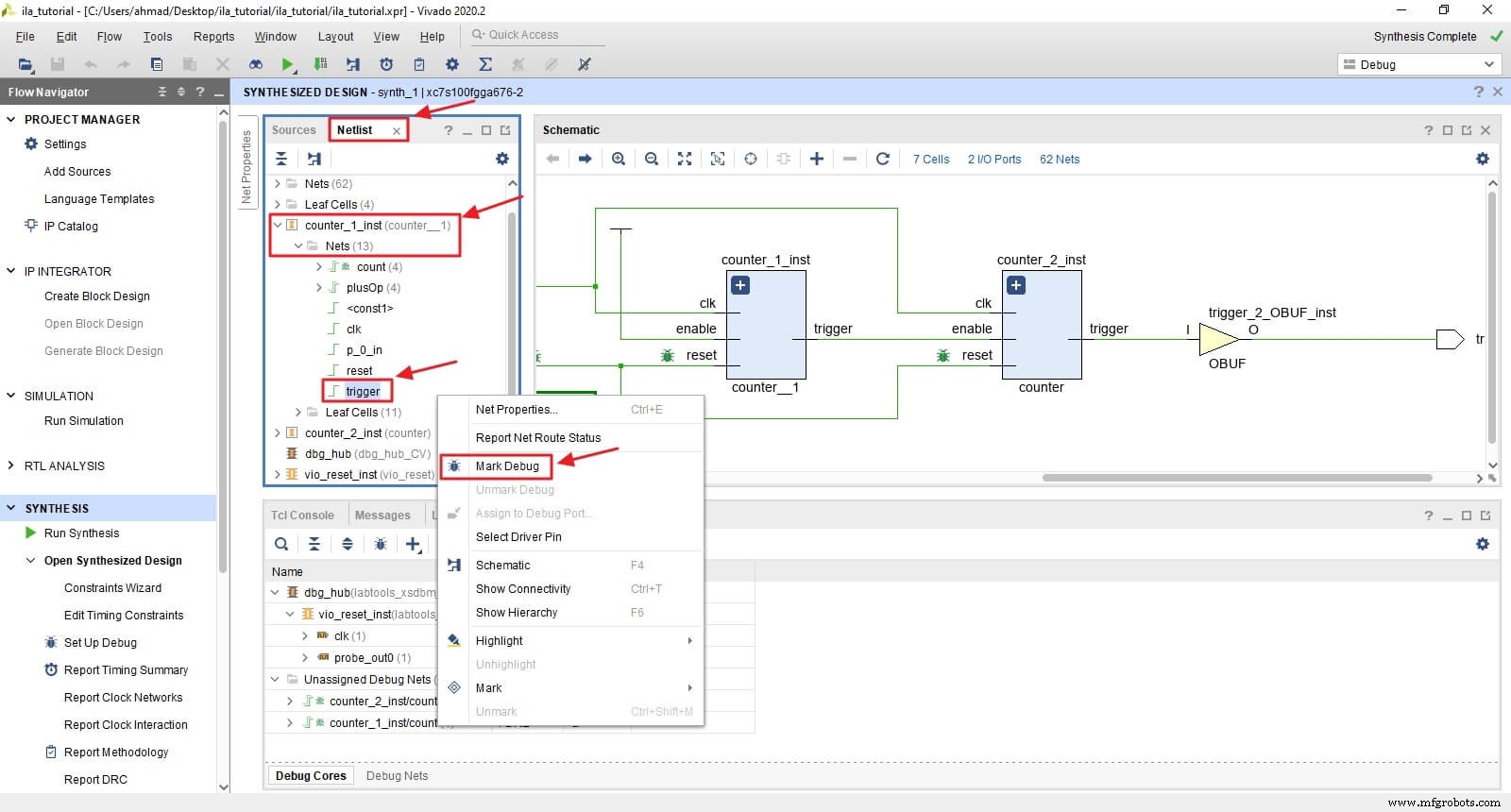

We zullen de uitvoerpoort onderzoeken trigger in beide tellers met behulp van de Netlijst . We kunnen dit doen vanuit het Netlist-venster of het Schema door het signaalnet te lokaliseren en vervolgens klik met de rechtermuisknop erop en kies Debug markeren .

Zoek in het Netlist-venster trigger onder counter_1_inst → Netten → trigger . Klik er vervolgens met de rechtermuisknop op en kies Mark Debug .

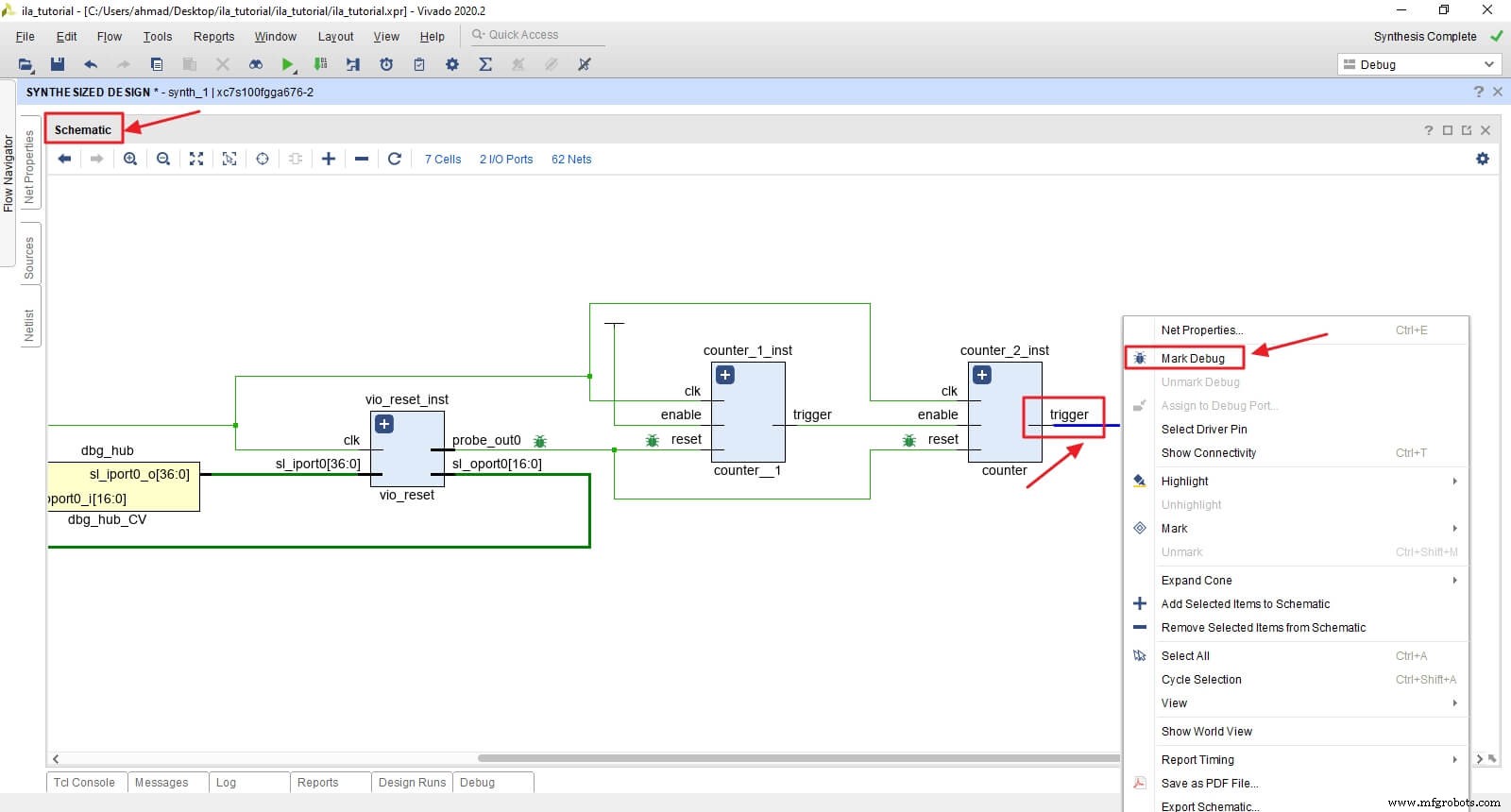

Zoek in het schemavenster trigger uitvoer van counter_2_inst . Klik er vervolgens met de rechtermuisknop op en kies Mark Debug .

We kunnen zien dat ze nu worden vermeld onder Niet-toegewezen foutopsporingsnetten .

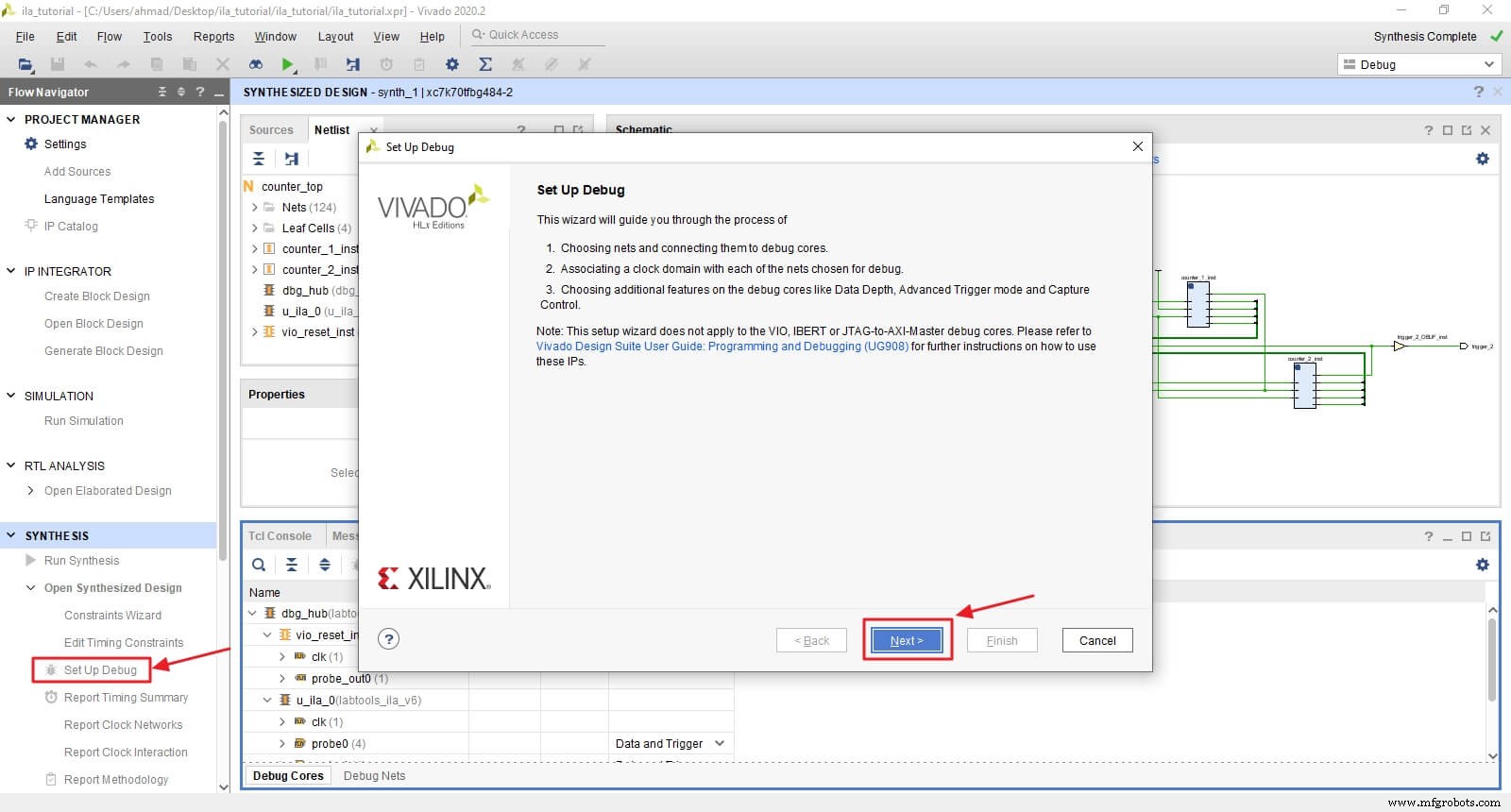

De ILA-foutopsporingskern maken

Nu is het tijd om de ILA-foutopsporingskern te maken. We moeten een sonde maken voor elk signaal dat we willen analyseren. De gemakkelijkste manier is om gebruik te maken van de Vivado-wizard Debug instellen .

Klik op Debug instellen en klik vervolgens op Volgende .

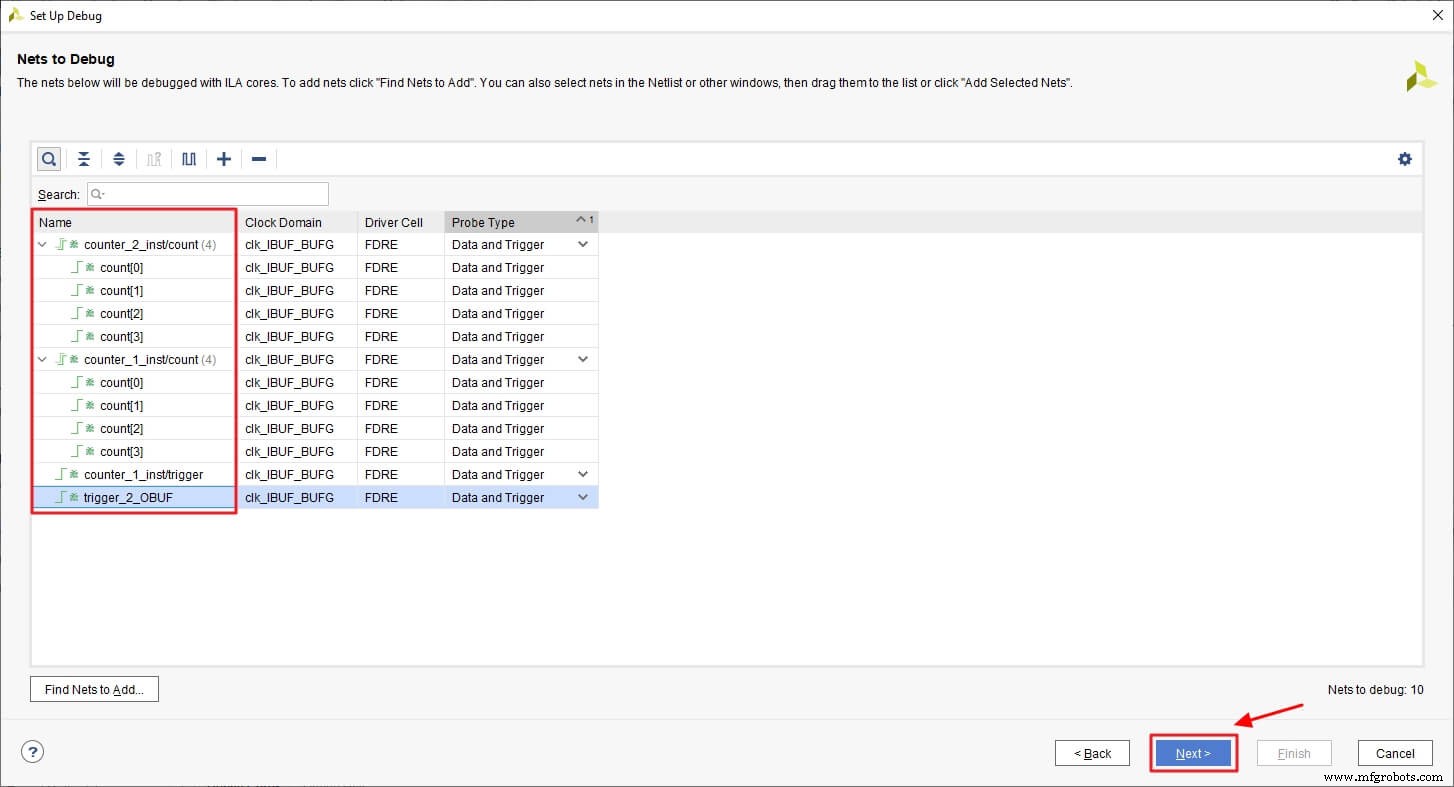

Vivado zal alle foutopsporingssignalen weergeven en het klokdomein automatisch voor u vastleggen. Hier zien we dat onze vier signalen worden vermeld. Je kunt de signalen waarin je niet geïnteresseerd bent verwijderen of extra signalen toevoegen, maar we zullen ze allemaal gebruiken.

Opmerking: we hoeven niet alle signalen te gebruiken die we hebben gemarkeerd als Debug.

Klik op Volgende .

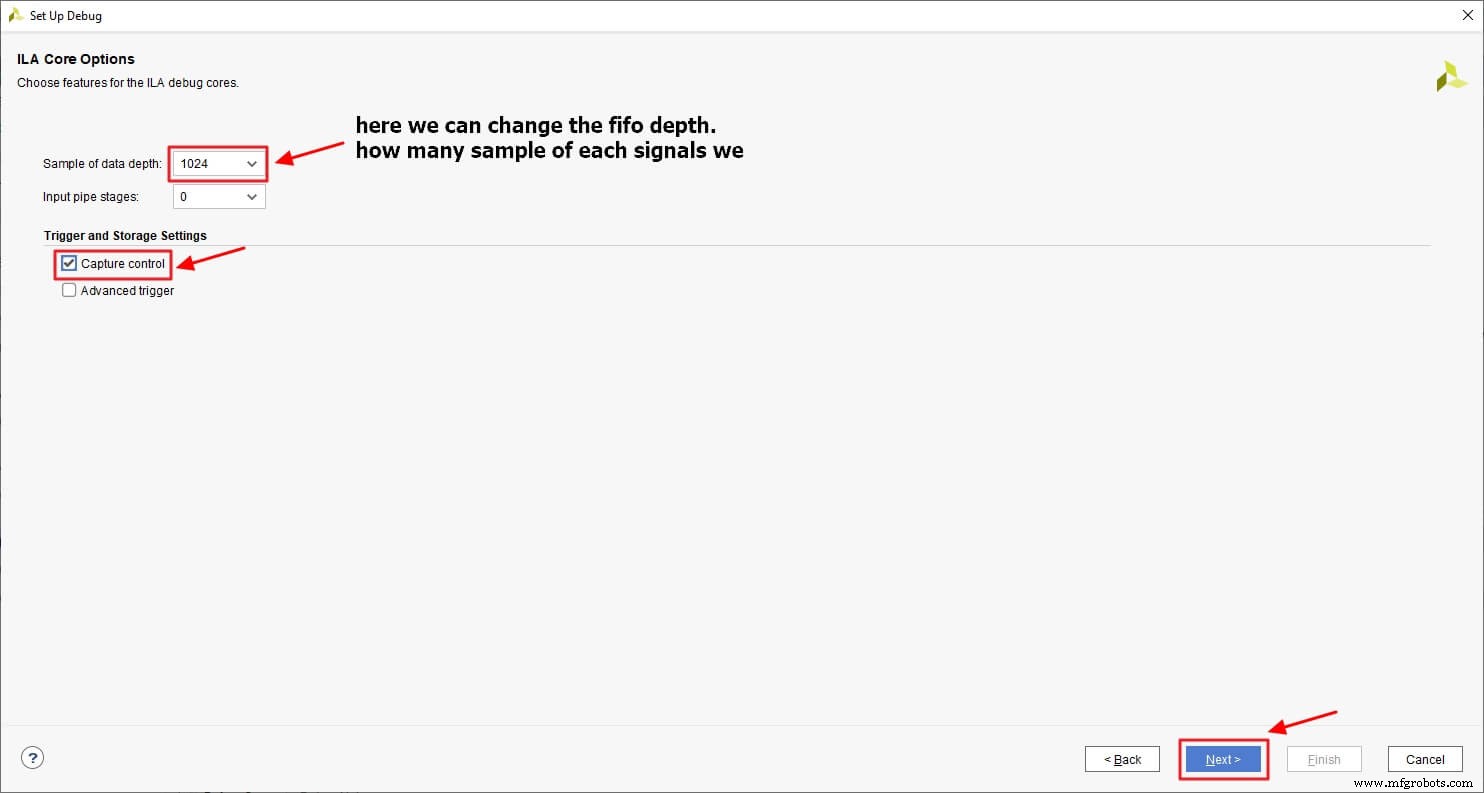

Nu configureren we de ILA door de FIFO-diepte . te kiezen en het controleren van Capture control . We kunnen de FIFO op 1024 laten staan, omdat dit voldoende diepte is voor ons voorbeeld.

Klik op Volgende .

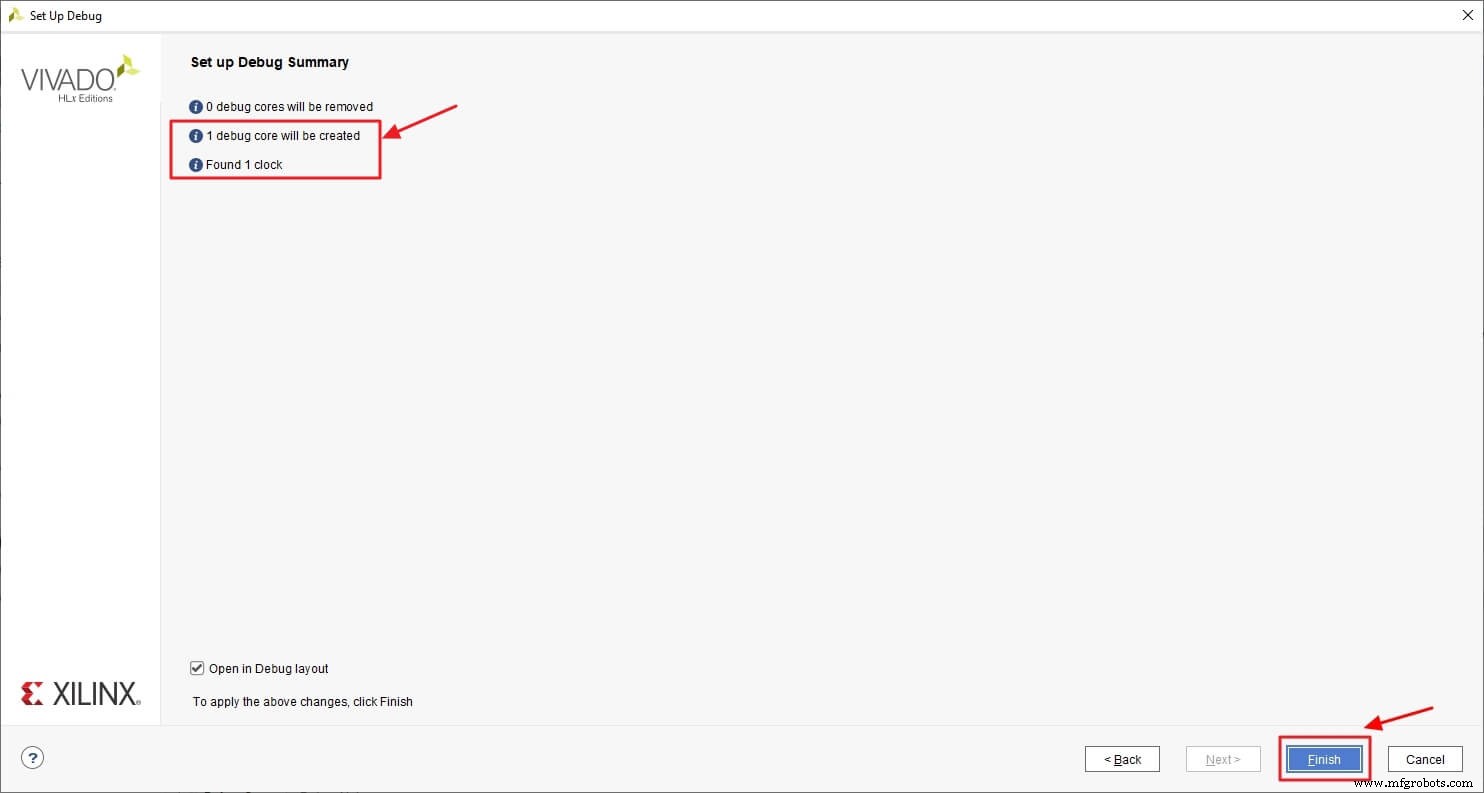

Nu zien we dat Vivado één klok heeft gevonden en één kern voor foutopsporing zal maken.

Klik op Voltooien .

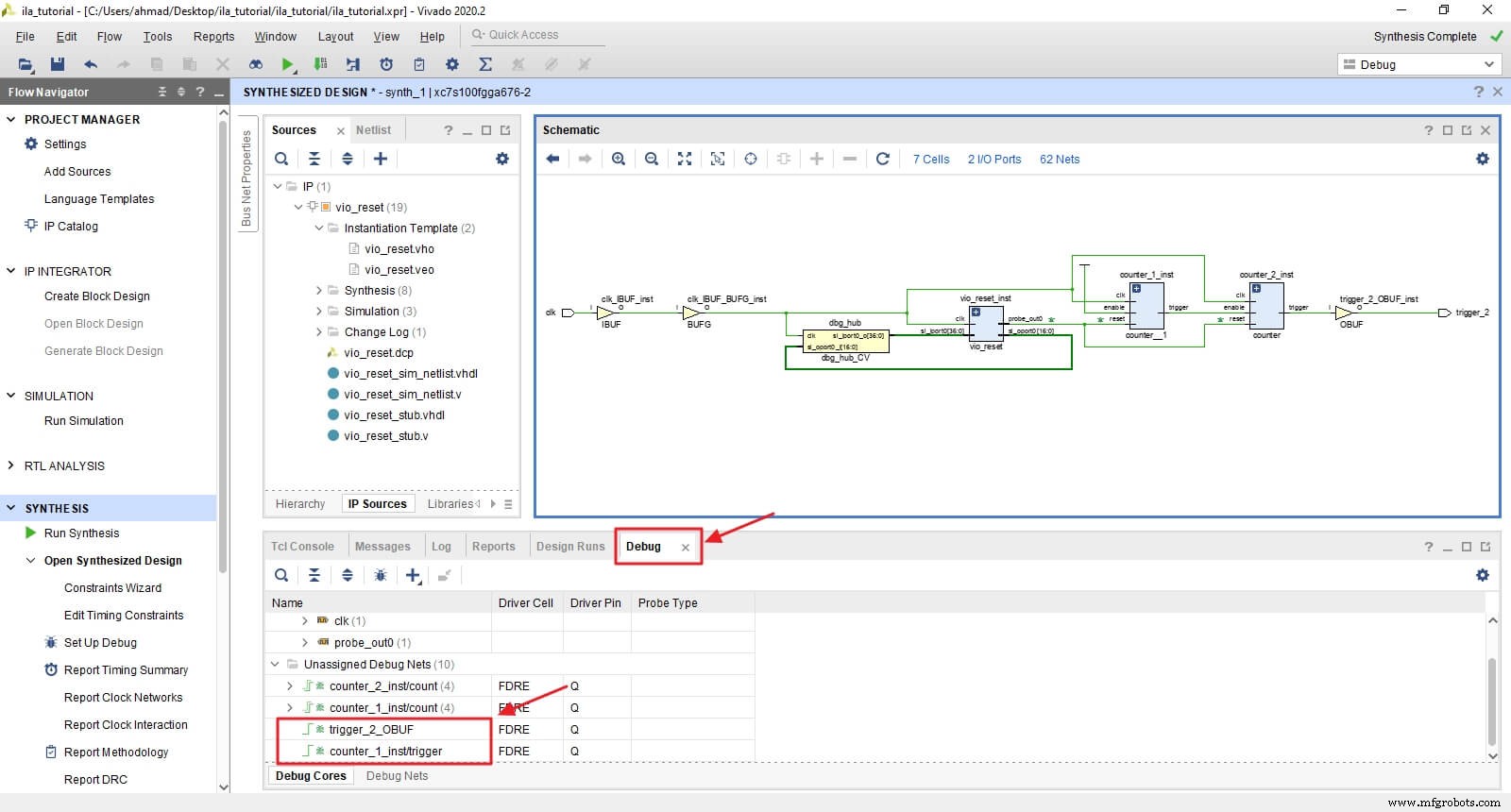

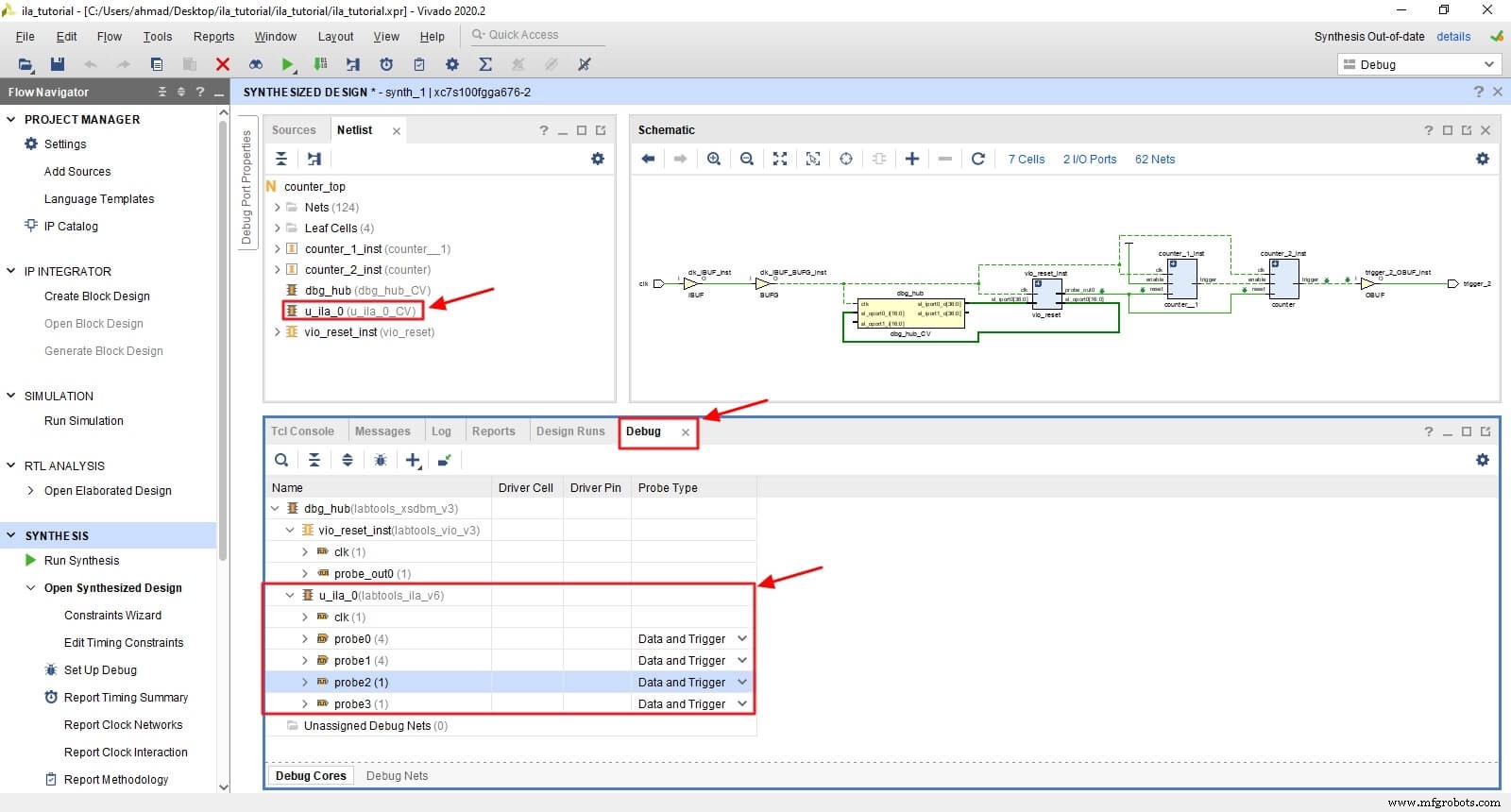

We kunnen nu een ILA debug-kern zien met vier probes toegevoegd aan het debug-tabblad en het Netlist-venster .

BELANGRIJK: Het is erg belangrijk om de beperking in deze fase op te slaan, zodat deze aan het ontwerp kan worden toegevoegd. Anders lopen we het risico onze ILA-kern te verliezen.

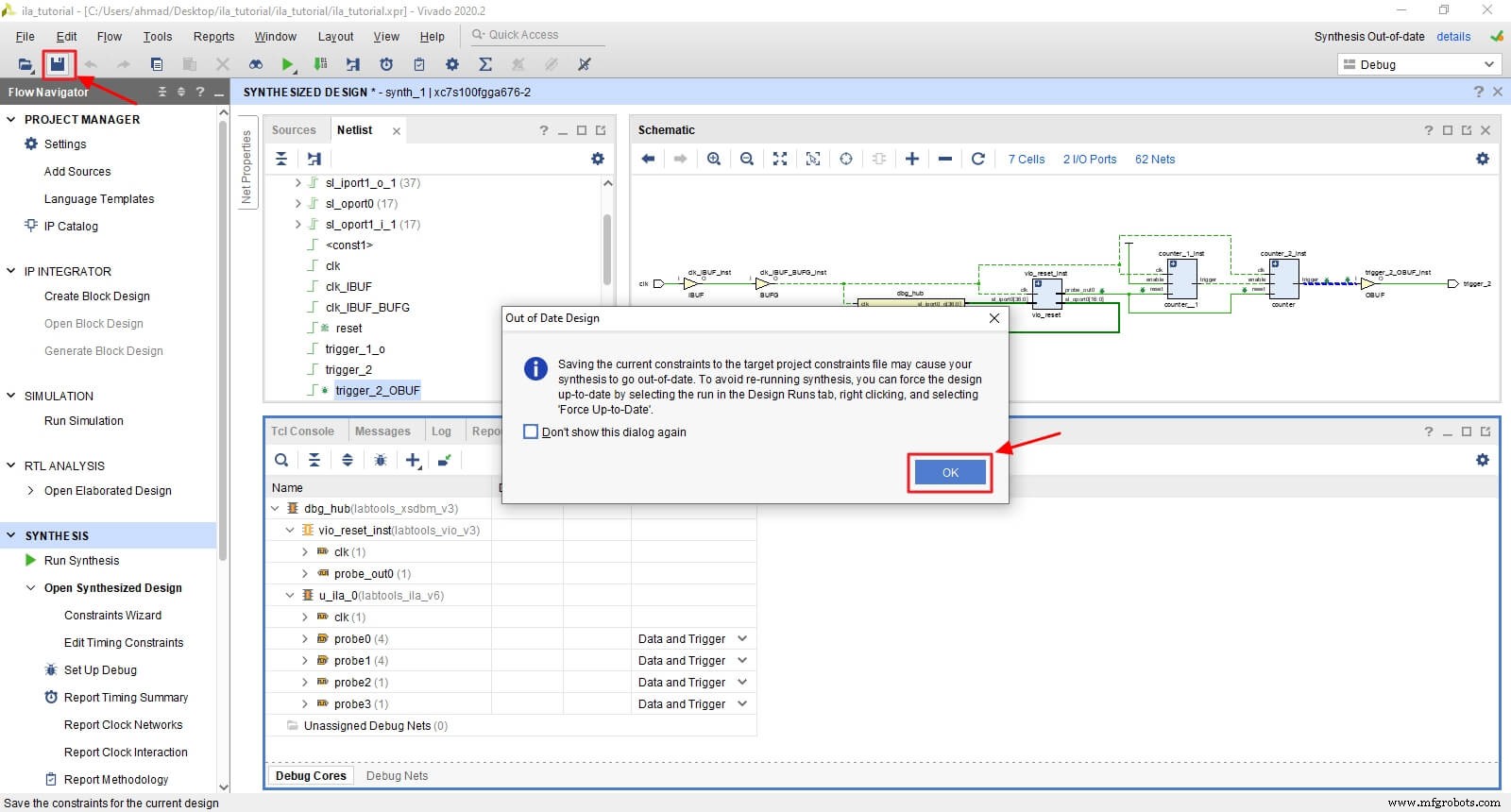

Klik op de Opslaan pictogram of druk op Ctrl+S.

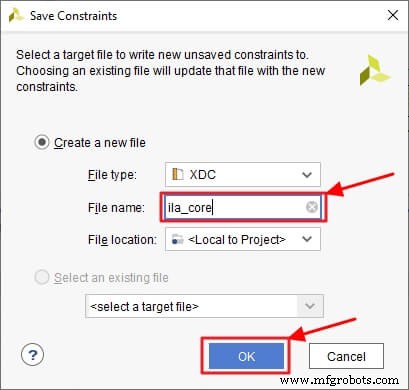

Noem het bestand ila_core en klik op OK .

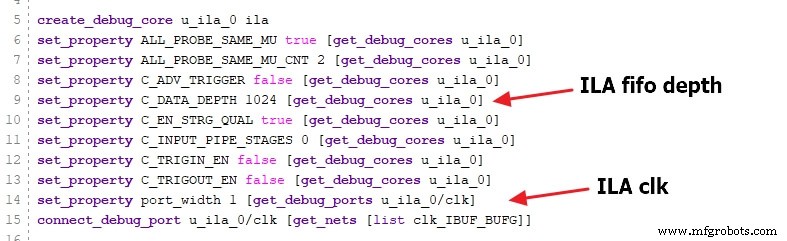

De ila_core.xdc bestand wordt toegevoegd aan de beperking en bevat de code en instellingen voor de ILA.

Laten we eens kijken naar de inhoud van het bestand. U kunt het bestand openen door naar het Bronvenster te gaan → de beperkingsmap uit te vouwen → constr_1 uit te vouwen .

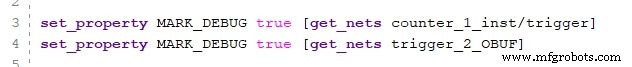

Ten eerste zien we dat het bestand een debug-attribuut toevoegt aan de signalen die we hebben gemarkeerd als debug met behulp van de Netlist-invoeging.

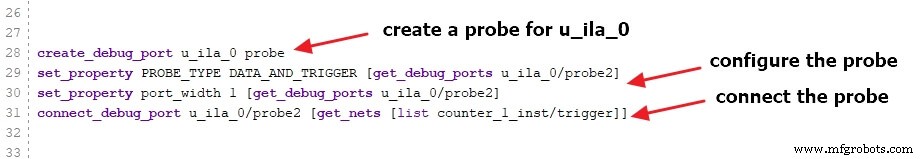

Vervolgens zien we de creatie en configuratie van een ILA-kern.

Vervolgens zien we de creatie, configuratie en verbinding voor elke sonde.

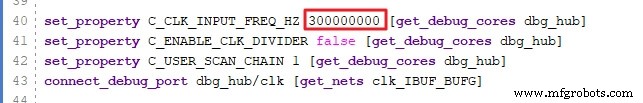

Vervolgens zien we het maken van een debug-hub (dbg_hub ).

De debug-hub is verantwoordelijk voor de communicatie tussen Vivado IDE en de debug-cores (ILA en VIO). We zien dat het een klokfrequentie definieert (standaard is 300 MHz). U moet die klok aanpassen aan uw klokfrequentie en het bestand opslaan.

Opmerking: de klok die is aangesloten op ILA en Debug_hub moet een vrijlopende klok zijn.

Nu is de ILA voltooid en opgeslagen. We moeten de synthese opnieuw uitvoeren zodat de ILA kan worden toegevoegd aan het gesynthetiseerde ontwerp.

Klik op Synthese uitvoeren en dan op OK .

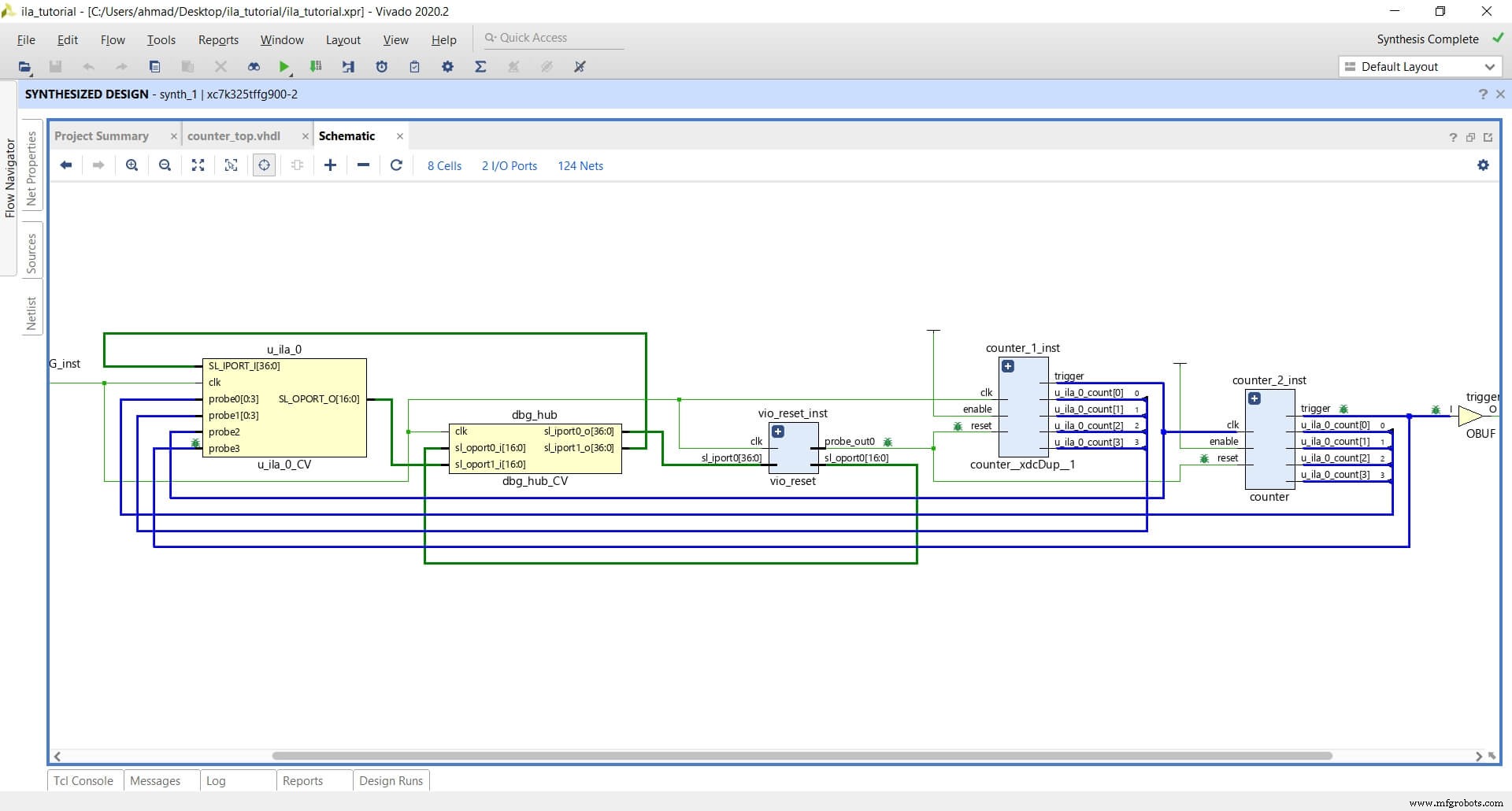

Wanneer Vivado klaar is met het uitvoeren van de synthese, klikt u op Open synthetisch ontwerp en dan op Schema .

We kunnen nu zien dat Vivado de ILA en Debug_Hub aan ons ontwerp heeft toegevoegd en de debug-signalen heeft aangesloten op de ILA-sondes.

Nu zijn we klaar om ons ontwerp te implementeren en de bitstream te genereren, zodat we ons ontwerp kunnen testen.

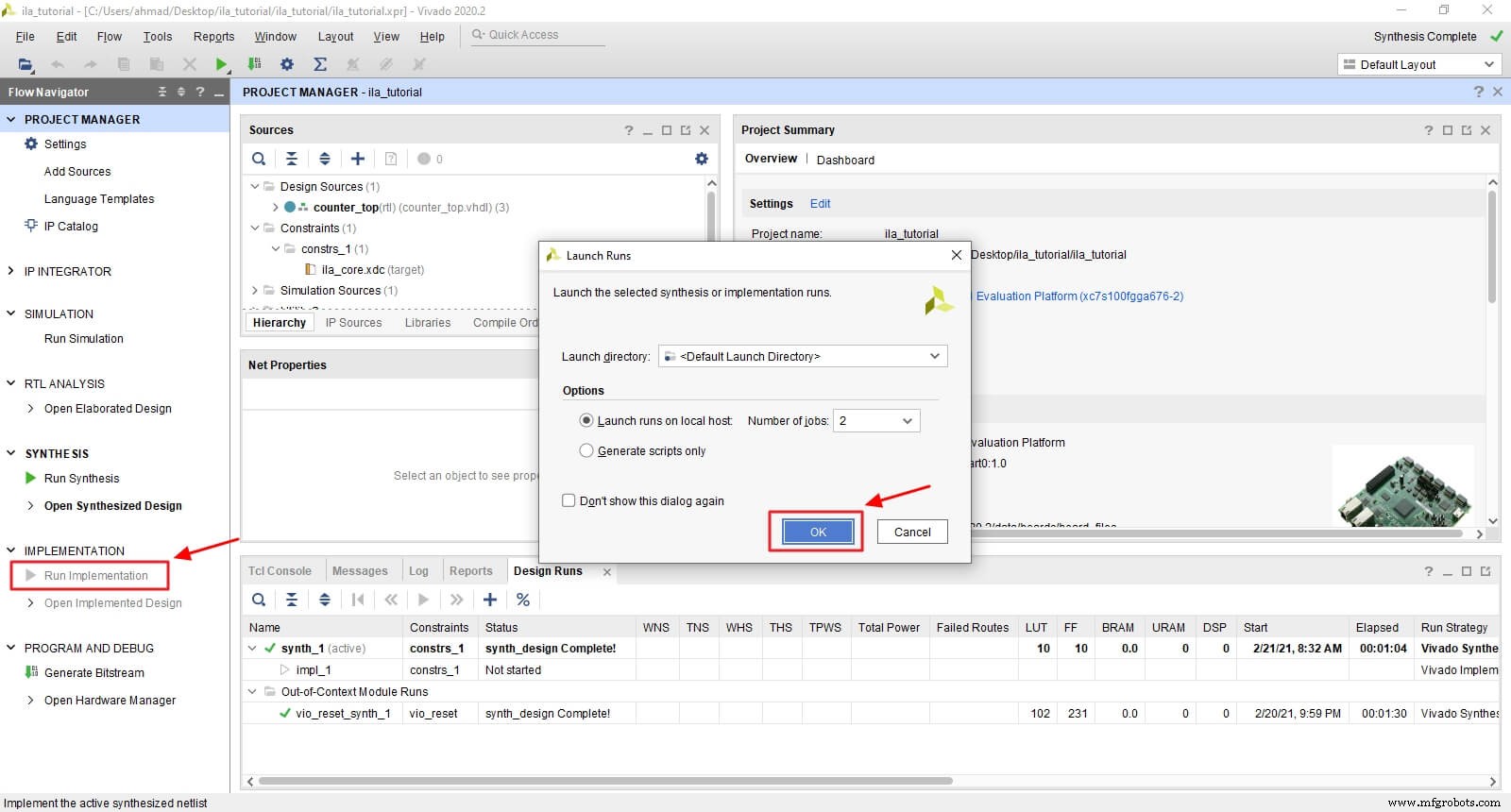

Klik op Implementatie uitvoeren en dan op OK .

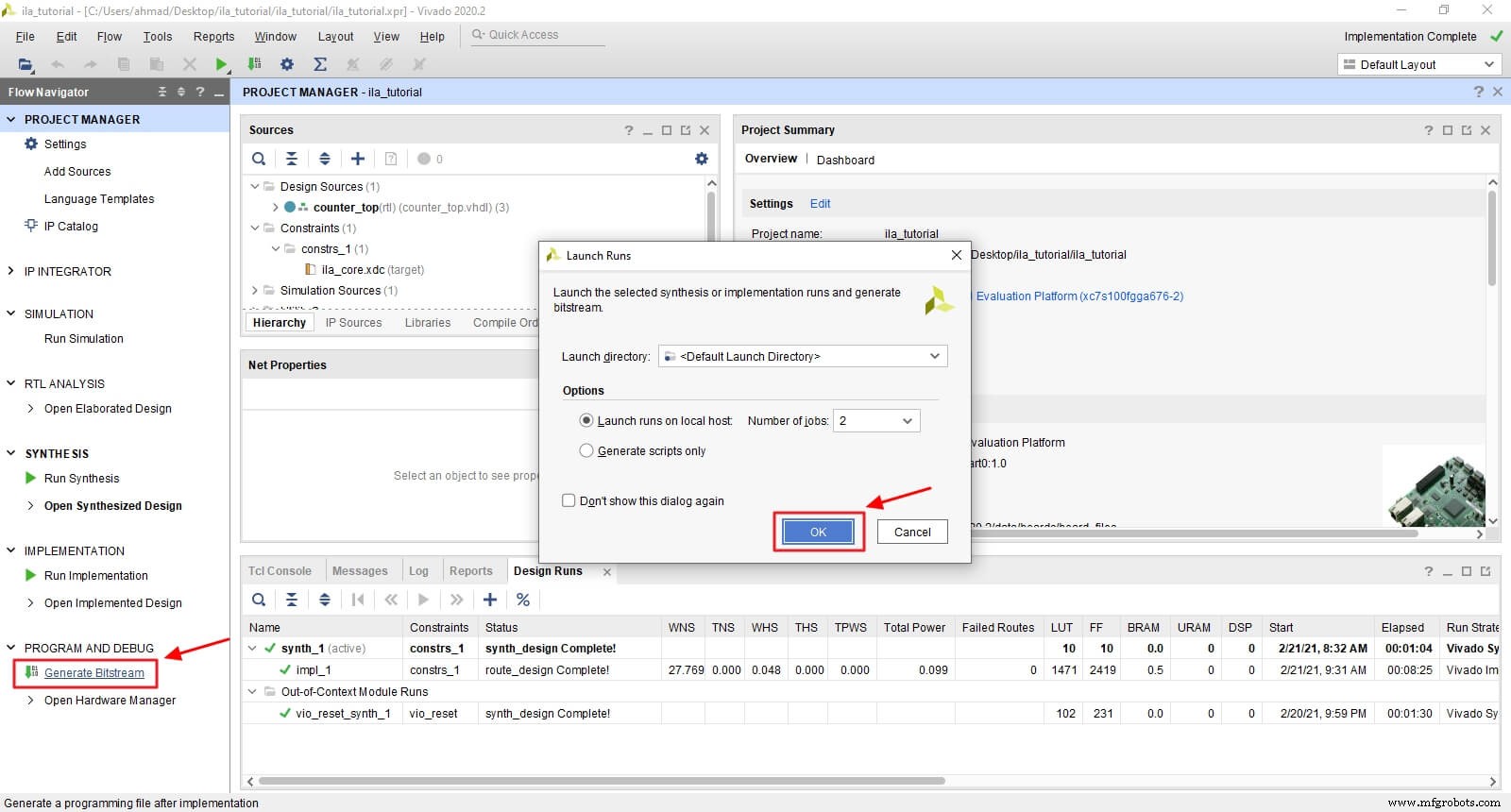

Nadat Vivado klaar is met het uitvoeren van de implementatie, klikt u op Bitstream genereren en dan op OK .

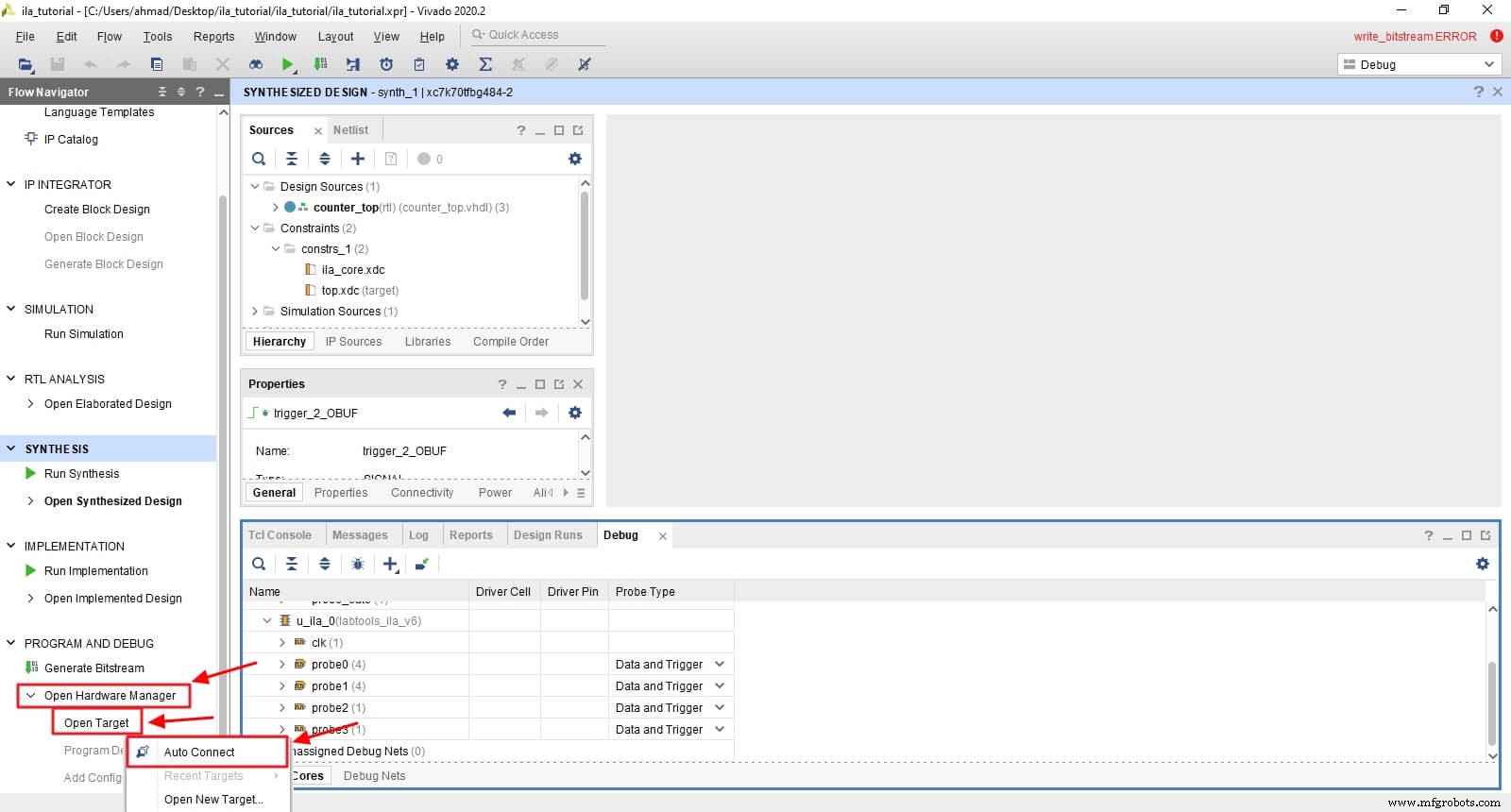

Nadat Vivado klaar is met het genereren van de bitstream, klikt u op Hardwarebeheer openen en dan op Doel openen, en tot slot op Automatisch verbinden .

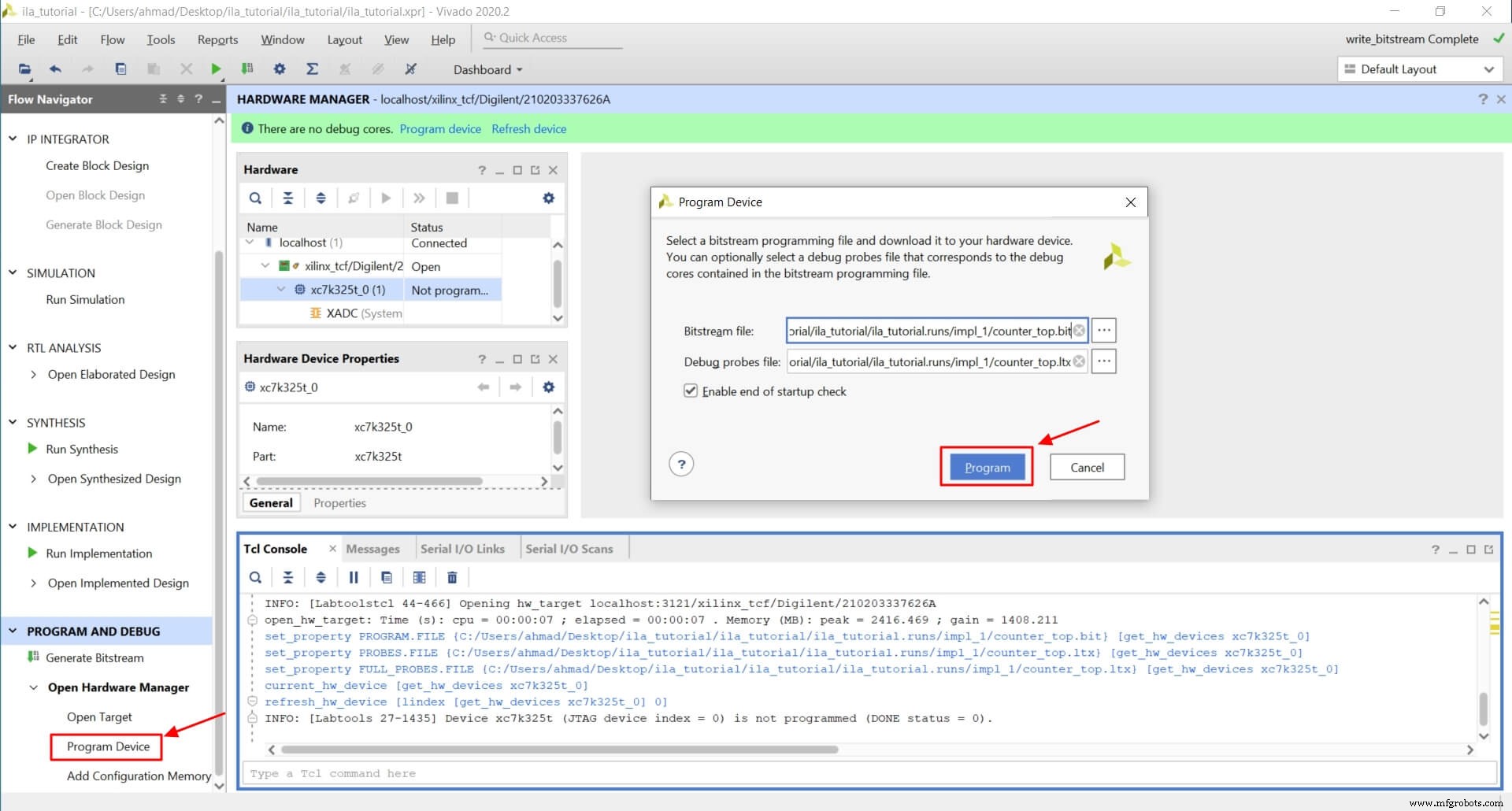

Vervolgens moeten we de FPGA programmeren met het bitbestand (*.bit) en het debug-probebestand (*.ltx). Vivado vindt ze automatisch voor je.

Klik op Apparaat programmeren en dan op Programma .

De ILA-triggers configureren

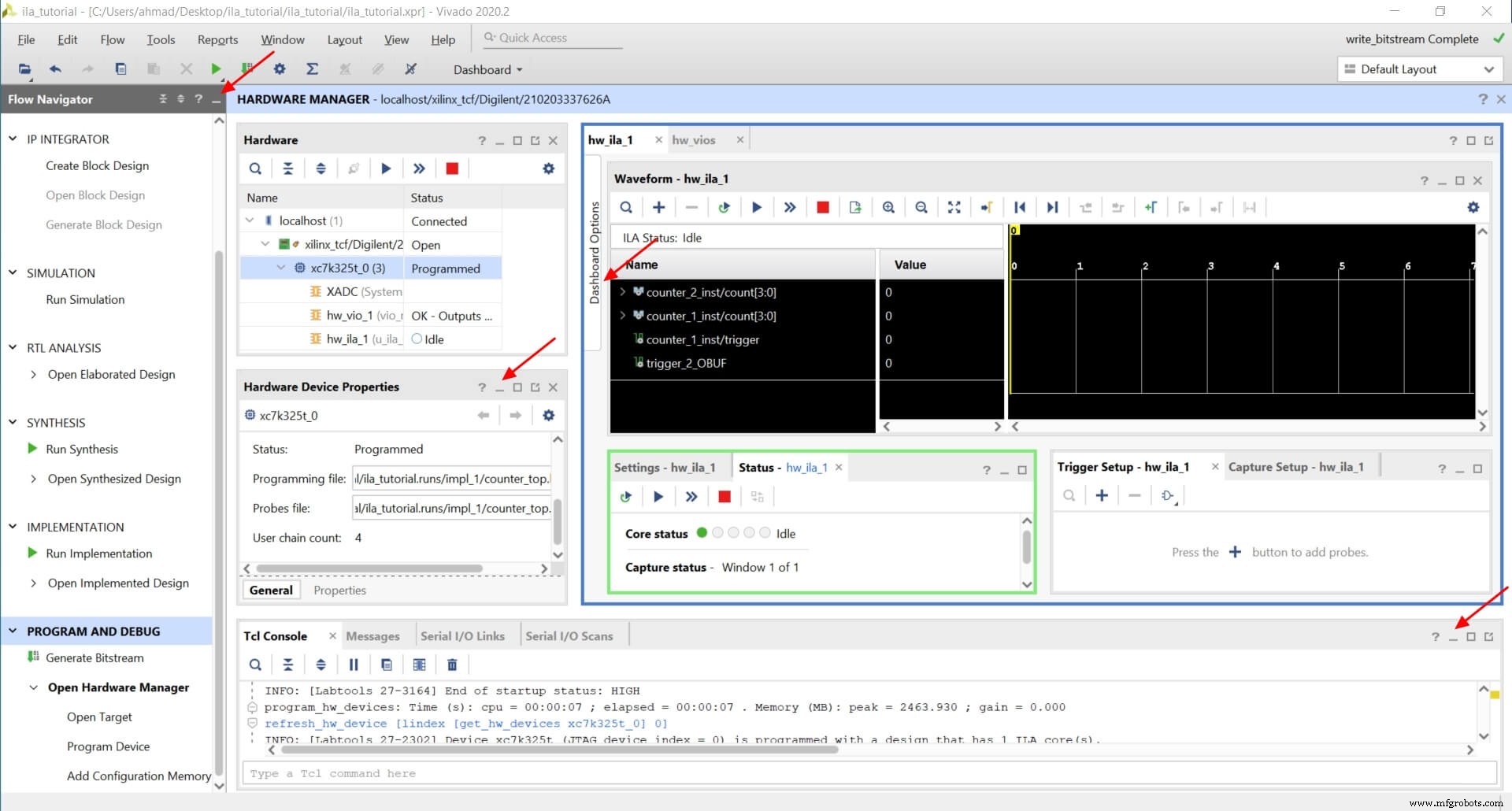

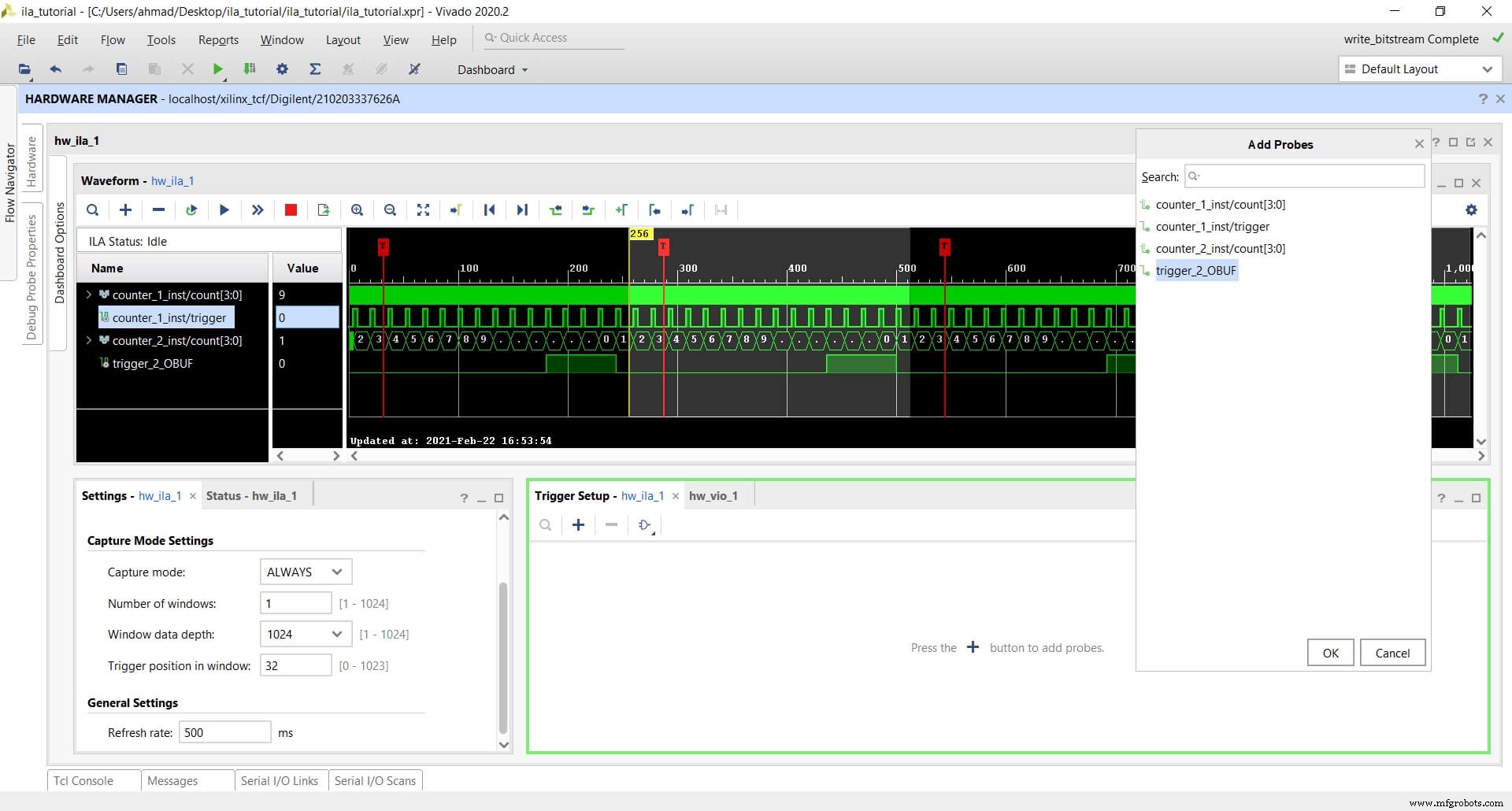

Na het programmeren van het apparaat, kunnen we zien dat de GUI-layout van Vivado is veranderd en een nieuwe hw_ila_1 dashboard is geopend en bevat verschillende vensters.

We zullen sommige vensters die we niet nodig hebben minimaliseren, zodat we comfortabel kunnen werken.

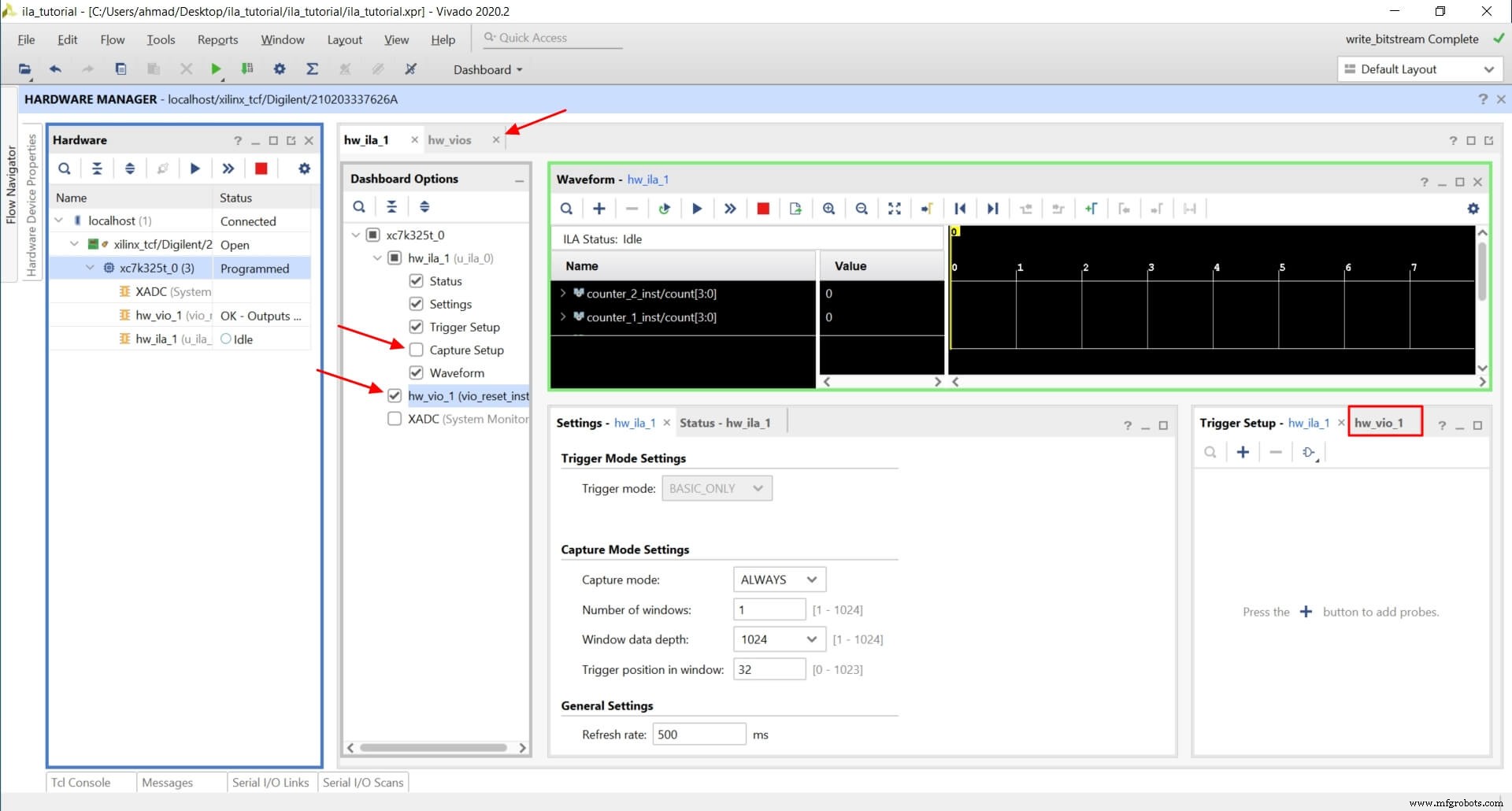

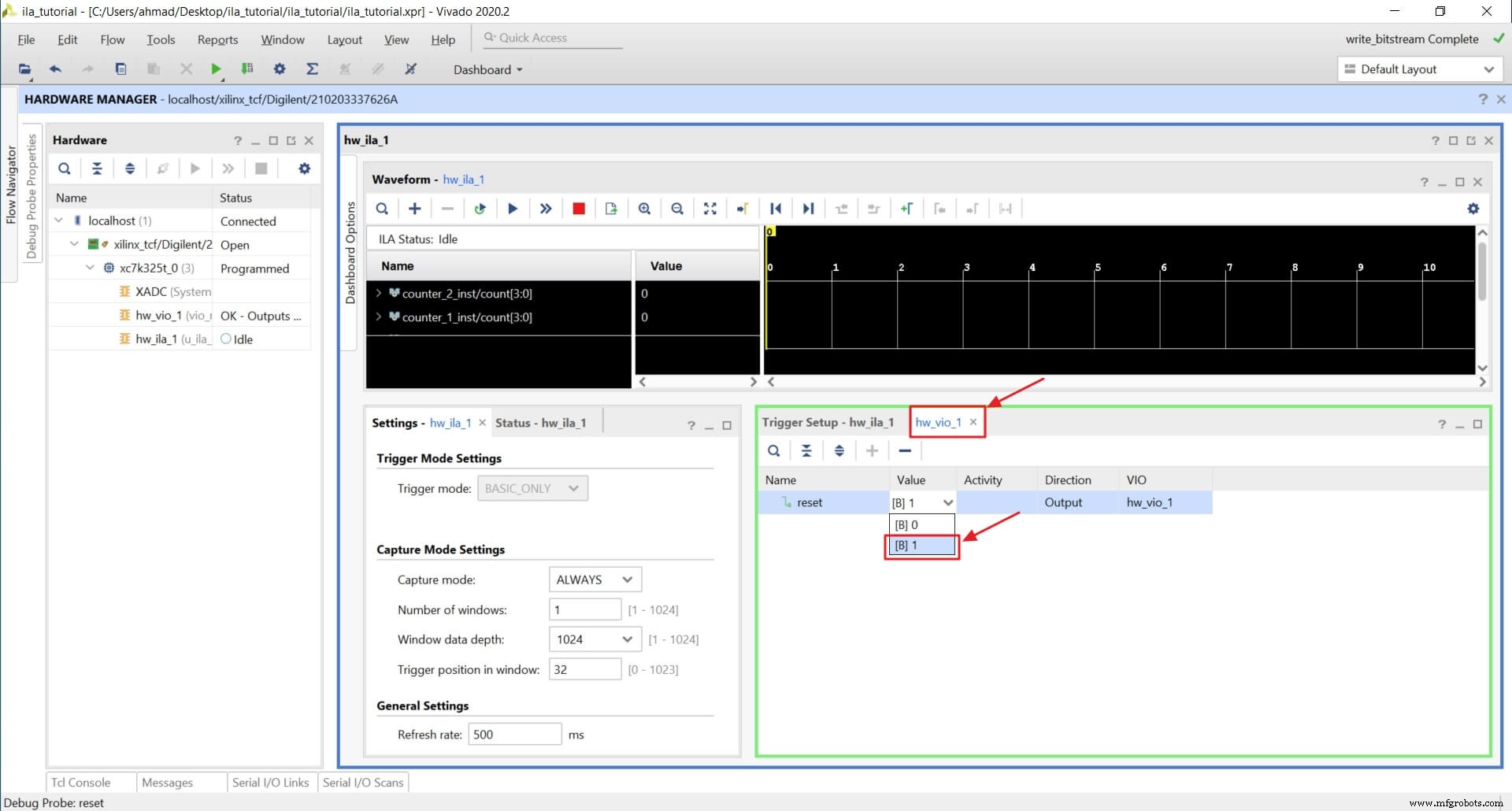

Vink in de dashboardopties hw_vio_1 . aan en verwijder het vinkje bij Capture Setup .

Sluit ook de hw_vios tabblad omdat toen we hw_vio_1 . controleerden , het is toegevoegd aan de Trigger setup venster.

Nu moeten we de reset . toevoegen knop naar de VIO zodat we de reset . kunnen bedienen .

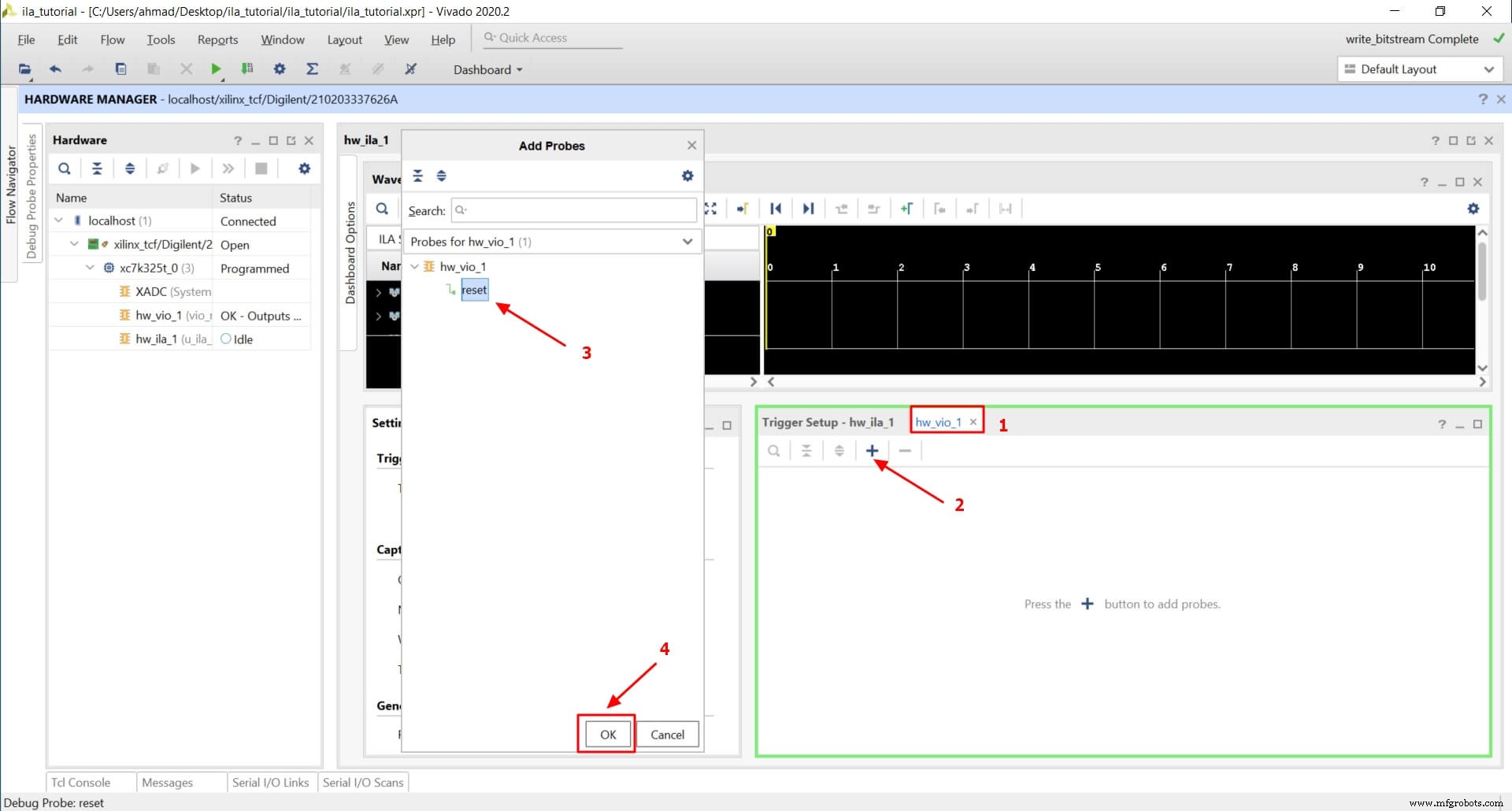

Klik op hw_vio_1 en voeg vervolgens reset . toe zoals weergegeven in de onderstaande afbeelding.

We kunnen zien dat hw_vio_1 bevat nu de reset sonde.

Wijzig de waarde van de reset in vio_reset naar 1 als het niet 1 is.

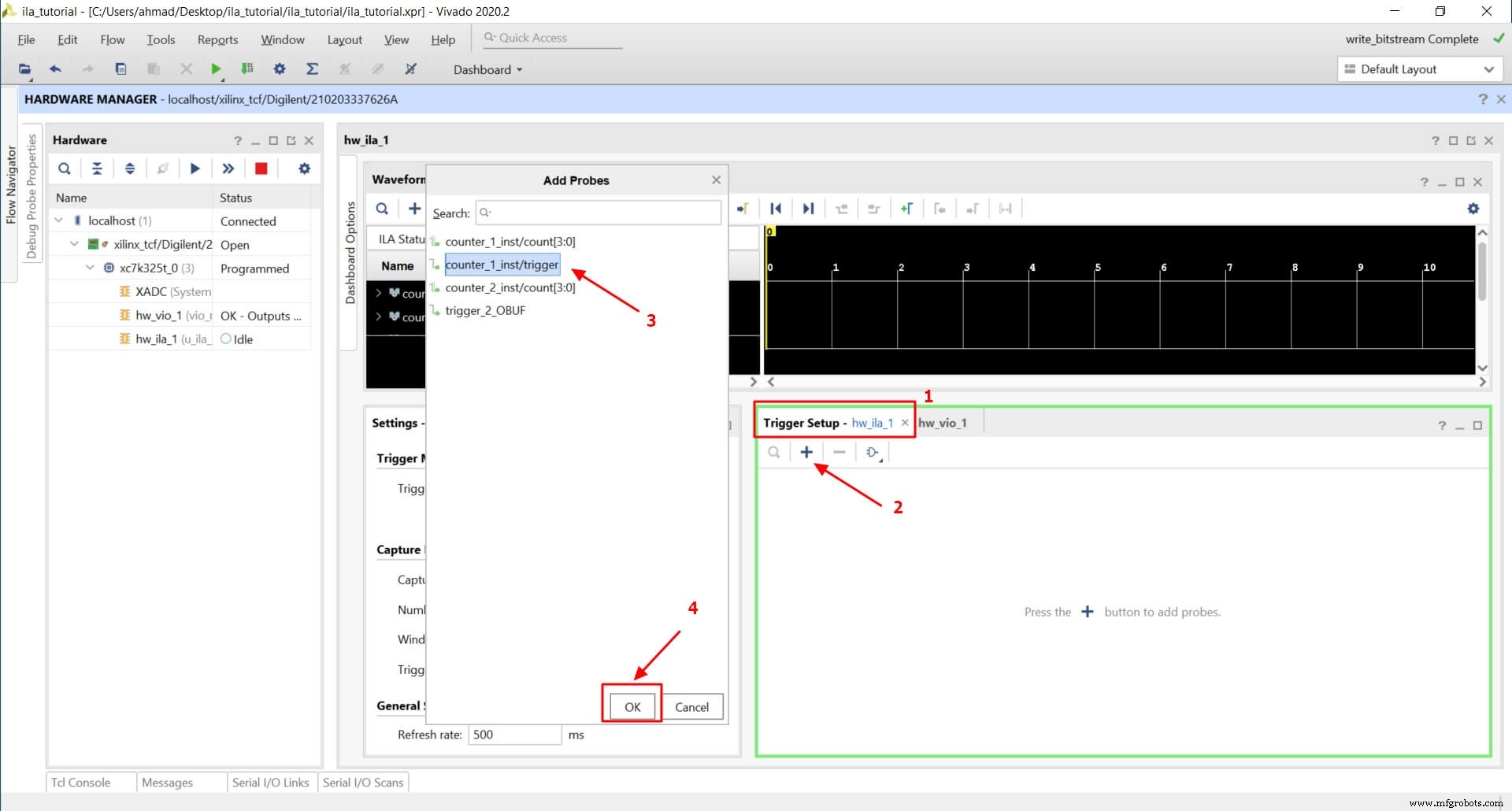

Nu zullen we de triggers toevoegen die we zullen gebruiken. Een verandering van waarde op een triggersignaal zorgt ervoor dat de ILA begint met het opnemen van de getaste signalen.

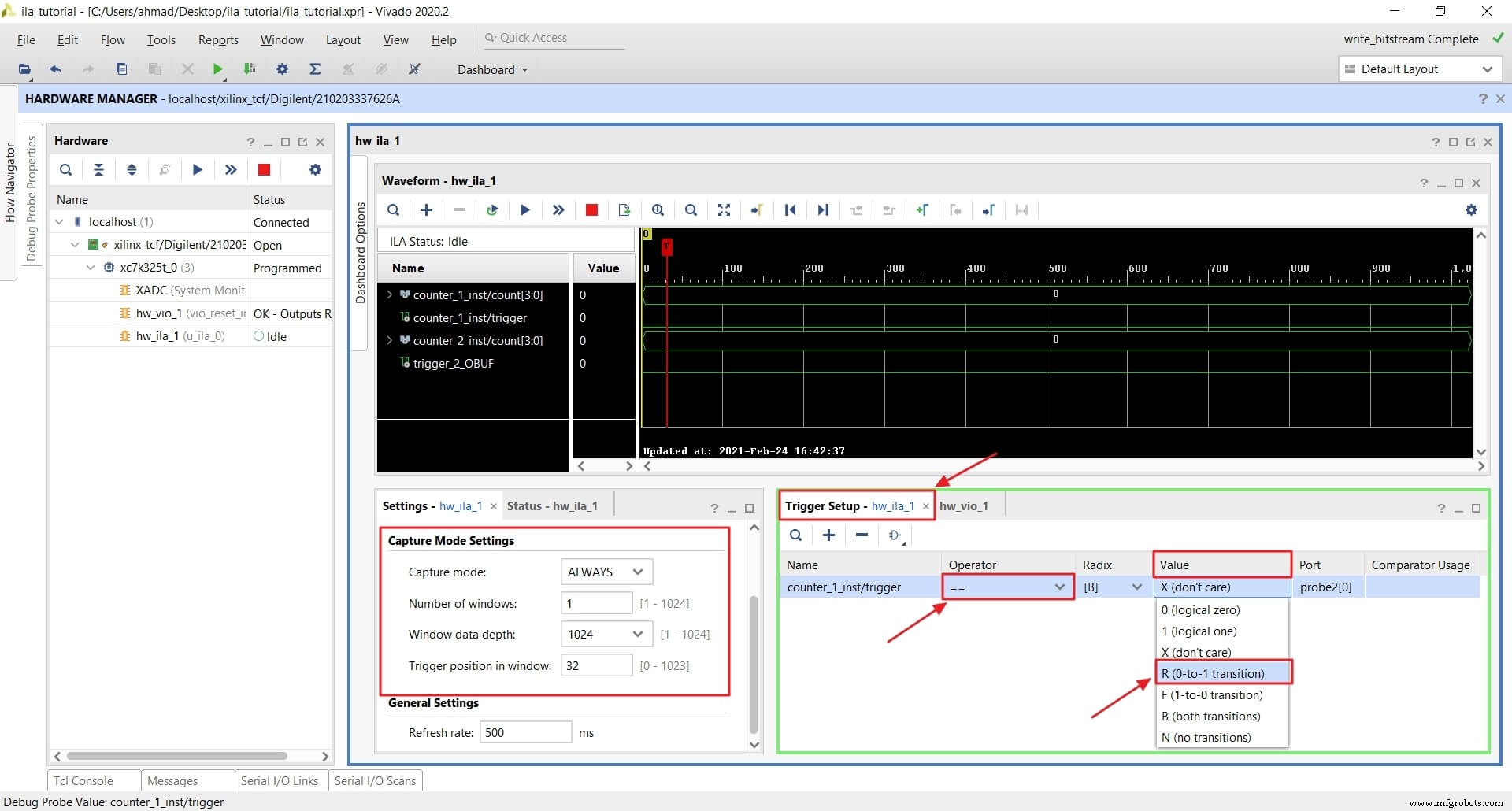

Laten we zeggen dat we willen triggeren (start opnemen) op de stijgende rand van de uitvoerpoort trigger van counter_1_inst . Volg hiervoor deze stappen:

- Ga naar de Trigger Setup – hw_ila_1 venster

- Klik op de + pictogram om een nieuwe trigger toe te voegen en kies counter_1_inst/trigger en klik op OK.

- We kunnen zien dat de trigger is toegevoegd en nu moeten we de voorwaarde instellen. Klik op het Waardevak en kies R(0 naar 1 overgang) . Klik op het Operatorvenster en kies ==(gelijk aan)

We zullen ook de triggerpositie wijzigen in 32, wat betekent dat er 32 samples worden opgenomen vóór de triggergebeurtenis, naast wat erna komt.

Nu is de trigger ingesteld en klaar om te worden ingeschakeld.

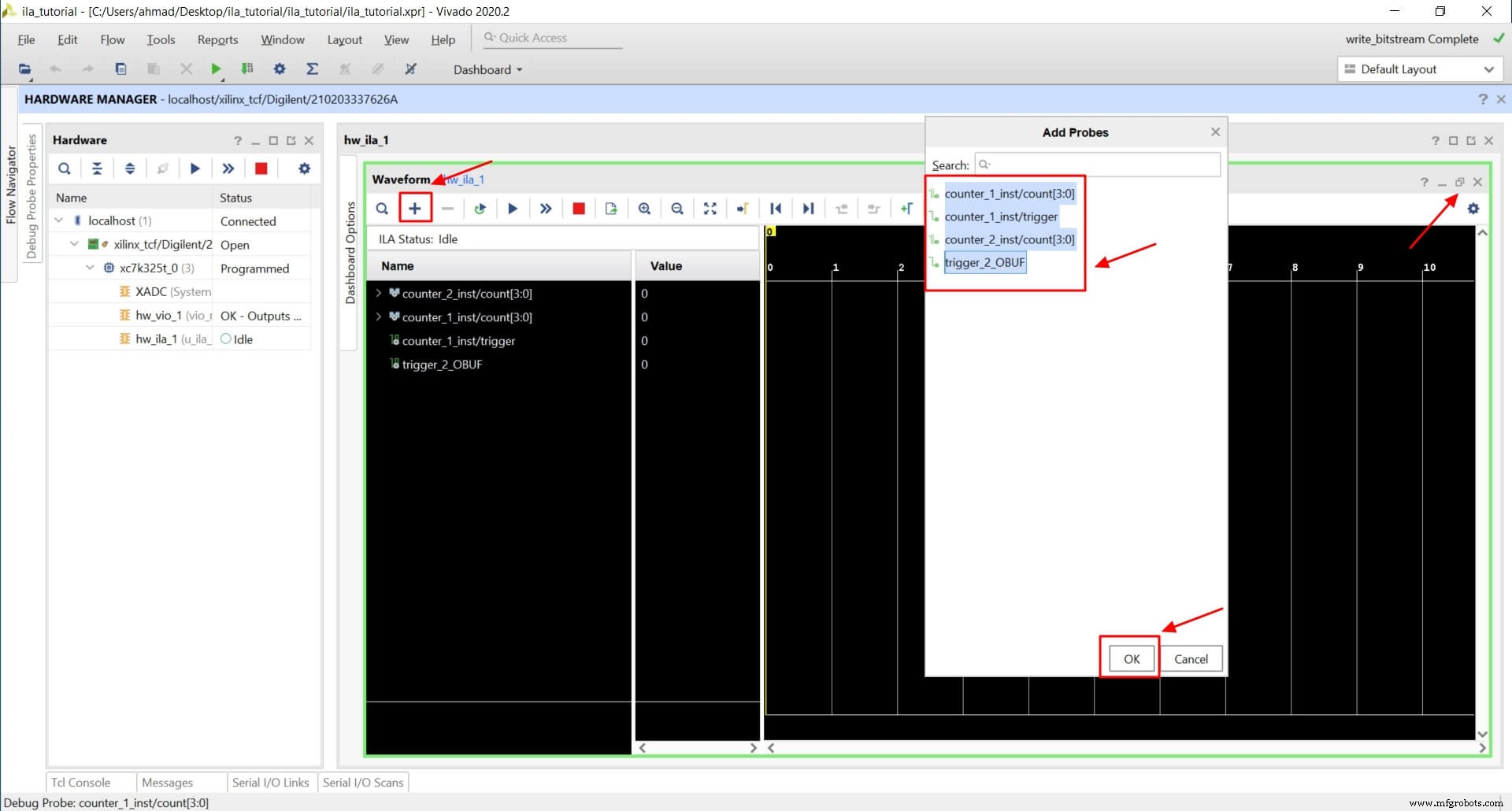

Nu gaan we naar het golfvormvenster om de signalen toe te voegen die we willen bekijken. Laten we eerst het binnenvenster maximaliseren om een beter zicht te krijgen.

Ten tweede moeten we enkele ontbrekende signalen aan de sonde toevoegen. Vivado voegt normaal gesproken alle toegewezen signalen automatisch toe, maar in dit geval niet.

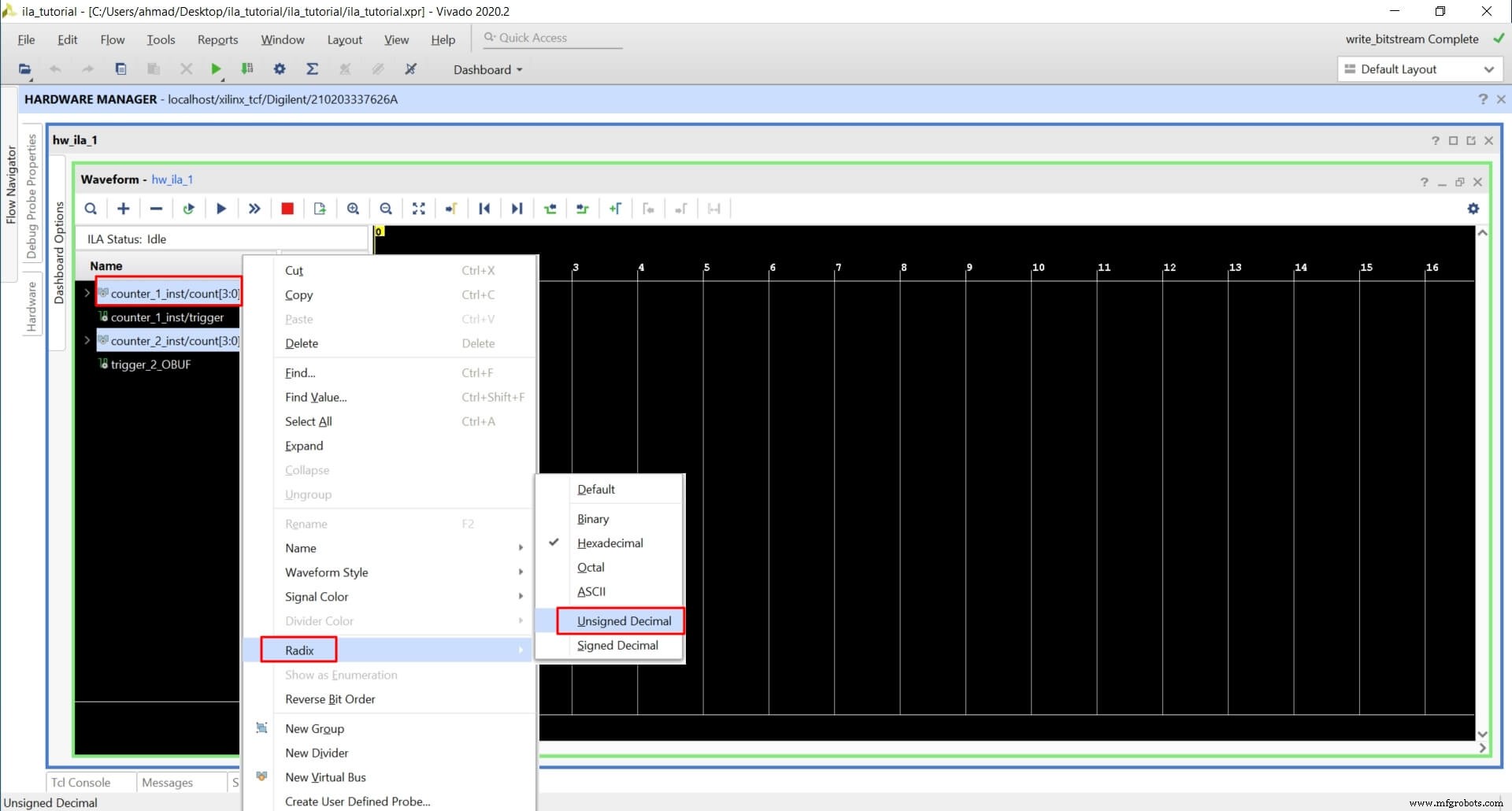

Nu veranderen we de radix van de count signaal naar Unsigned omdat het gemakkelijker te volgen is.

Klik met de rechtermuisknop op de telling signaalnaam en kies vervolgens radix en dan Niet ondertekend .

De ILA en VIO gebruiken

Nu zijn we klaar met het configureren en aanpassen van de ILA en zijn we klaar om het uit te voeren.

ILA heeft twee loopmodi:Direct en triggeren .

Directe modus

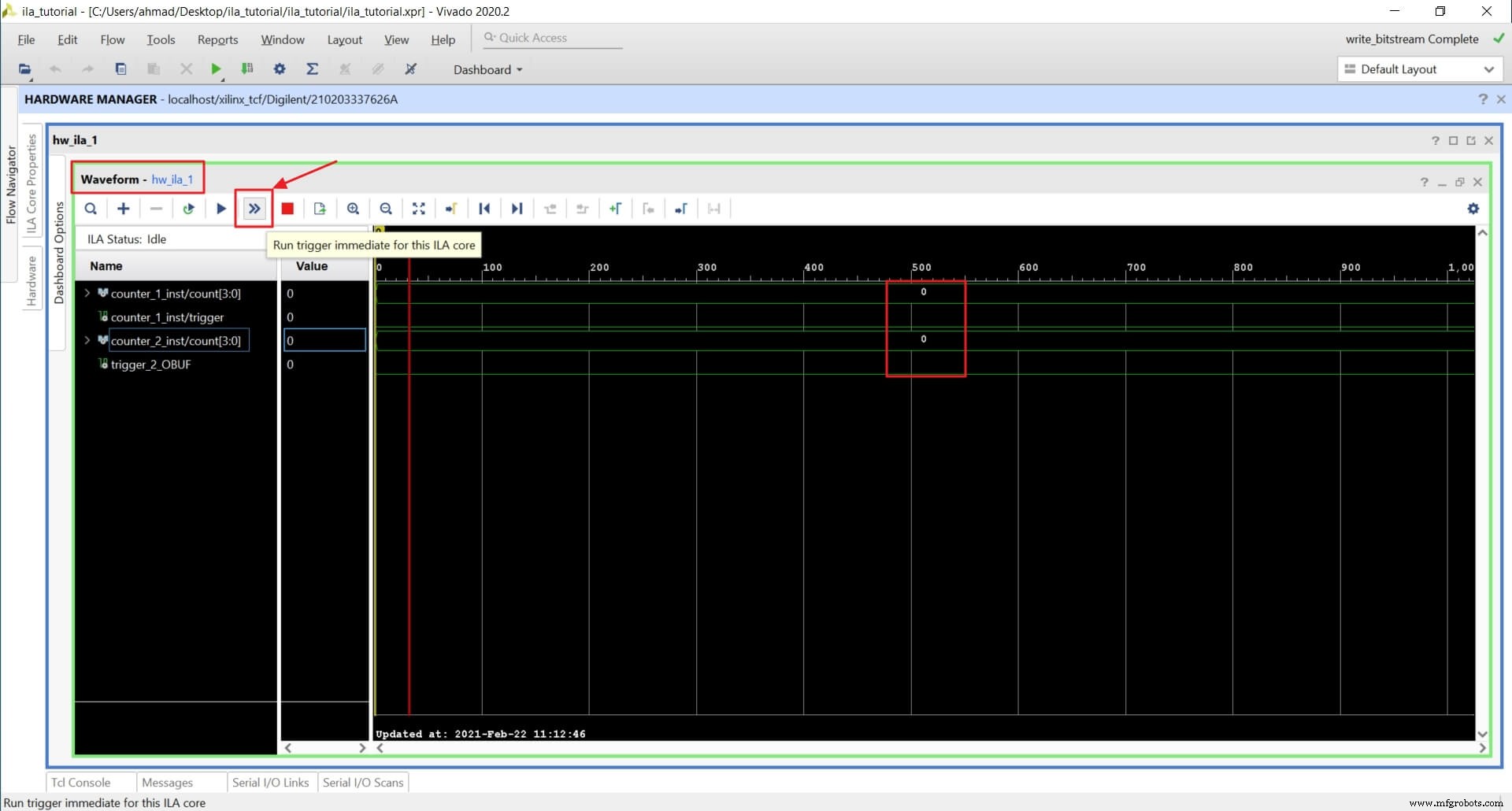

De directe modus activeert de ILA onmiddellijk en begint de samples direct op te nemen totdat de FIFO vol is.

Klik op de Trigger onmiddellijk uitvoeren knop.

We kunnen nu de opgenomen samples in het golfvormvenster zien. We zien dat beide tellen signalen zijn 0, en beide triggeren signalen zijn laag '0' omdat de reset is actief.

Triggermodus

De triggermodus vereist dat we een voorwaarde instellen voor ten minste één trigger en deze inschakelen. De ILA blijft wachten tot de toestand van de geactiveerde trigger waar wordt, en begint dan direct met het opnemen van de samples totdat de FIFO vol is.

We hebben de trigger al toegevoegd en ingesteld op R(0 naar 1 overgang) .

ILA uitvoeren met één trigger

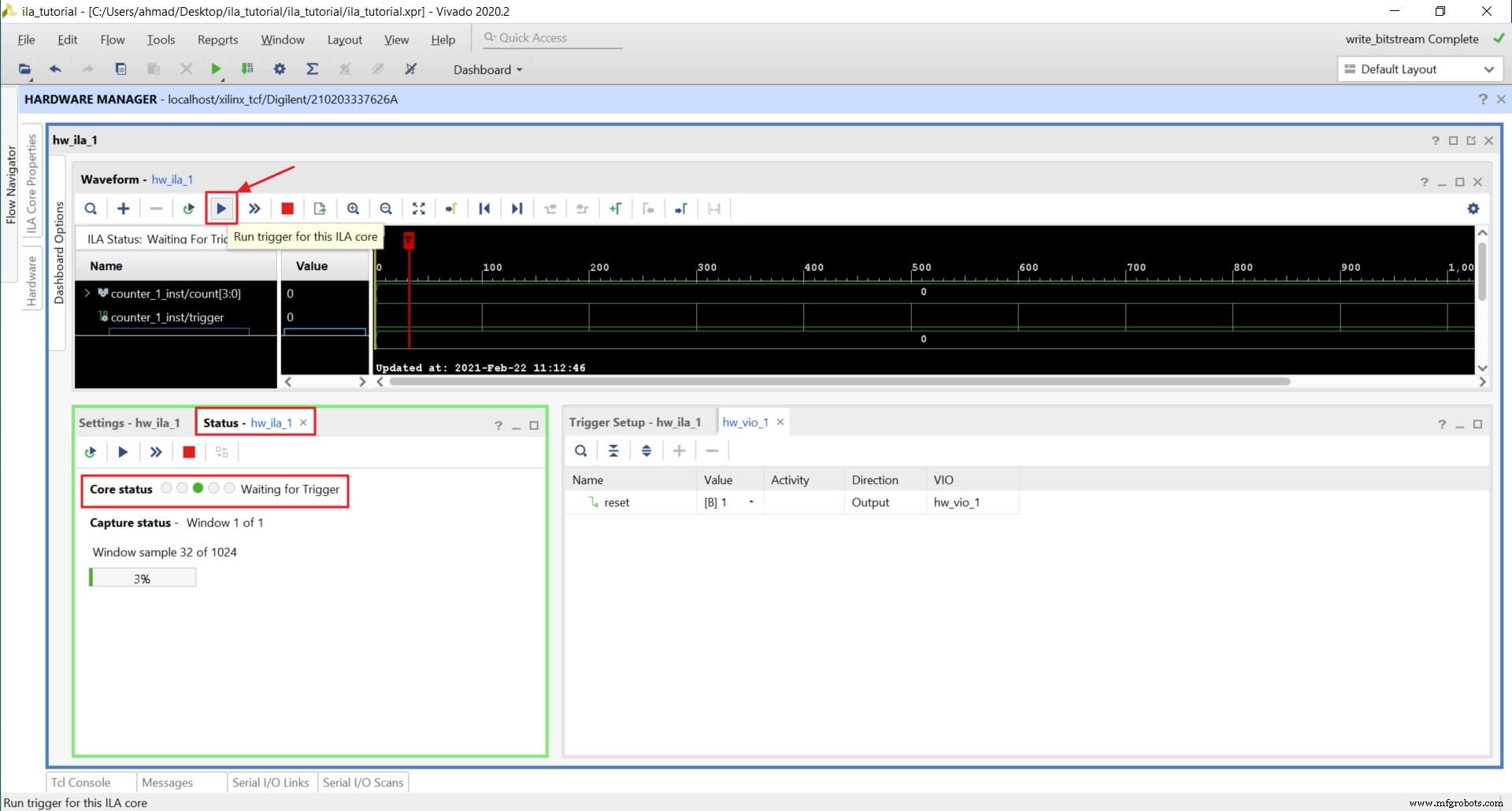

Wijzig reset terug naar 1 van vio_reset .

Klik op het venster Status hw_ila_1 . We zien dat de kernstatus Inactief is omdat er geen triggers zijn ingeschakeld. Klik op de Trigger uitvoeren knop, en dat zal de trigger activeren.

We zien nu dat de kernstatus is gewijzigd in wachten op trigger . Als de reset hoog is, is er geen activiteit op ons triggersignaal (poort trigger van counter_1_inst ), en ILA wacht.

Laten we nu de reset . wijzigen tot 0 zodat de tellers beginnen te werken.

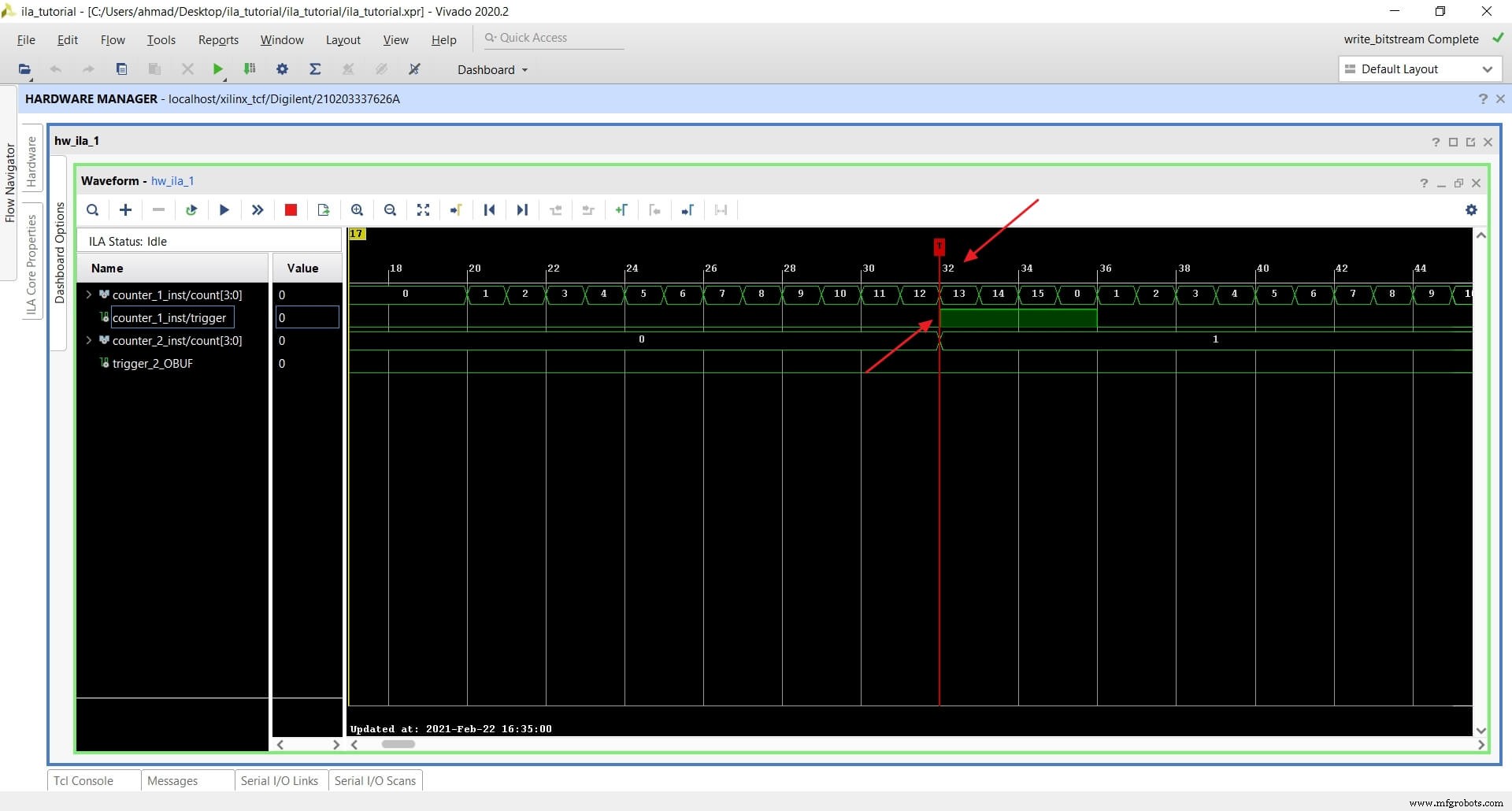

We zien nu dat de ILA is geactiveerd en de monsters heeft opgenomen, en dat de kernstatus weer is gewijzigd in Idle .

We zien de rode verticale lijn (markering) op de stijgende flank van ons triggersignaal (poort trigger van counter_1_inst ), en het staat op positie 32 . We kunnen ook verifiëren dat het signaal tellen zich correct gedraagt en het signaal counter_1_inst/trigger is hoog voor vier klokcycli tussen 12 en 15 (de output wordt vertraagd met één klokcyclus).

Als we een beetje uitzoomen, kunnen we ook het gedrag van count . verifiëren en triggeren signalen voor counter_2_inst .

ILA uitvoeren met meerdere triggers

We kunnen een combinatie van triggers gebruiken voor complexe of geavanceerde aandoeningen. Om meerdere onsamenhangende tijdframes in dezelfde golfvorm vast te leggen, kunnen we meerdere triggers gebruiken die herhaaldelijk worden geactiveerd.

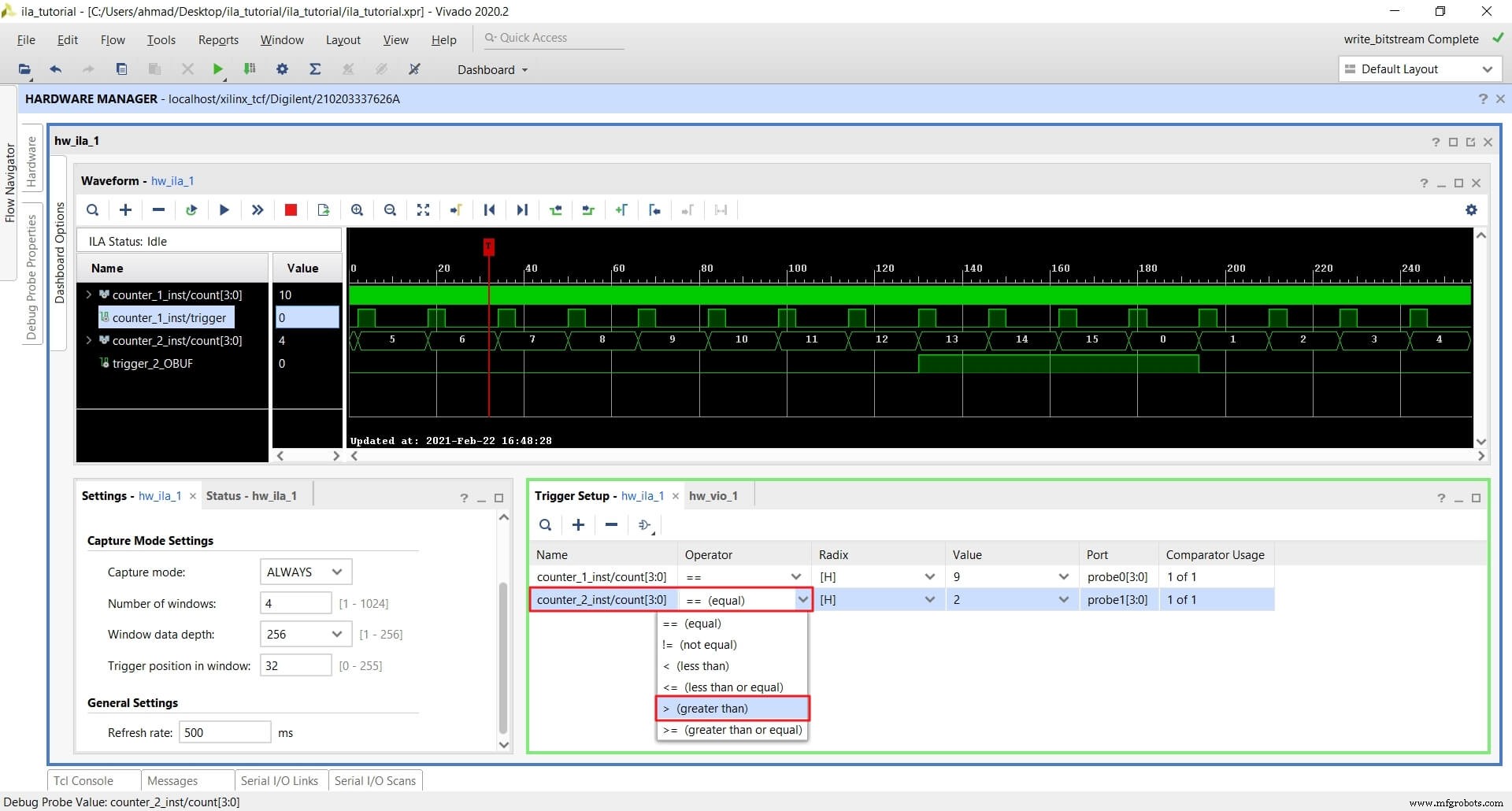

Laten we bijvoorbeeld zeggen dat we willen activeren wanneer de count signaal van counter_1_inst gelijk is aan 9 (count ==9) en wanneer de count signaal van counter_2_inst groter is dan 2 (telling> 2). Om dat te doen en de FIFO in vier tijdvensters te splitsen, volgt u deze stappen:

- Wijzig reset terug naar 1 van vio_reset

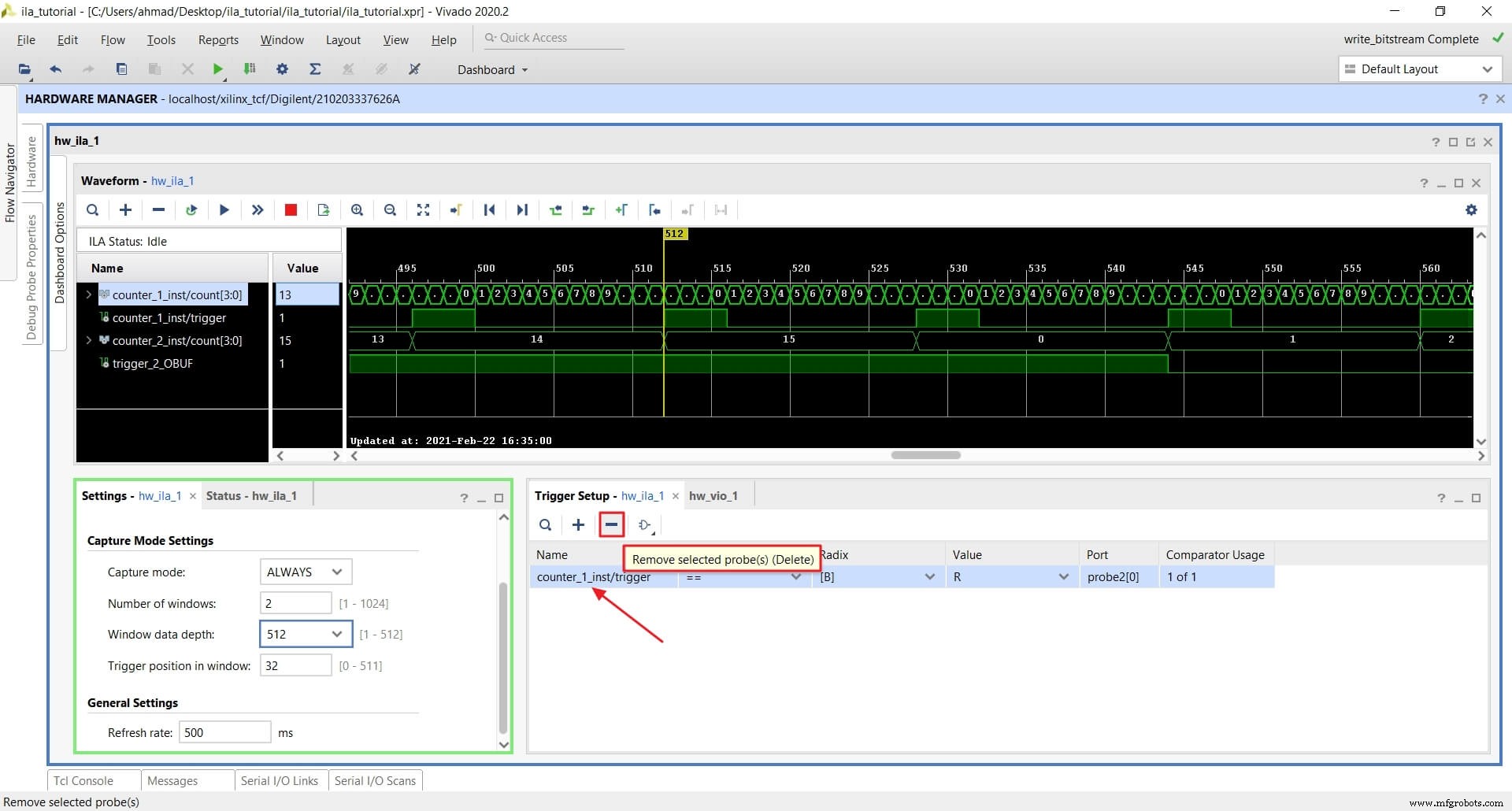

- Verwijder de vorige trigger-sonde:

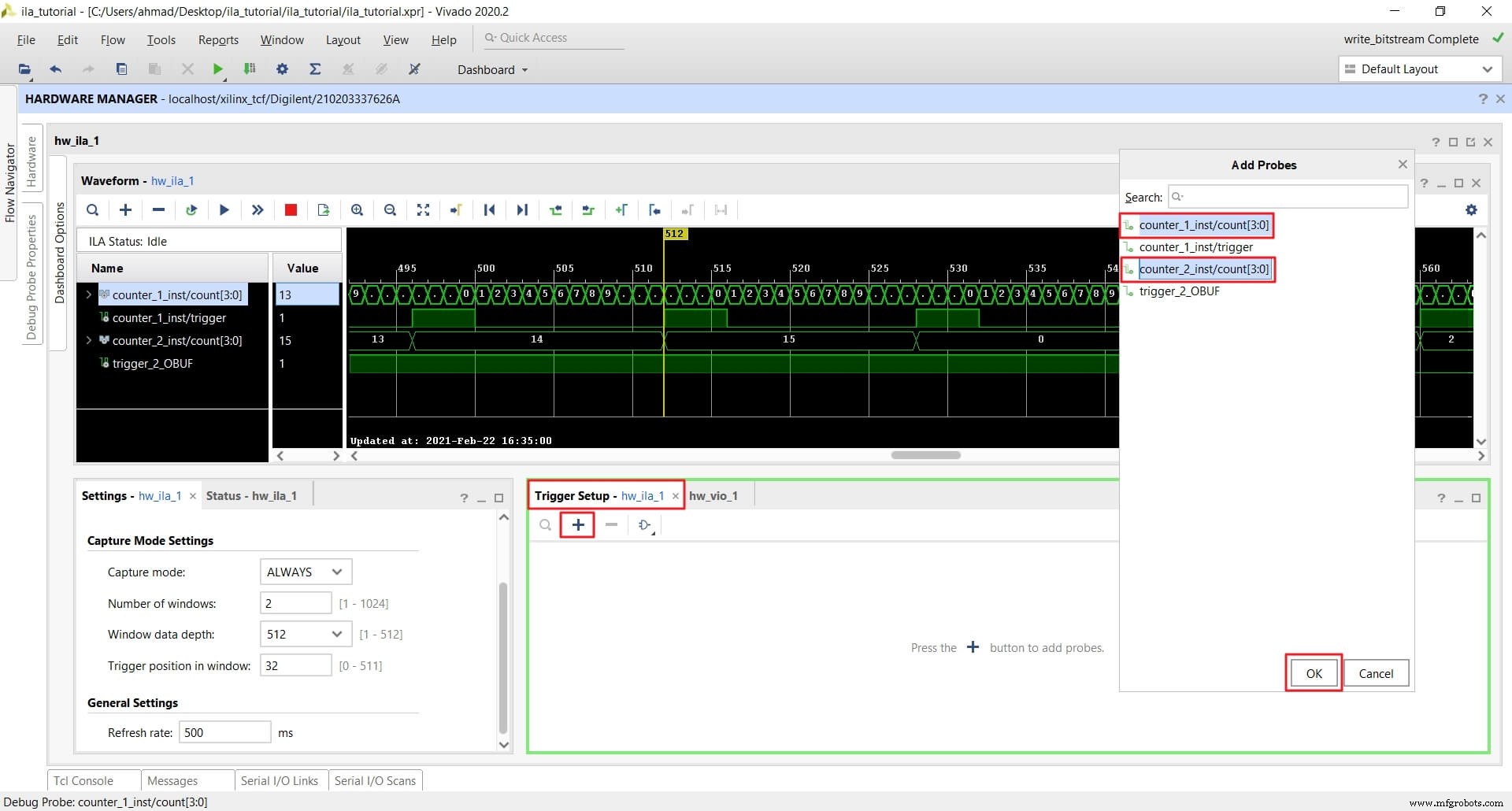

- Voeg beide tellingen toe signalen als triggers:

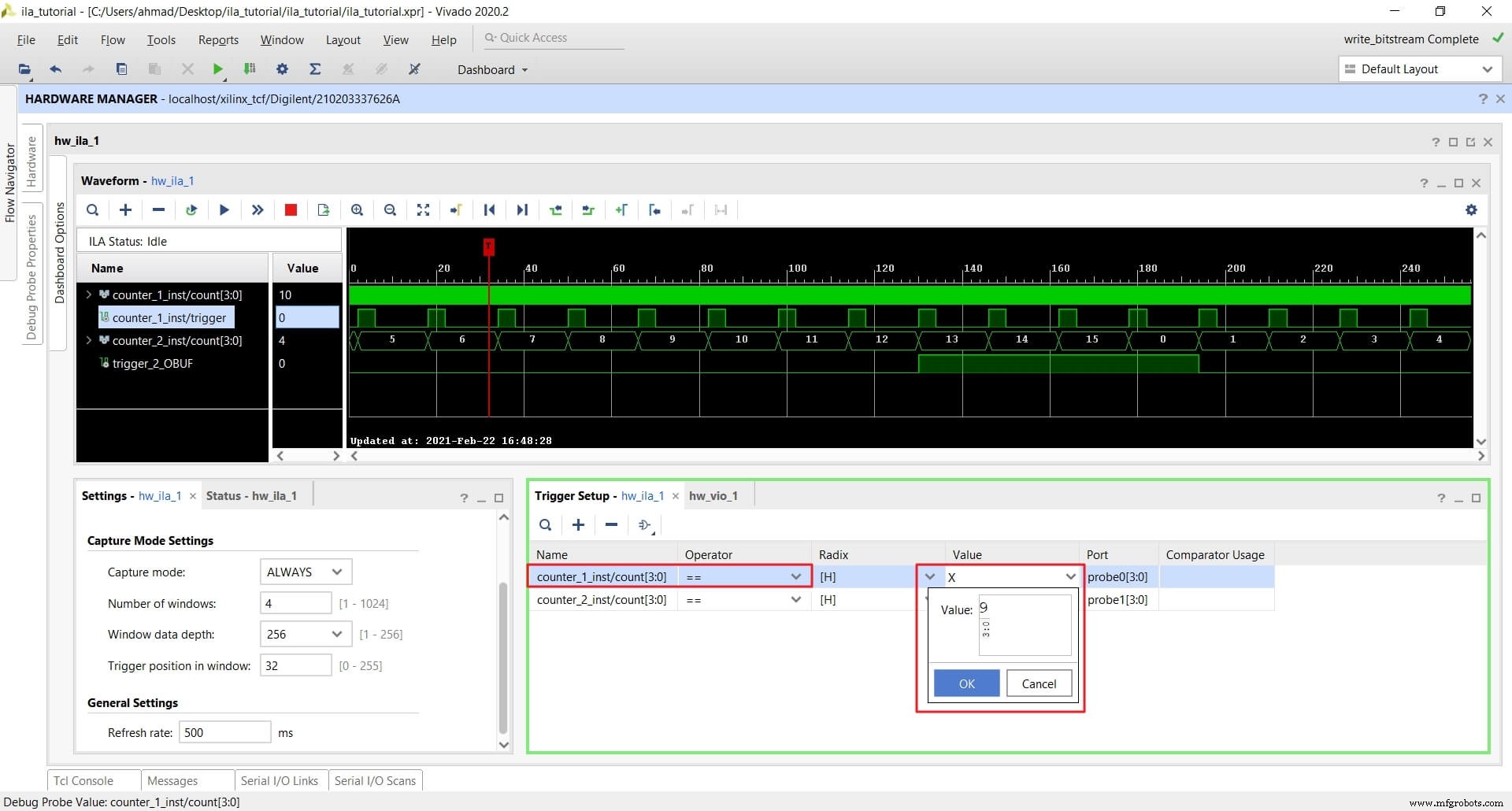

- Configureer het signaal count voor counter_1_inst tot (tel ==9):

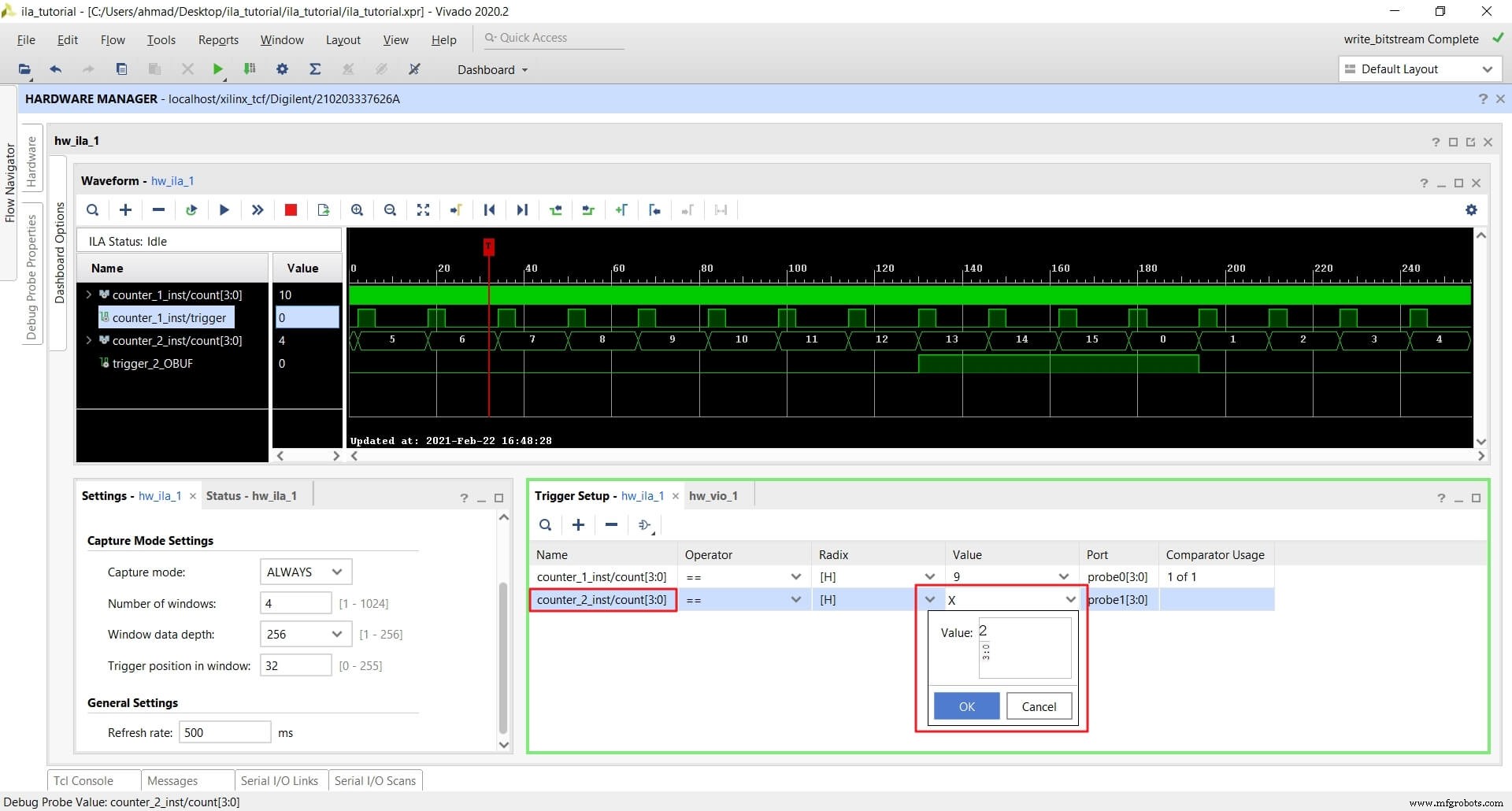

- Configureer het signaal count voor counter_2_inst tot (tel> 2):

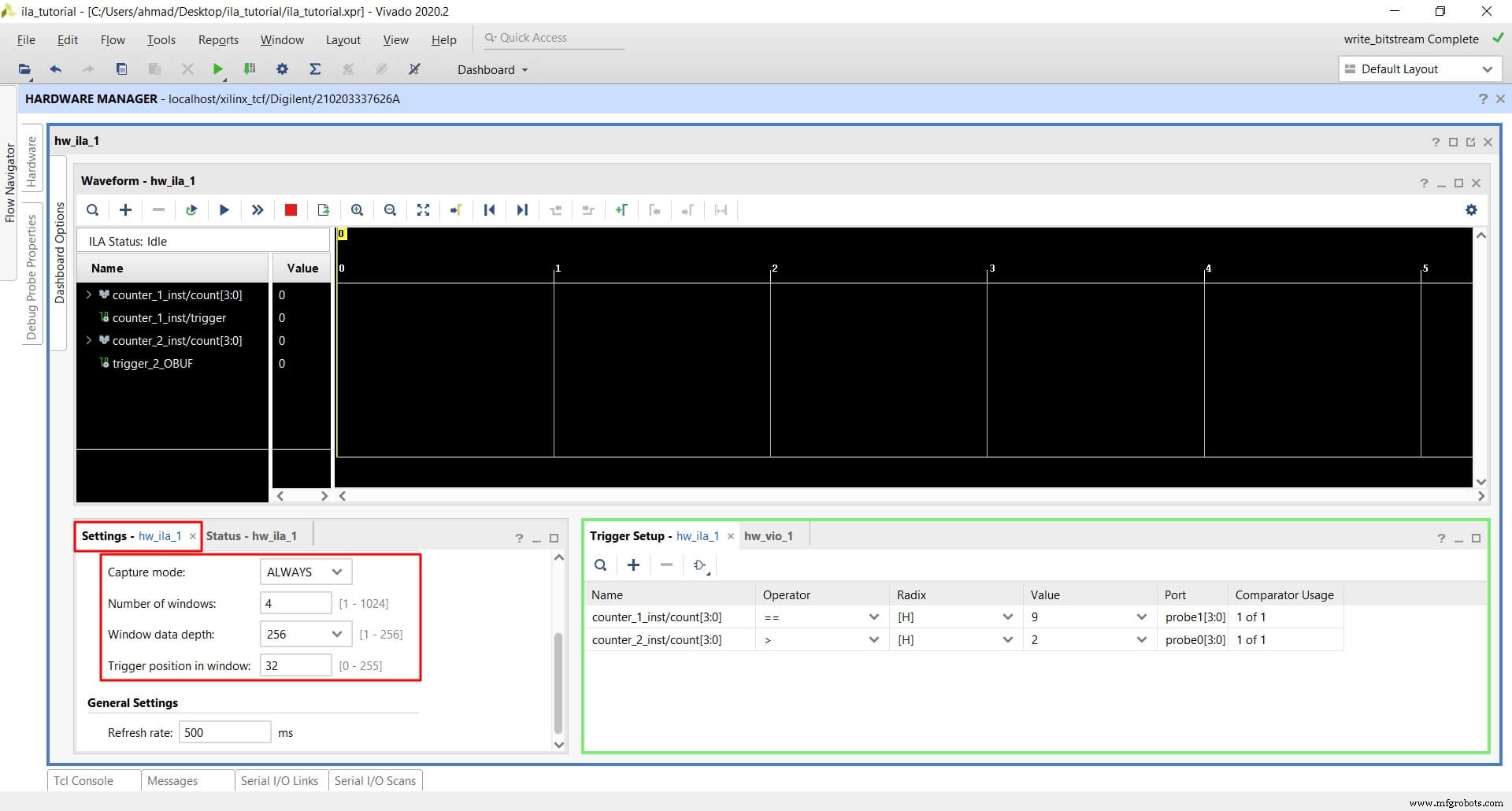

- Configureer het aantal vensters op 4 en FIFO-diepte tot 256, en positie naar 32 .

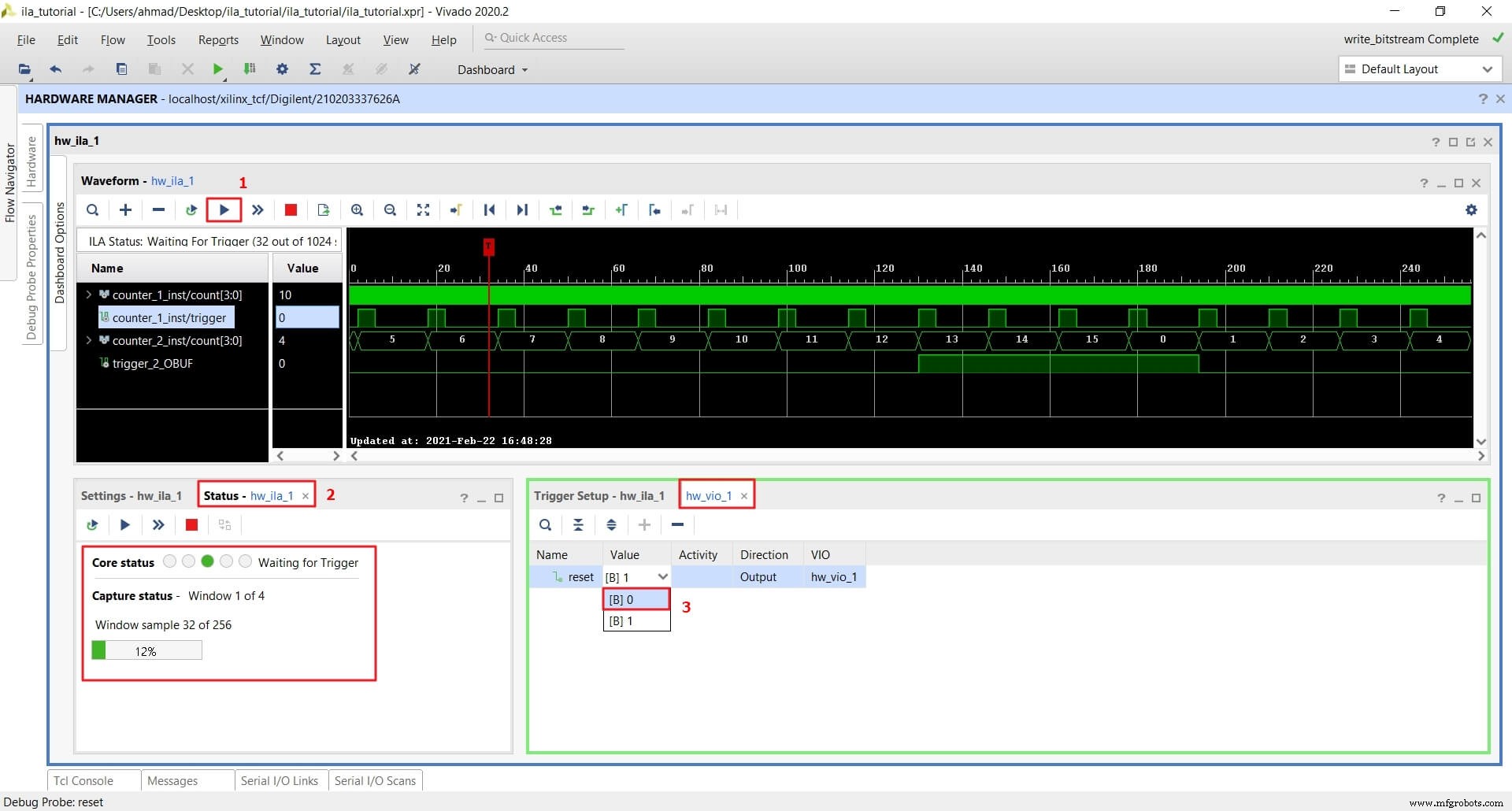

- Klik op de Trigger uitvoeren knop, en dat zal de trigger activeren. Merk op dat in het venster Status hw_ila_1 , de opnamestatus is nu venster 1 van 4 omdat we vier vensters hebben.

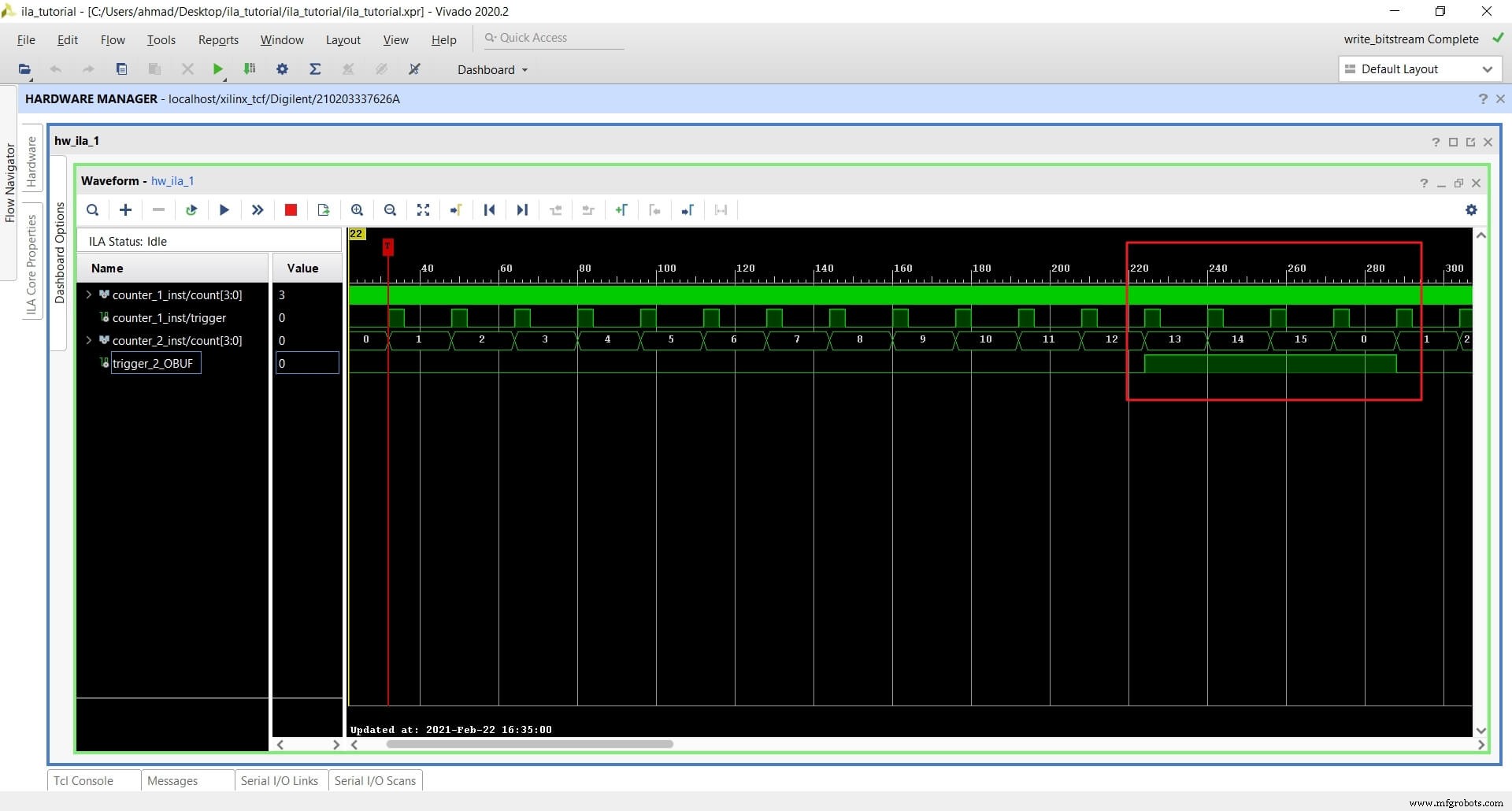

Wijzig reset terug naar 0 van vio_reset .

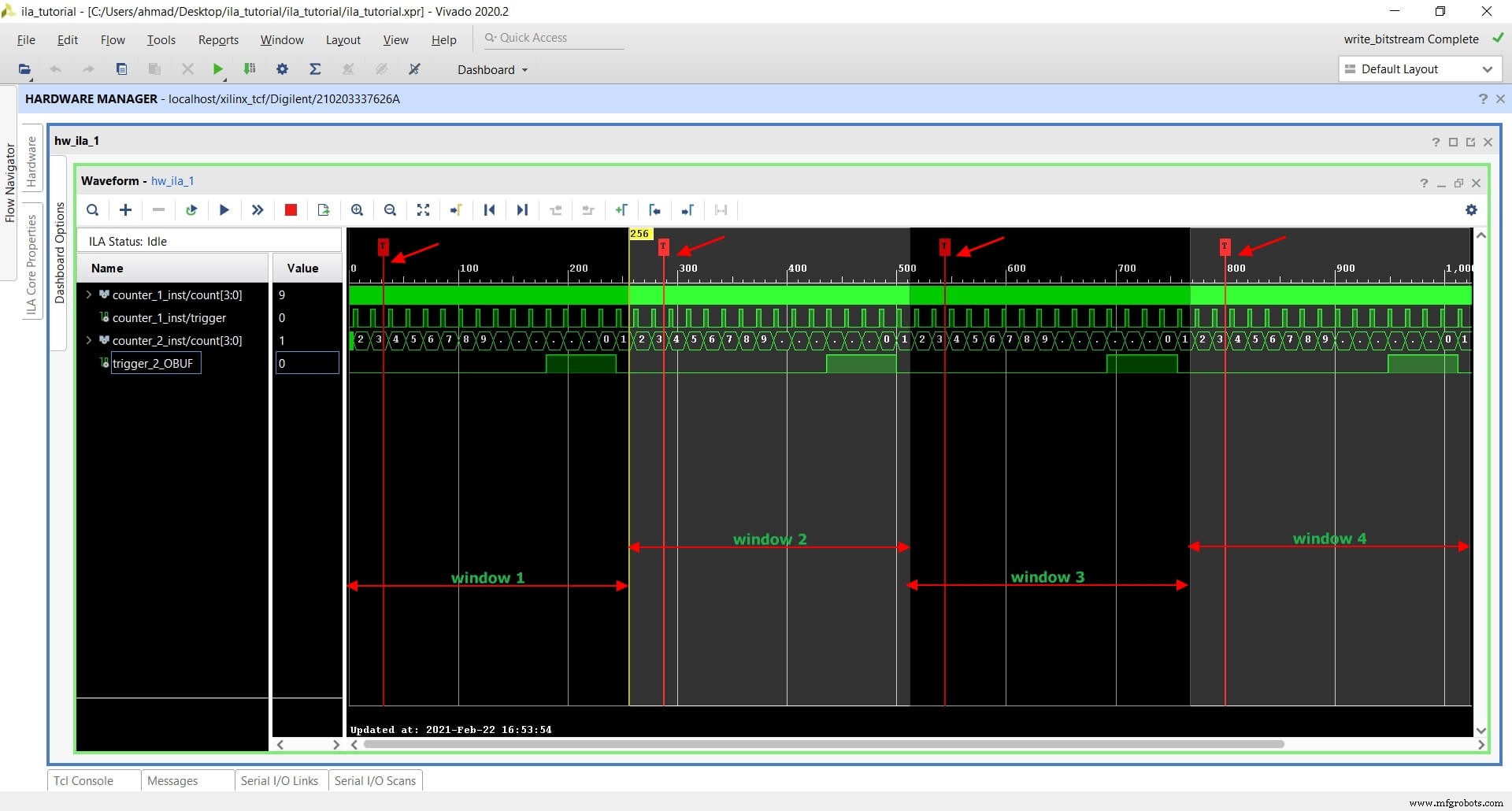

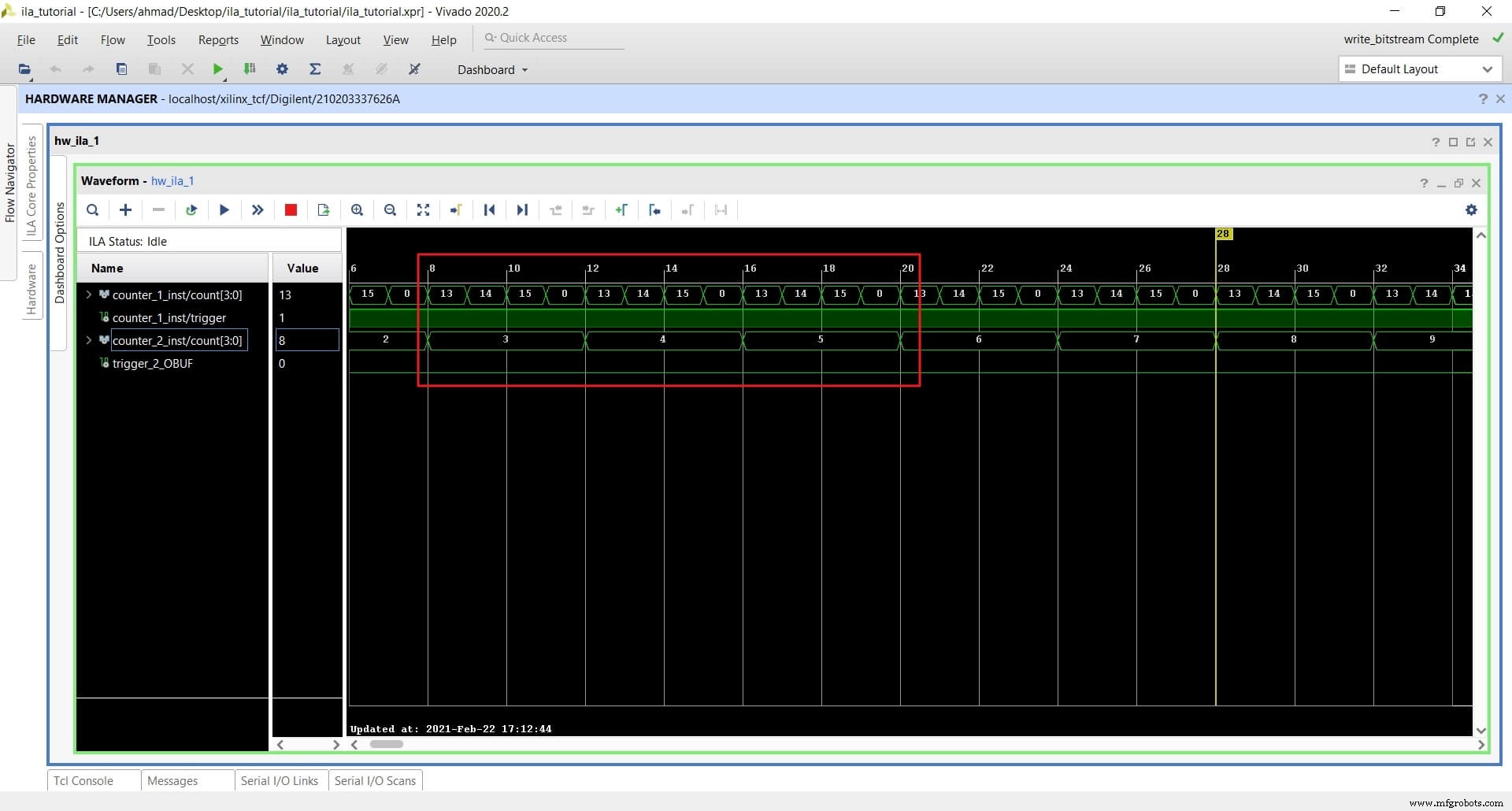

Maximaliseer het golfvormvenster. We see now that we have four windows and a trigger associated with each window. Notice that these windows are independent and not continuous.

The ILA waits for the trigger event to happen, and when it does, the ILA uses the first window to record 256 samples. It then immediately waits for the next trigger until all the windows are full.

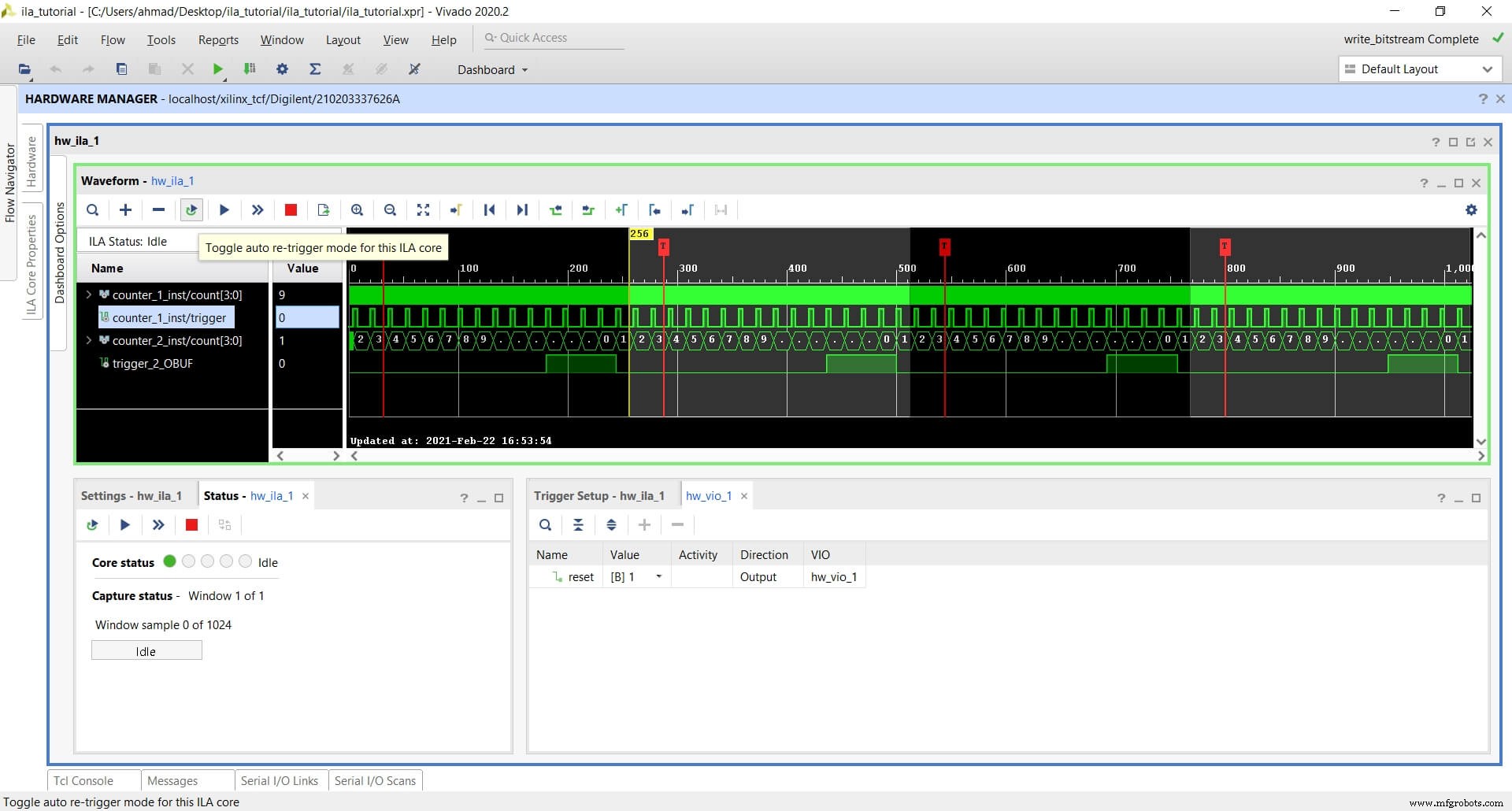

Running ILA with Auto re-trigger mode

ILA has a nice feature called Auto re-trigger that will automatically arm the trigger after it gets triggered. It is useful when monitoring events that occur seldom and you want to run a test overnight. Or you can use it when the trigger happens so often and fast that you cannot arm the trigger manually to capture the samples repeatedly.

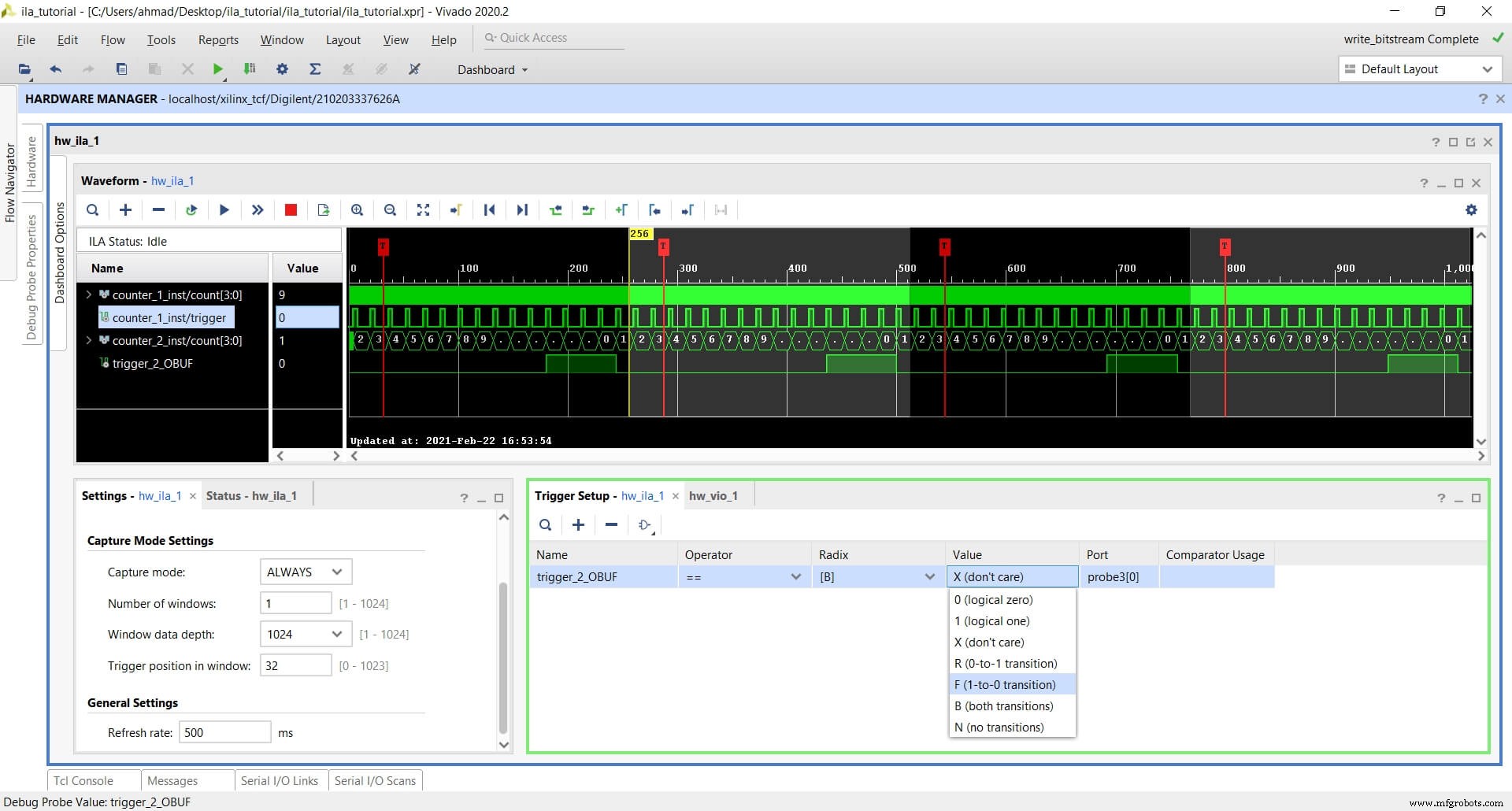

Let us assume that the output port trigger of counter_2_inst gets asserted every 3 hours, and you want to record the data each time it happens. To use the Auto trigger, follow these steps:

- Change reset back to 1 from vio_reset

- Remove the previous trigger probe

- Add trigger_2_OBUF signal as trigger:

- Configure the trigger to the condition to equal (==) and falling edge F(1-to-0 transition)

- Configure the number of windows to 1 and FIFO depth to 1024, and position to 32:

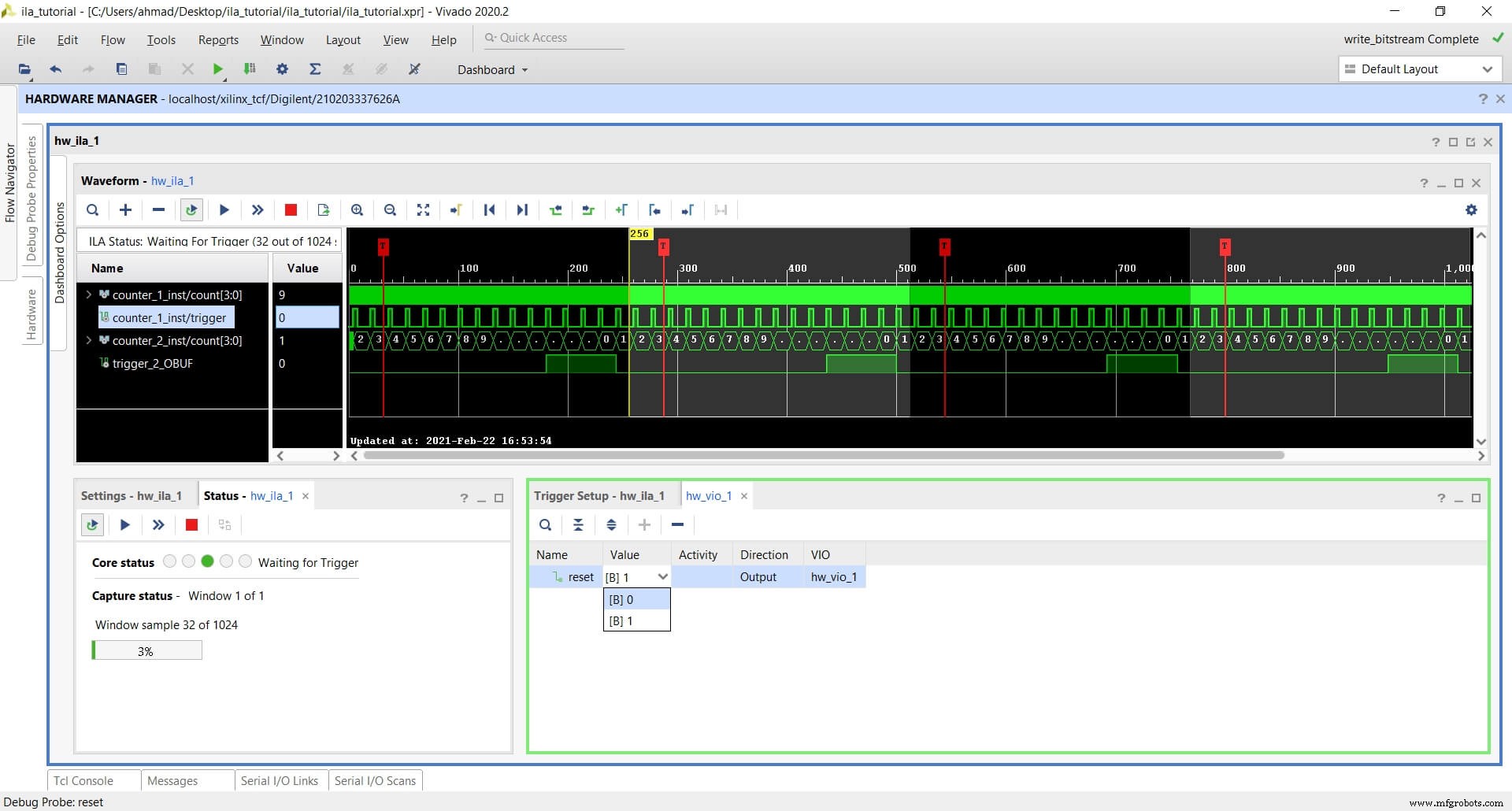

- Click on Auto re-trigger button:

- Finally, change reset back to 0 from vio_reset:

We can see now that the waveform window is getting refreshed and updated as the trigger happen. It is fast, but the behavior is noticeable.

Click on Stop trigger and toggle Auto re-trigger .

Running ILA with Capture mode

Another feature of ILA is the Capture mode . In some cases, you are not interested in recording all the data but rather capture a specific sample. Capture mode helps you filter out data and record only the samples you are interested in.

Let’s say we are only interested in sampling when the output port trigger of counter_1_inst is ‘1’ AND the output port trigger of counter_2_inst is ‘0’.

To use Capture mode to achieve this, follow these steps:

- Change reset back to 1 from vio_reset

- Remove the previous trigger probe

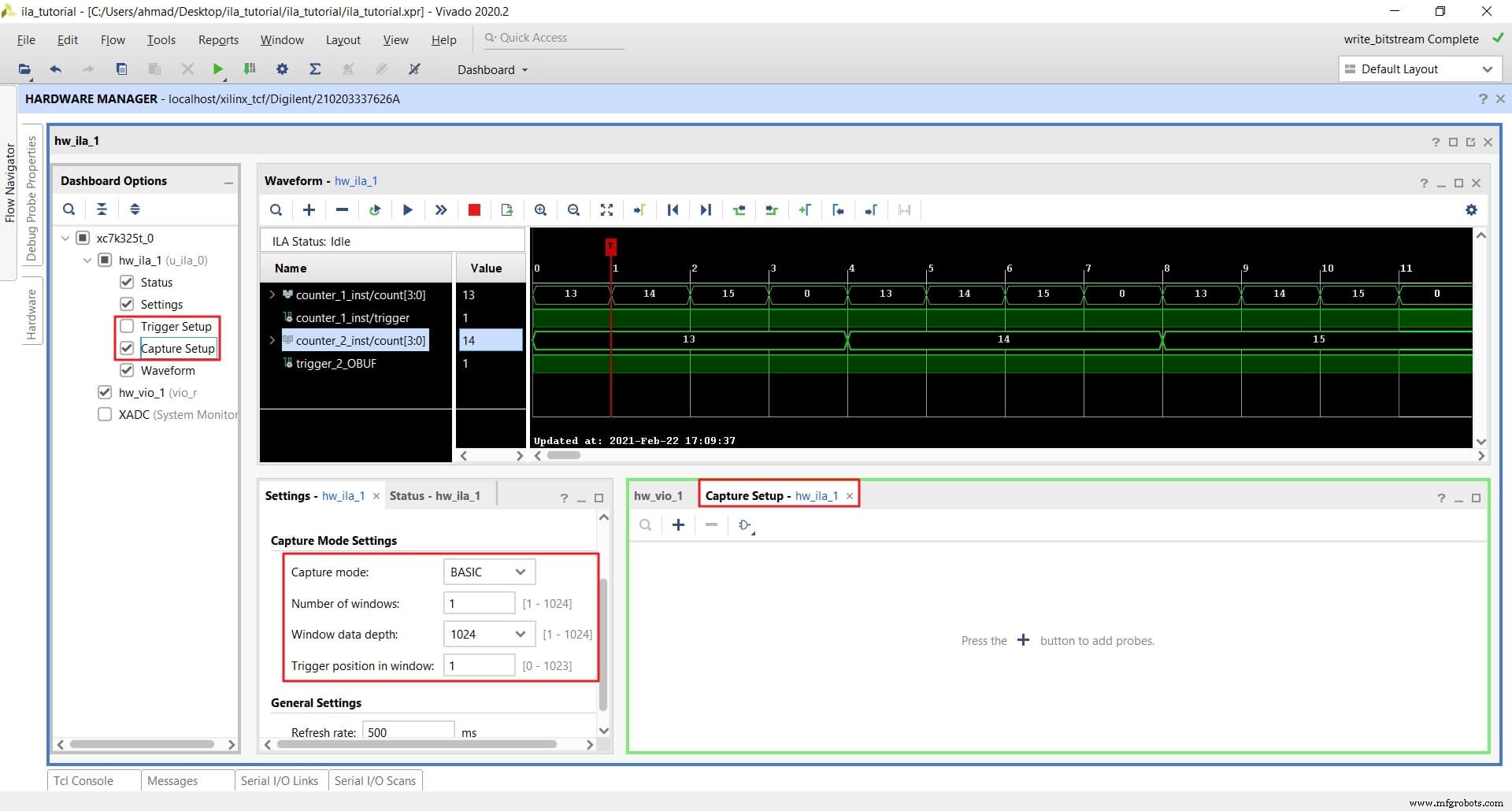

- From the dashboard, Uncheck Trigger Setup and check Capture Setup . Notice that a Capture Setup window will appear. From the Settings – hw_ila_1 window, Change Capture mode to BASIC , the window to 1, the FIFO depth to 1024, and position to 1:

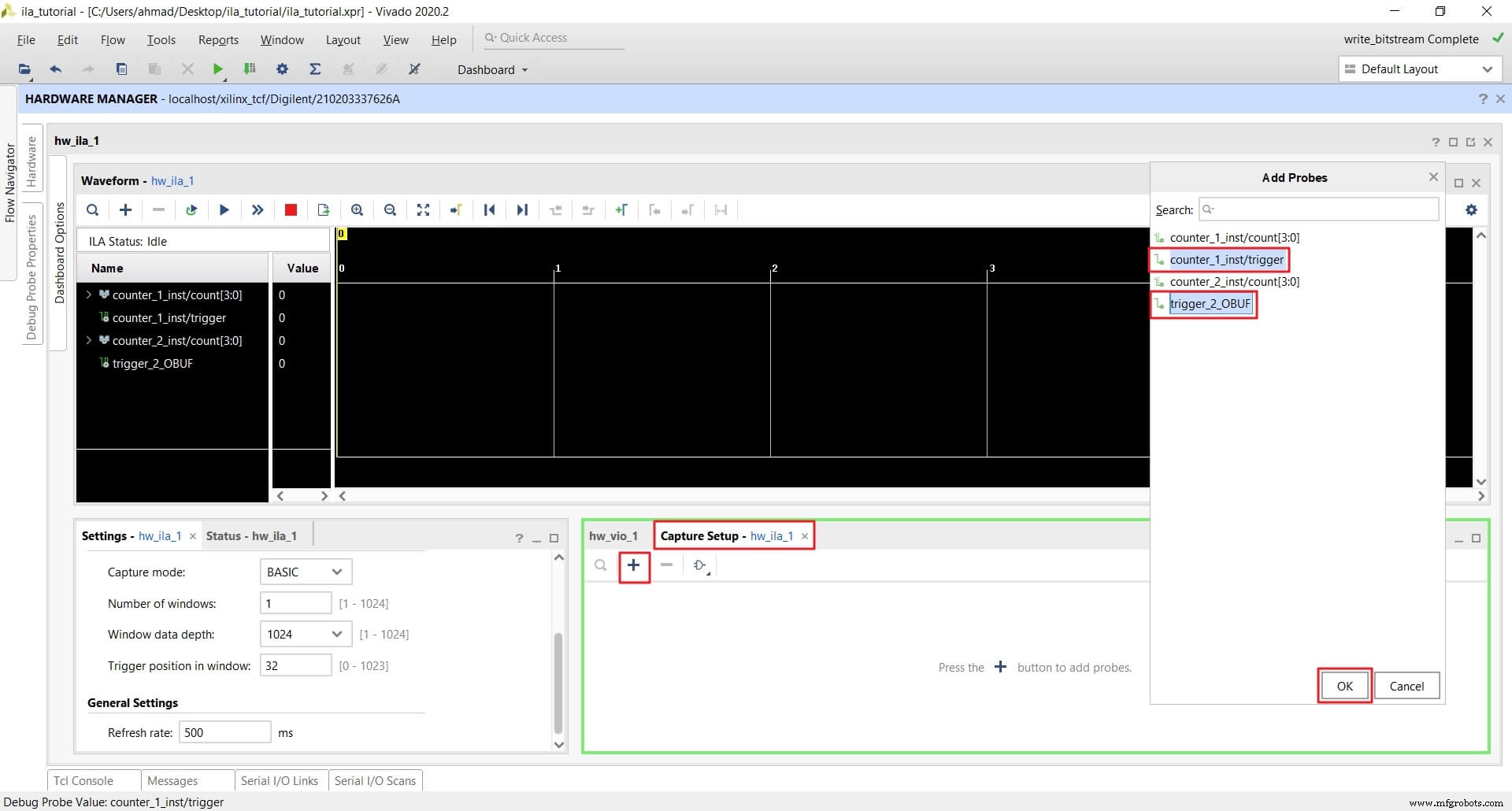

- Add trigger_2_OBUF , and counter_1_inst/trigger from the Capture Setup window:

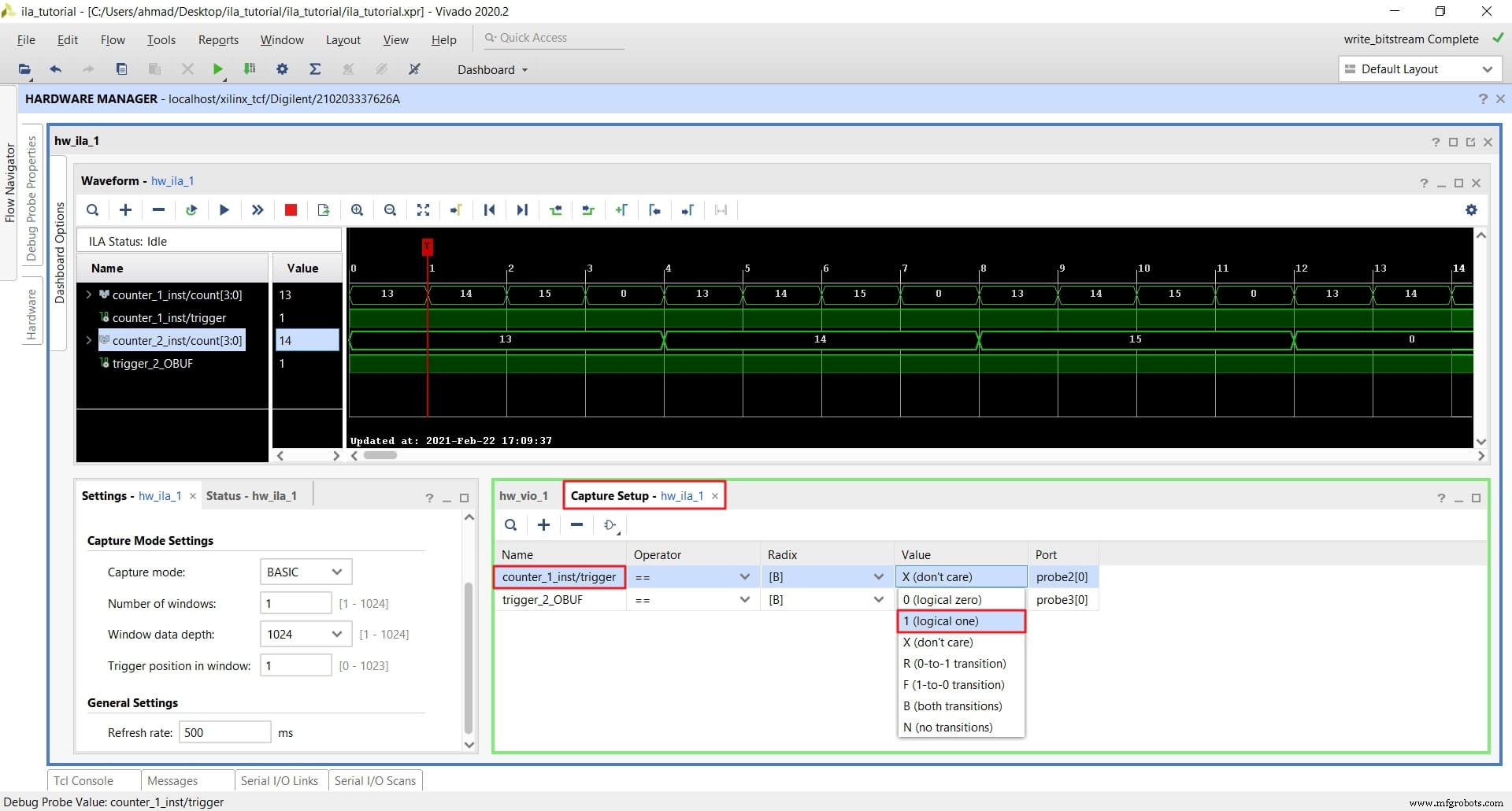

- Configure counter_1_inst/trigger to the condition equal (==) and 1 (logical one) :

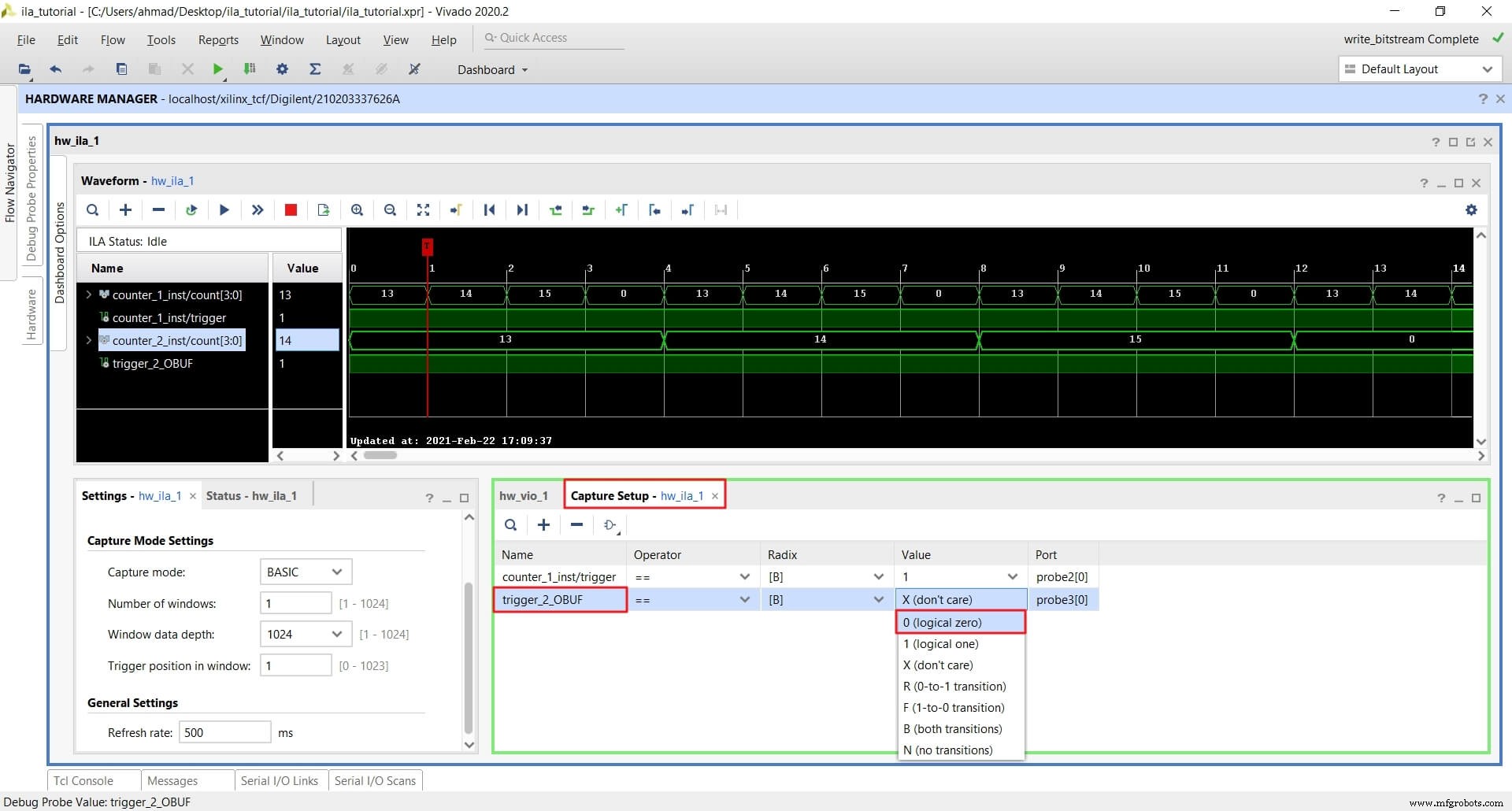

- Configure trigger_2_OBUF to the condition equal (==) and 0 (logical zero) :

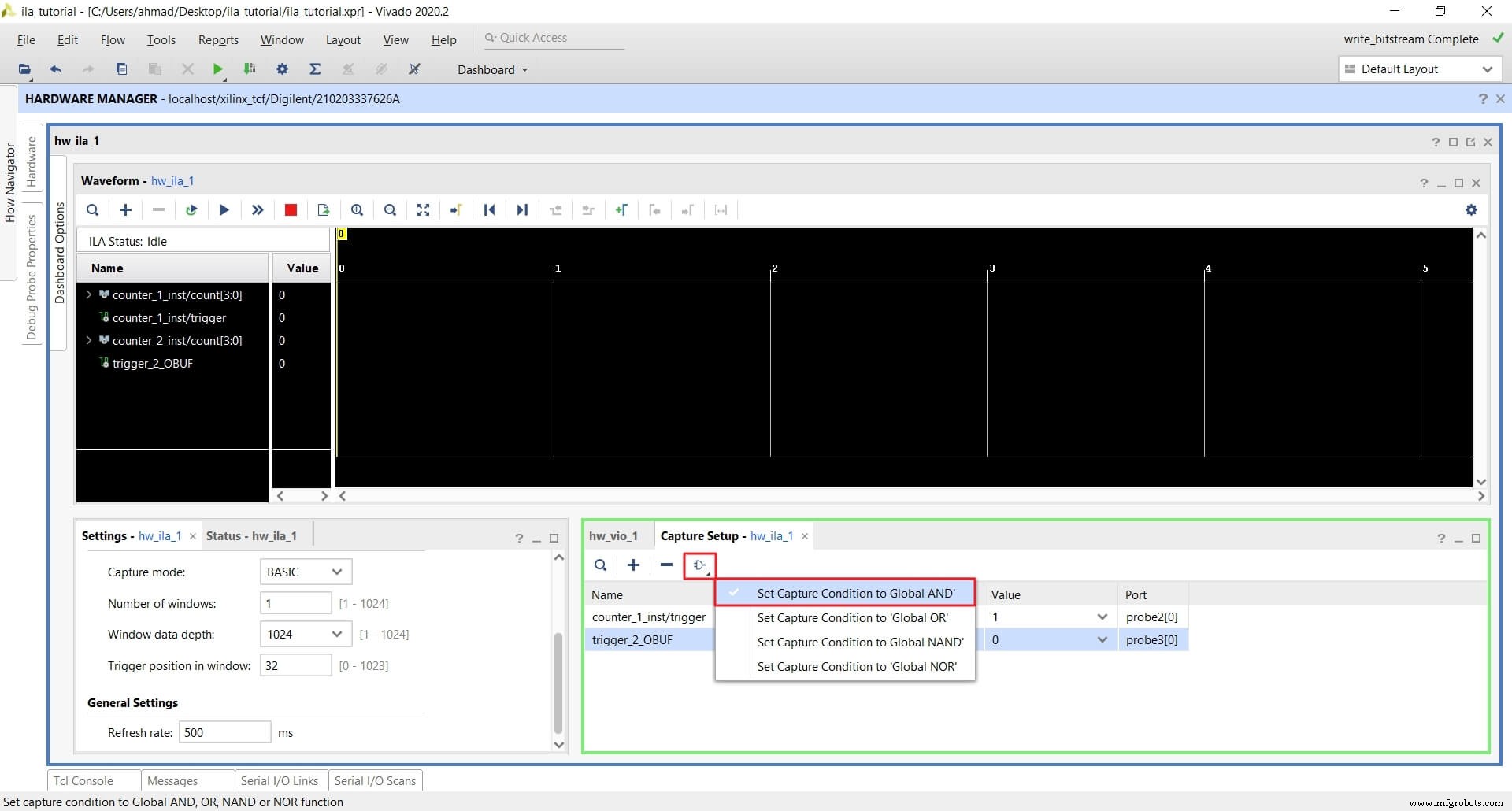

- Change the Capture Condition to Global AND :

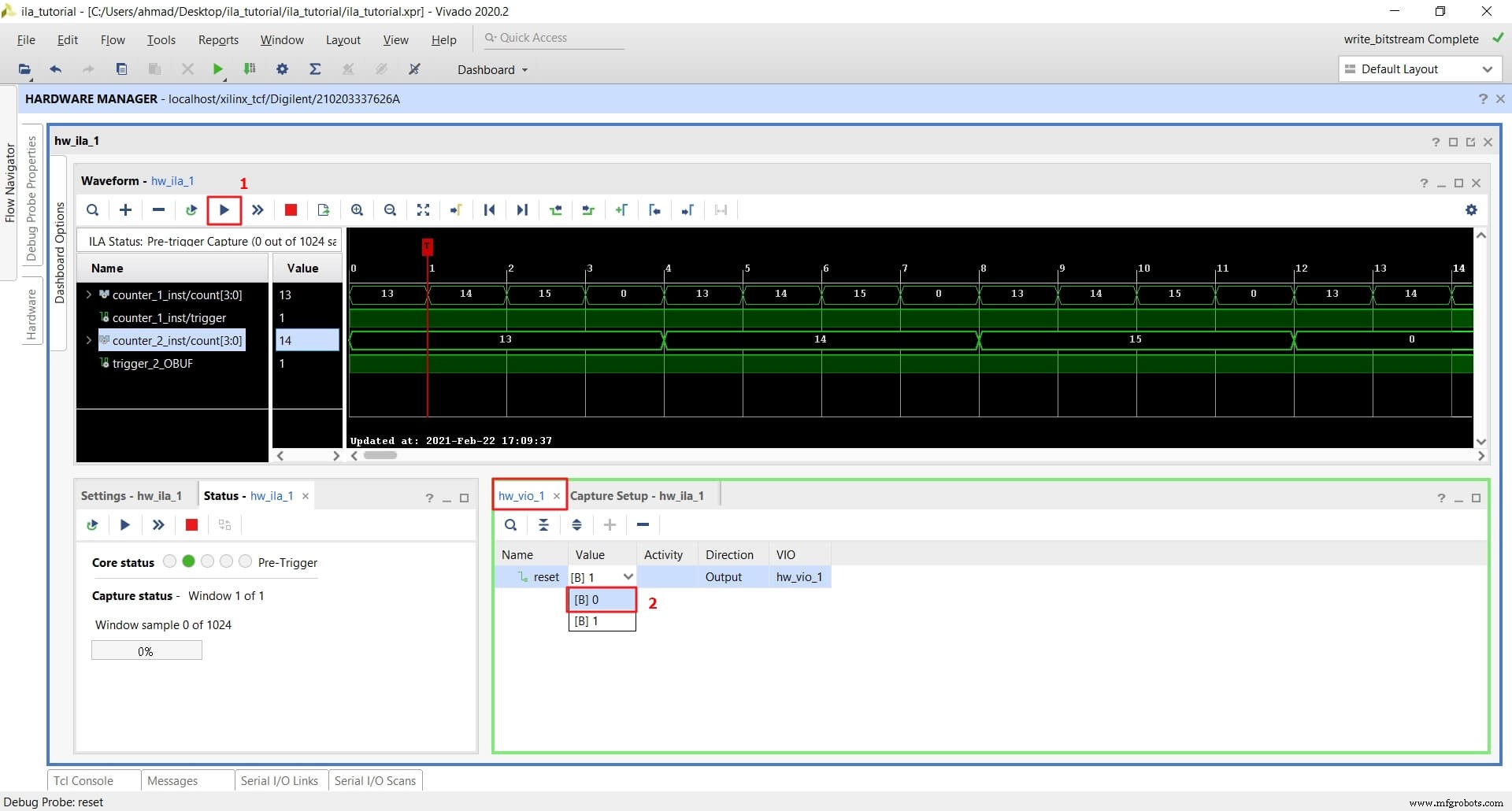

- Click on the Run trigger button and then change reset to 0 from vio_reset :

As we can see from the image below, the waveform has only recorded data when counter_1_inst’s count signal is 13, 14, 15, or 0. Any other counts are filtered out because counter_1_inst/trigger is high on these counts only.

Conclusie

In this tutorial, we learned about ILA and VIO and different use-cases for them. ILA and VIO are excellent options for on-chip debugging. They are free, easy to use, flexible, scalable, and simple yet offer advanced features. The use of multiple triggers and Capture mode helps you achieve a complex debugging scheme.

VHDL

- Tutorial - Combinatie- en sequentiële code schrijven

- Naar Cloud Infinity en verder

- C# Basisinvoer en -uitvoer

- C++ basisinvoer/uitvoer

- C Ingang Uitgang (I/O)

- Python invoer, uitvoer en import

- Java basis invoer en uitvoer

- Python- en Raspberry Pi-temperatuursensor

- D Vergrendeling

- C - Invoer en uitvoer

- RightHand Robotics en Element Logic lanceren geïntegreerde gerobotiseerde stukverzameloplossing