Variabelen - VHDL-voorbeeld

Variabelen in VHDL werken op dezelfde manier als variabelen in C. Hun waarde is geldig op de exacte locatie in de code waar de variabele is gewijzigd. Daarom, als een signaal de waarde van de variabele voor . gebruikt de toewijzing, zal deze de oude variabele waarde hebben. Als een signaal de waarde gebruikt van de variabele na de toewijzing zal het de nieuwe variabele waarde hebben.

Variabelenregels:

- Variabelen kunnen alleen binnen processen worden gebruikt

- Elke variabele die in het ene proces is gemaakt, kan niet in een ander proces worden gebruikt

- Variabelen moeten worden gedefinieerd na het trefwoord proces maar voordat het zoekwoord begin

- Variabelen worden toegewezen met de := toewijzingssymbool

- Variabelen die worden toegewezen krijgen onmiddellijk de waarde van de toewijzing

Het belangrijkste om te begrijpen is dat variabelen onmiddellijk de waarde van hun toewijzing aannemen. Hier is een voorbeeld dat een handige manier laat zien om variabelen te gebruiken:gegevens opslaan voor tijdelijk gebruik . Het gebruikt een case-statement en de en-teken (&) aaneenschakelingsoperator.

VAR_CASE : process (i_clk)

variable v_Choices : std_logic_vector(1 downto 0);

begin

v_Choices := i_select_1 & i_select_2; -- concatenation

case v_Choices is

when "00" =>

o_data <= "0001";

when "01" =>

o_data <= "0010";

-- ETC

In het vorige voorbeeld hebben we de twee signalen aaneengeschakeld zodat ze in de case-statement konden worden gebruikt. De variabele v_Choices was direct beschikbaar voor gebruik zodra deze was toegewezen. Laten we naar een ander voorbeeld kijken. Het onderstaande voorbeeld is uitgebreider en laat zien hoe variabelen onmiddellijk de waarde van hun toewijzing krijgen. De signalen r_Var_Copy1 en r_Var_Copy2 lijken hetzelfde te zijn, maar r_Var_Copy2 kan nooit op 5 komen voordat het wordt gereset.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity variable_ex is

port (

i_clk : in std_logic;

o_done : out std_logic

);

end variable_ex;

architecture rtl of variable_ex is

signal r_Done : std_logic := '0';

signal r_Var_Copy1 : natural range 0 to 5 := 0;

signal r_Var_Copy2 : natural range 0 to 5 := 0;

begin

EX_VAR : process (i_clk)

variable v_Count : natural range 0 to 5 := 0;

begin

if rising_edge(i_clk) then

v_Count := v_Count + 1;

r_Var_Copy1 <= v_Count;

if v_Count = 5 then

r_Done <= '1';

v_Count := 0;

else

r_Done <= '0';

end if;

r_Var_Copy2 <= v_Count;

end if;

end process EX_VAR;

o_done <= r_Done;

end rtl;

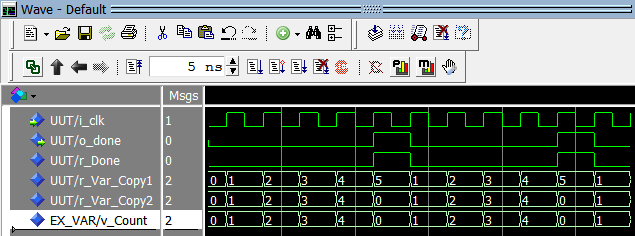

Om ons ontwerp te simuleren, moeten we een testbank maken. Ook kunnen variabelen een beetje lastig zijn om in simulatie weer te geven. Als je Modelsim gebruikt, lees dan meer over hoe je je variabelen kunt zien in het golfvormvenster van Modelsim.

Testbank:

library ieee;

use ieee.std_logic_1164.all;

entity variable_ex_tb is

end variable_ex_tb;

architecture behave of variable_ex_tb is

component variable_ex

port (

i_clk : in std_logic;

o_done : out std_logic

);

end component variable_ex;

constant c_CLK_PERIOD : time := 10 ns;

signal r_CLK : std_logic := '0';

signal w_DONE : std_logic;

begin

UUT : variable_ex

port map (

i_clk => r_CLK,

o_done => w_DONE

);

r_CLK <= not r_CLK after c_CLK_PERIOD/2;

end behave;

Variabelen Voorbeeld testbank-golfvorm

Variabelen Voorbeeld testbank-golfvorm Het bovenstaande voorbeeld laat zien hoe variabelen anders werken dan signalen. De signalen r_Var_Copy1 en r_Var_Copy2 lijken hetzelfde te zijn, maar r_Var_Copy2 kan nooit op 5 komen voordat het wordt gereset.

VHDL

- Procedureverklaring - VHDL-voorbeeld

- Records - VHDL-voorbeeld

- Analyse-opties

- C#-variabelen en (primitieve) gegevenstypen

- C++ variabelen, literalen en constanten

- C Variabelen, constanten en literalen

- C opslagklasse

- Strings in C:variabele declareren, initialiseren, afdrukken, voorbeeld

- Java - Variabele Types

- C - Variabelen

- Variabel bereik in C++