Hoe het meest voorkomende VHDL-type te gebruiken:std_logic

Het meest gebruikte type in VHDL is de std_logic . Zie dit type als een enkele bit, de digitale informatie die wordt gedragen door een enkele fysieke draad. De std_logic geeft ons een meer fijnmazige controle over de bronnen in ons ontwerp dan de integer type, dat we in de vorige tutorials hebben gebruikt.

Normaal gesproken willen we dat een draad in een digitale interface de waarde '1' . heeft of '0' . Deze twee waarden zijn de enige waarden die een bit, een binair cijfer, kan hebben. Maar in werkelijkheid kan een fysiek digitaal signaal zich in een aantal toestanden bevinden, die de std_logic type kan goed emuleren. Daarom is het het meest gebruikte type in VHDL.

Deze blogpost maakt deel uit van de serie Basic VHDL Tutorials.

De std_logic type kan de volgende waarden hebben:

| ‘1’ | Logica 1 |

| '0' | Logica 0 |

| 'Z' | Hoge impedantie |

| ‘W’ | Zwak signaal, weet niet of 0 of 1 |

| 'L' | Zwak 0, pulldown |

| 'H' | Zwak 1, pull-up |

| ‘-‘ | Maakt niet uit |

| 'U' | Niet geïnitialiseerd |

| 'X' | Onbekend, meerdere stuurprogramma's |

Dit lijkt misschien een heleboel verschillende toestanden voor een type dat verondersteld wordt een enkele binaire waarde te modelleren. Maak je geen zorgen, we zullen niet al deze typen gebruiken in deze tutorialserie. We gebruiken '1' en '0' natuurlijk. En we zullen ook 'U' . zien en 'X' , waarmee we fouten in ons ontwerp kunnen opsporen. De andere waarden zijn geavanceerde VHDL-functies die kunnen worden gebruikt voor zaken als het modelleren van communicatie met bijvoorbeeld I

2

C-apparaten, of voor het maken van tri-state bussen.

Als verschillende processen verschillende waarden naar een signaal proberen te schrijven, zeggen we dat het meerdere stuurprogramma's heeft . Als een std_logic signaal meerdere stuurprogramma's heeft, zal het geen compilatie- of runtime-fout zijn, althans niet in de simulator. Dat komt omdat std_logic is een opgelost type , wat betekent dat de waarde wordt bepaald door een resolutiefunctie.

De waarde van een std_logic signaal met twee drivers wordt bepaald op basis van deze resolutietabel:

| U | X | 0 | 1 | Z | W | L | H | – | |

|---|---|---|---|---|---|---|---|---|---|

| U | X | X | 1 | 1 | 1 | 1 | 1 | X | 1 |

| U | X | 0 | X | 0 | 0 | 0 | 0 | X | 0 |

| U | U | U | U | U | U | U | U | U | U |

| U | X | X | X | X | X | X | X | X | X |

| U | X | 0 | 1 | Z | W | L | H | X | Z |

| U | X | 0 | 1 | W | W | W | W | X | W |

| U | X | 0 | 1 | L | W | L | W | X | L |

| U | X | 0 | 1 | H | W | W | H | X | H |

| U | X | X | X | X | X | X | X | X | – |

Oefening

In deze video-tutorial leren we hoe u declare en show std_logic . kunt gebruiken signalen in een golfvorm:

De laatste code die we in deze tutorial hebben gemaakt:

library ieee;

use ieee.std_logic_1164.all;

entity T10_StdLogicTb is

end entity;

architecture sim of T10_StdLogicTb is

signal Signal1 : std_logic := '0';

signal Signal2 : std_logic;

signal Signal3 : std_logic;

begin

process is

begin

wait for 10 ns;

Signal1 <= not Signal1;

end process;

-- Driver A

process is

begin

Signal2 <= 'Z';

Signal3 <= '0';

wait;

end process;

-- Driver B

process(Signal1) is

begin

if Signal1 = '0' then

Signal2 <= 'Z';

Signal3 <= 'Z';

else

Signal2 <= '1';

Signal3 <= '1';

end if;

end process;

end architecture;

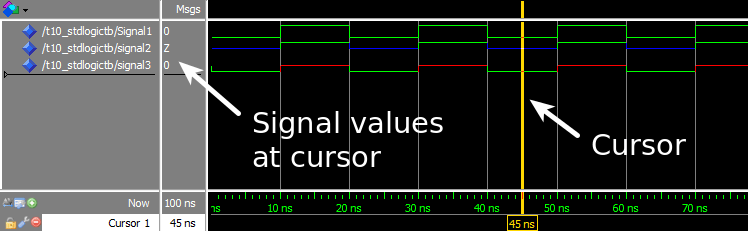

Het golfvormvenster in ModelSim nadat we op run hebben gedrukt en ingezoomd op de tijdlijn:

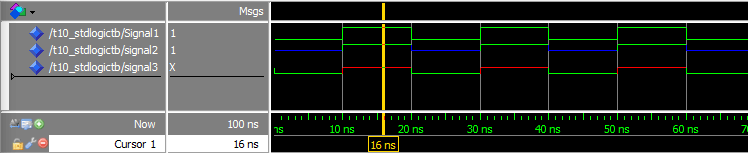

De golfvorm met de cursor op het andere deel van de herhalende signaalcyclus:

Analyse

De oefening demonstreerde hoe de resolutiefunctie van VHDL werkt met de std_logic type. Bij het werken met digitale logica is het vaak praktischer om de tijdlijn in een golfvorm te bestuderen in plaats van afdrukken te gebruiken. Daarom hebben we de ModelSim-golfvorm gebruikt om de signaalwaarden in deze oefening te controleren.

Het eerste proces en Signal1 wordt alleen gebruikt voor het wijzigen van de waarde die het derde proces stuurt op Signal2 en Signal3 .

Het tweede proces, Driver A, zal proberen een 'Z' . te besturen op Signal2 , en een '0' op Signal3 constant.

Het derde proces, Bestuurder B, zal afwisselend rijden met '1' en 'Z' op beide Signal2 en Signal3 .

We zien in de golfvorm-screenshots dat Signal1 verandert tussen '0' en '1' , omdat er maar één proces is dat dit signaal probeert aan te sturen. We kunnen ook zien dat de signalen van meerdere stuurprogramma's zijn opgelost volgens de resolutietabel die is geplaatst in de opmerkingen over de VHDL-code:

| Signaal | Bestuurder A | Bestuurder B | Resultaat |

|---|---|---|---|

| Signaal2 | ‘Z’ | ‘Z’ | ‘Z’ |

| Signaal2 | ‘Z’ | ‘1’ | ‘1’ |

| Signaal3 | '0' | ‘Z’ | '0' |

| Signaal3 | '0' | ‘1’ | ‘X’ |

Afhaalmaaltijden

std_logicis het meest voorkomende type dat wordt gebruikt om een enkele bitwaarde in VHDL vast te houden- Denk aan een

std_logicsignaal als een fysieke draad in ons digitale ontwerp - Als meerdere processen een

std_logicproberen aan te sturen signaal, wordt de waarde bepaald door een resolutietabel

Ga naar de volgende tutorial »

VHDL

- De meest voorkomende knelpunten in de 3D-printworkflow - en hoe u ze kunt oplossen

- De meest voorkomende problemen met het autokoelsysteem

- Hoe u het meeste uit uw gegevens haalt

- Een gekoppelde lijst maken in VHDL

- Een procedure gebruiken in een proces in VHDL

- Een onzuivere functie gebruiken in VHDL

- Een functie gebruiken in VHDL

- Een procedure gebruiken in VHDL

- Hoe u veilig een motortakel op de werkplek kunt gebruiken?

- De meest voorkomende oorzaken van kraanongevallen (en hoe ze te vermijden)

- De meest voorkomende toepassingen van a286