Asynchrone tellers

In het vorige gedeelte zagen we een circuit met één JK-flip-flop die achteruit telde in een binaire reeks van twee bits, van 11 tot 10 tot 01 tot 00.

Aangezien het wenselijk zou zijn om een circuit te hebben dat vooruit kan tellen en niet alleen achteruit, het zou de moeite waard zijn om een voorwaartse telreeks opnieuw te onderzoeken en te zoeken naar meer patronen die zouden kunnen aangeven hoe zo'n circuit moet worden gebouwd.

Omdat we weten dat binaire telreeksen een patroon van octaaf (factor 2) frequentiedeling volgen, en dat JK flip-flop multivibrators die zijn ingesteld voor de "toggle" -modus in staat zijn om dit type frequentiedeling uit te voeren, kunnen we ons een circuit voorstellen samengesteld uit verschillende JK-flip-flops, in cascade geschakeld om vier bits output te produceren.

Het grootste probleem waarmee we worden geconfronteerd, is om te bepalen hoe om deze flip-flops met elkaar te verbinden zodat ze op het juiste moment schakelen om de juiste binaire reeks te produceren.

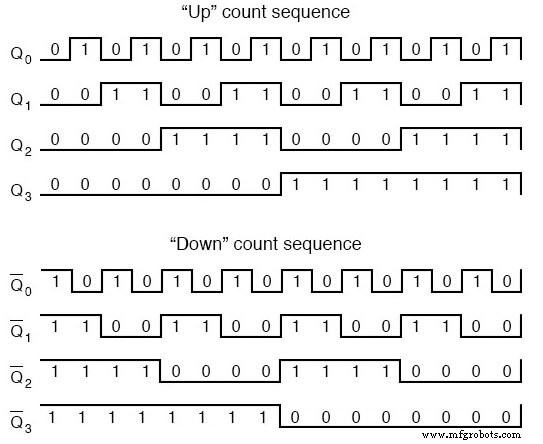

Bestudeer de volgende reeks van binaire tellingen, let op patronen die voorafgaan aan het "wisselen" van een bit tussen 0 en 1:

Merk op dat elk bit in deze reeks van vier bits wisselt wanneer het bit ervoor (de bit met een kleinere betekenis of plaatsgewicht) in een bepaalde richting wisselt:van 1 naar 0.

Kleine pijlen geven die punten in de reeks aan waar een bit wisselt, waarbij de punt van de pijl die naar het vorige bit wijst, overgaat van een "hoge" (1) toestand naar een "lage" (0) toestand:

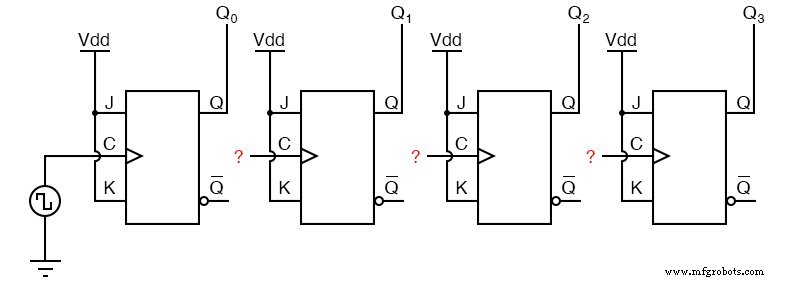

Beginnend met vier JK-flip-flops die zo zijn aangesloten dat ze altijd in de "toggle" -modus staan, moeten we bepalen hoe de klokingangen zo moeten worden aangesloten dat elke volgende bit wisselt wanneer de bit ervoor overgaat van 1 naar 0.

De Q-uitgangen van elke flip-flop zullen dienen als de respectieve binaire bits van de laatste, vier-bits telling:

Als we flip-flops met negatieve-edge triggering zouden gebruiken (bubbelsymbolen op de klokingangen), zouden we eenvoudig de klokingang van elke flip-flop kunnen verbinden met de Q-uitgang van de flip-flop ervoor, zodat wanneer de bit ervoor het verandert van een 1 in een 0, de "dalende flank" van dat signaal zou de volgende flip-flop "klokken" om het volgende bit te schakelen:

Vier-bits “Omhoog” Teller

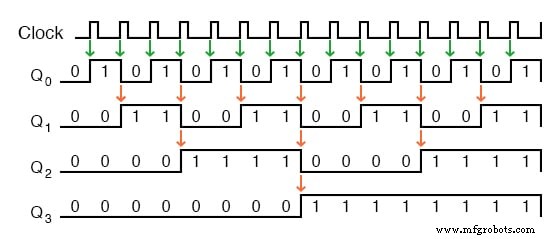

Dit circuit zou de volgende uitgangsgolfvormen opleveren, wanneer het wordt "geklokt" door een zich herhalende bron van pulsen van een oscillator:

De eerste flip-flop (die met de Q0 output), heeft een positieve flank getriggerde klokingang, dus het wisselt met elke stijgende flank van het kloksignaal.

Merk op hoe het kloksignaal in dit voorbeeld een duty cycle heeft van minder dan 50%.

Ik heb het signaal op deze manier getoond om te demonstreren hoe het kloksignaal niet symmetrisch hoeft te zijn om betrouwbare, "schone" uitvoerbits te verkrijgen in onze vier-bits binaire reeks.

In de allereerste flip-flop-schakeling die in dit hoofdstuk wordt getoond, heb ik het kloksignaal zelf als een van de uitgangsbits gebruikt.

Dit is echter een slechte gewoonte bij het ontwerpen van tellers, omdat het het gebruik van een blokgolfsignaal met een 50% duty cycle (“hoge” tijd =“lage” tijd) vereist om een telreeks te verkrijgen waarbij elke stap pauzeert even lang.

Het gebruik van één J-K-flip-flop voor elk uitgangsbit verlost ons echter van de noodzaak van een symmetrisch kloksignaal, waardoor praktisch elke variëteit van hoge/lage golfvormen kan worden gebruikt om de telreeks te verhogen.

Zoals aangegeven door alle andere pijlen in het pulsdiagram, wordt elke volgende uitvoerbit omgeschakeld door de actie van de voorgaande bit die overgaat van "hoog" (1) naar "laag" (0).

Dit is het patroon dat nodig is om een "up" count-reeks te genereren.

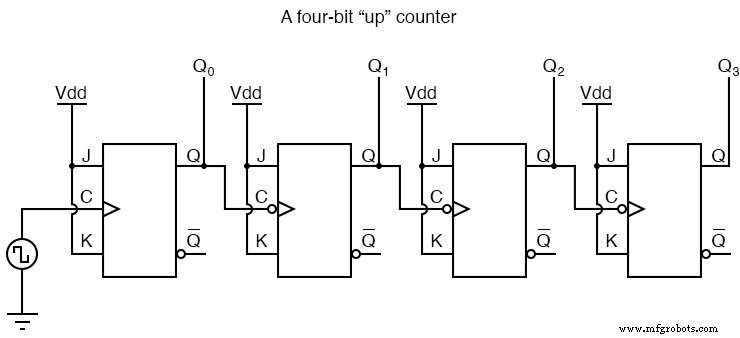

Een minder voor de hand liggende oplossing voor het genereren van een "up" -reeks met behulp van flip-flops met positieve rand, is om elke flip-flop te "klokken" met behulp van de Q'-uitgang van de voorgaande flip-flop in plaats van de Q-uitgang.

Aangezien de Q'-uitgang altijd precies de tegenovergestelde toestand is van de Q-uitgang op een JK-flip-flop (geen ongeldige toestanden bij dit type flip-flop), zal een overgang van hoog naar laag op de Q-uitgang gepaard gaan met een overgang van laag naar hoog op de Q'-uitgang.

Met andere woorden, elke keer dat de Q-uitgang van een flip-flop overgaat van 1 naar 0, zal de Q'-uitgang van dezelfde flip-flop overgaan van 0 naar 1, wat de positief gaande klokpuls oplevert die we nodig zouden hebben om een positieve-edge getriggerde flip-flop op het juiste moment:

Alternatieve vier-bits “omhoog” teller

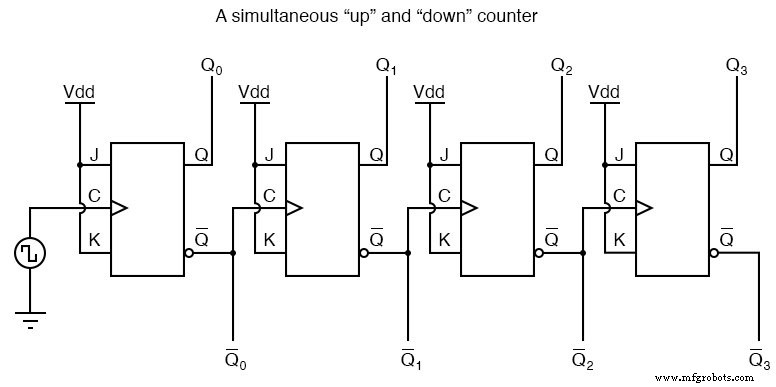

Een manier waarop we de mogelijkheden van een van deze twee tegencircuits kunnen uitbreiden, is door de Q'-uitgangen te beschouwen als een andere set van vier binaire bits.

Als we het pulsdiagram voor zo'n circuit bekijken, zien we dat de Q'-uitgangen een down genereren -telsequentie, terwijl de Q-uitgangen een up . genereren -telvolgorde:

Gelijktijdige "Omhoog" en "Omlaag" teller

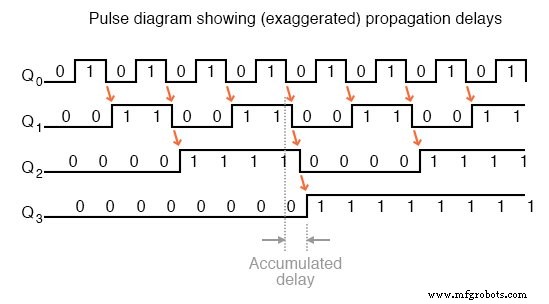

Helaas hebben alle tot nu toe getoonde tegencircuits een gemeenschappelijk probleem:de rimpeling effect.

Dit effect wordt gezien in bepaalde typen binaire opteller en dataconversiecircuits, en is te wijten aan cumulatieve voortplantingsvertragingen tussen gecascadeerde poorten.

Wanneer de Q-uitgang van een flip-flop overgaat van 1 naar 0, geeft deze de volgende flip-flop het commando om te wisselen.

Als de volgende flip-flop toggle een overgang is van 1 naar 0, zal het de flip-flop erna opdracht geven om ook te toggle, enzovoort.

Omdat er echter altijd een kleine hoeveelheid voortplantingsvertraging is tussen het commando om te schakelen (de klokpuls) en de daadwerkelijke toggle-respons (Q en Q'-uitgangen veranderen van toestand), zullen alle volgende flip-flops die moeten worden geschakeld enige tijd wisselen na de eerste flip-flop is omgeschakeld.

Dus wanneer meerdere bits in een binaire telreeks wisselen, zullen ze niet allemaal op precies hetzelfde moment wisselen:

Nadeel van asynchrone tellerschakeling:voortplantingsvertraging

Zoals u kunt zien, hoe meer bits er worden geschakeld met een bepaalde klokpuls, hoe ernstiger de geaccumuleerde vertragingstijd van LSB naar MSB.

Wanneer een klokpuls optreedt op zo'n overgangspunt (bijvoorbeeld bij de overgang van 0111 naar 1000), zullen de uitvoerbits in volgorde "rimpelen" van LSB naar MSB, aangezien elke volgende bit schakelt en de volgende bit opdracht geeft om ook te wisselen , met een kleine propagatievertraging tussen elke bitwissel.

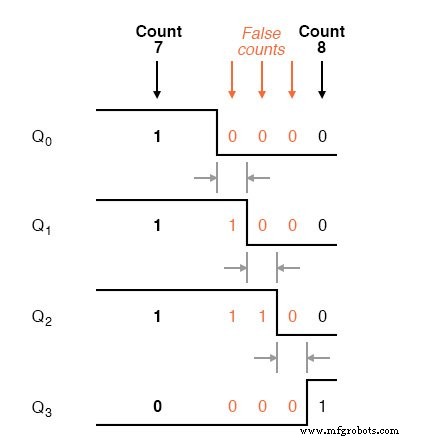

Als we dit effect tijdens de overgang van 0111 naar 1000 van dichtbij bekijken, kunnen we zien dat er false zal zijn outputtellingen gegenereerd in de korte tijdsperiode dat het "rimpeleffect" plaatsvindt:

In plaats van netjes over te gaan van een "0111" -uitgang naar een "1000" -uitgang, zal het tellercircuit zeer snel rimpelen van 0111 naar 0110 naar 0100 naar 0000 naar 1000, of van 7 naar 6 tot 4 tot 0 en dan naar 8. Door dit gedrag krijgt het tellercircuit de naam rimpelteller , of asynchrone teller .

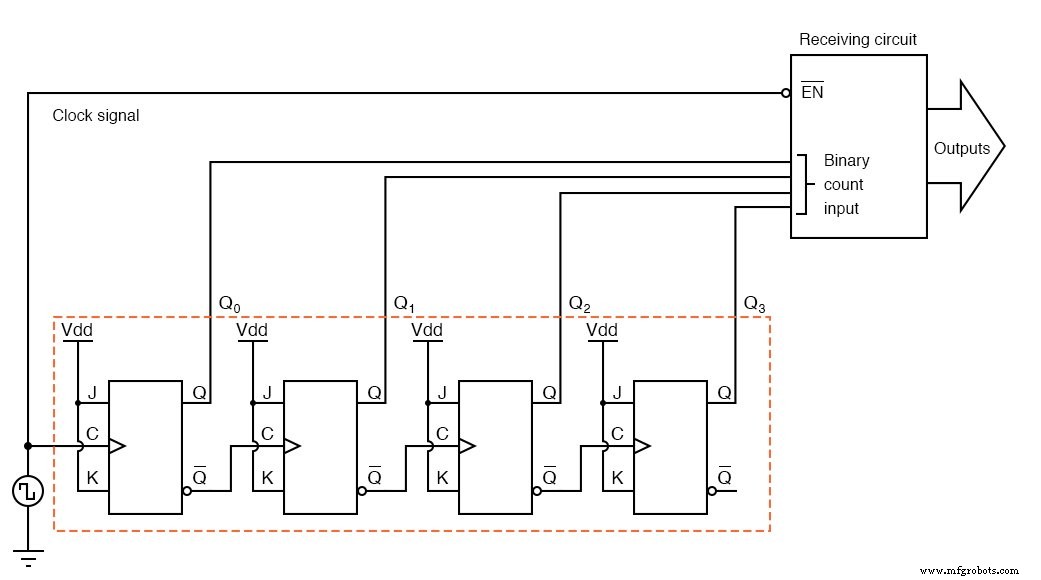

Stroboscoopsignaaltellercircuit

In veel toepassingen is dit effect aanvaardbaar, aangezien de rimpeling zeer, zeer snel optreedt (de breedte van de vertragingen is hier overdreven om de effecten te begrijpen).

Als we alleen maar een set light-emitting diodes (LED's) wilden aansturen met de uitgangen van de teller, zou deze korte rimpel helemaal geen gevolgen hebben.

Als we deze teller echter willen gebruiken om de "select"-ingangen van een multiplexer aan te sturen, een geheugenaanwijzer in een microprocessor (computer) circuit te indexeren of een andere taak uit te voeren waarbij valse uitgangen valse fouten kunnen veroorzaken, zou dit niet acceptabel zijn .

Er is een manier om dit type tellerschakeling te gebruiken in toepassingen die gevoelig zijn voor valse, door rimpelingen gegenereerde uitgangen, en het omvat een principe dat bekend staat als strobing .

De meeste decoder- en multiplexercircuits zijn uitgerust met ten minste één ingang die "enable" wordt genoemd.

De uitgang(en) van zo'n circuit zijn alleen actief als de activeringsingang actief is gemaakt.

We kunnen deze activeringsinvoer gebruiken om flitsen het circuit dat de uitgang van de rimpelteller ontvangt, zodat deze is uitgeschakeld (en dus niet reageert op de telleruitgang) gedurende de korte periode waarin de telleruitgangen kunnen rimpelen, en alleen wordt ingeschakeld als er voldoende tijd is verstreken sinds de laatste klokpuls dat al het kabbelen zal zijn opgehouden.

In de meeste gevallen kan het stroboscoopsignaal dezelfde klokpuls zijn die het tellercircuit aanstuurt:

Met een active-low Enable-ingang reageert het ontvangende circuit alleen op de binaire telling van het vierbits-tellercircuit wanneer het kloksignaal "laag" is.

Zodra de klokpuls "hoog" wordt, reageert het ontvangende circuit niet meer op de uitgang van het tellercircuit.

Aangezien het tellercircuit positief-flankgetriggerd is (zoals bepaald door de eerste flip-flop klokingang), alle telacties vinden plaats op de laag-naar-hoog overgang van het kloksignaal, wat betekent dat het ontvangstcircuit wordt uitgeschakeld net voordat er een omschakeling plaatsvindt op de vier uitgangsbits van het tellercircuit.

Het ontvangstcircuit wordt pas ingeschakeld als het kloksignaal terugkeert naar een lage status, wat lang genoeg zou moeten zijn na alle rimpelingen zijn niet langer "veilig" om de nieuwe telling effect te laten hebben op het ontvangende circuit.

De cruciale parameter hier is de "hoge" tijd van het kloksignaal:deze moet minstens zo lang zijn als de maximaal verwachte rimpelperiode van het tellercircuit.

Als dit niet het geval is, zal het kloksignaal het ontvangstcircuit voortijdig inschakelen, terwijl er nog steeds wat rimpeling plaatsvindt.

Nadeel van asynchrone tellerschakeling:beperkte snelheid

Een ander nadeel van het asynchrone of rimpel-tellercircuit is de beperkte snelheid.

Hoewel alle poortcircuits beperkt zijn in termen van maximale signaalfrequentie, verergert het ontwerp van asynchrone tegencircuits dit probleem door voortplantingsvertragingen additief te maken.

Dus zelfs als stroboscoop wordt gebruikt in het ontvangstcircuit, kan een asynchrone tellerschakeling niet worden geklokt op een hogere frequentie dan die waarmee de grootst mogelijke geaccumuleerde voortplantingsvertraging kan verstrijken ruim voor de volgende puls.

De oplossing voor dit probleem is een tegenschakeling die rimpeling helemaal vermijdt.

Een dergelijk tellercircuit zou de noodzaak elimineren om een "strobing"-functie te ontwerpen in alle digitale circuits die de telleruitgang als ingang gebruiken, en zou ook een veel grotere werksnelheid hebben dan zijn asynchrone equivalent.

Dit ontwerp van een tegencircuit is het onderwerp van de volgende sectie.

BEOORDELING:

- Een "omhoog" -teller kan worden gemaakt door de klokingangen van JK-flip-flops met positieve flank te verbinden met de Q'-uitgangen van de voorgaande flip-flops. Een andere manier is om flip-flops met negatieve flank te gebruiken, waarbij de klokingangen worden aangesloten op de Q-uitgangen van de voorgaande flip-flops. In beide gevallen zijn de J- en K-ingangen van alle flip-flops verbonden met Vcc of Vdd om altijd "high" te zijn.

- Tegenschakelingen gemaakt van gecascadeerde JK-flip-flops waarbij elke klokingang zijn pulsen ontvangt van de uitgang van de vorige flip-flop vertonen steevast een rimpeleffect , waarbij valse uitvoertellingen worden gegenereerd tussen sommige stappen van de telreeks. Dit soort tellerschakelingen worden asynchrone tellers genoemd , of rimpeltellers .

- Knipperlicht is een techniek die wordt toegepast op circuits die de uitvoer van een asynchrone (rimpel)teller ontvangen, zodat de valse tellingen die tijdens de rimpeltijd worden gegenereerd, geen nadelig effect hebben. In wezen is de enable ingang van zo'n circuit is op een zodanige manier verbonden met de klokpuls van de teller dat deze alleen wordt ingeschakeld wanneer de telleruitgangen niet veranderen, en zal worden uitgeschakeld tijdens die perioden van veranderende telleruitgangen waar rimpel optreedt.

GERELATEERDE WERKBLAD:

- Werkblad Ripple Counter

Industriële technologie