CMOS Gate Circuitry

Tot nu toe was onze analyse van logische transistorschakelingen beperkt tot de TTL ontwerpparadigma, waarbij bipolaire transistors worden gebruikt, en de algemene strategie waarbij zwevende ingangen equivalent zijn aan "hoog" (verbonden met Vcc ) ingangen - en dienovereenkomstig de toelating van "open-collector" eindtrappen - wordt gehandhaafd. Dit is echter niet de enige manier waarop we logische poorten kunnen bouwen.

Veldeffecttransistoren

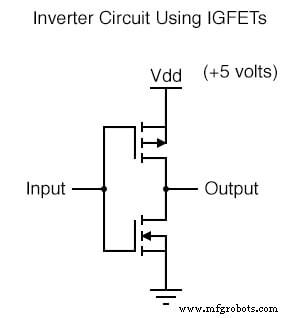

Veldeffecttransistoren, met name de variant met geïsoleerde poort, kunnen worden gebruikt bij het ontwerp van poortschakelingen. Omdat ze spanningsgestuurde in plaats van stroomgestuurde apparaten zijn, hebben IGFET's de neiging om zeer eenvoudige circuitontwerpen mogelijk te maken. Neem bijvoorbeeld het volgende invertercircuit dat is gebouwd met P- en N-kanaals IGFET's:

Let op de "Vdd ” label op de positieve voedingsklem. Dit label volgt dezelfde conventie als "Vcc ” in TTL-circuits:het staat voor de constante spanning die wordt toegepast op de afvoer van een veldeffecttransistor, met verwijzing naar aarde.

Veldeffecttransistoren in poortcircuits

Lage invoer

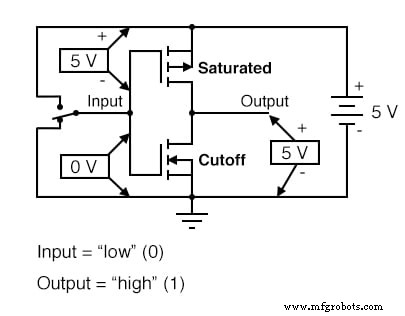

Laten we dit poortcircuit aansluiten op een stroombron en ingangsschakelaar en de werking ervan onderzoeken. Houd er rekening mee dat deze IGFET-transistoren van het E-type (Enhancement-mode) zijn, en dus normaal uitgeschakeld apparaten.

Er is een aangelegde spanning tussen poort en afvoer (eigenlijk, tussen poort en substraat) van de juiste polariteit nodig om ze aan voor te spannen .

De bovenste transistor is een P-kanaal IGFET. Wanneer het kanaal (substraat) positiever wordt gemaakt dan de poort (poort negatief ten opzichte van het substraat), wordt het kanaal versterkt en wordt er stroom toegestaan tussen source en drain.

Dus in de bovenstaande afbeelding is de bovenste transistor ingeschakeld. De onderste transistor, met nul spanning tussen poort en substraat (bron), bevindt zich in de normale modus:uit .

De werking van deze twee transistoren is dus zodanig dat de uitgangsklem van het poortcircuit een solide verbinding heeft met Vdd en een verbinding met aarde met een zeer hoge weerstand. Dit maakt de uitgang “hoog” (1) voor de “laag” (0) toestand van de ingang.

Hoge invoer

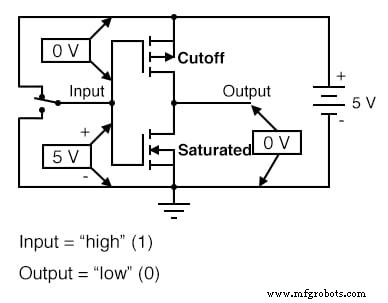

Vervolgens verplaatsen we de ingangsschakelaar naar de andere positie en kijken wat er gebeurt:

Nu is de onderste transistor (N-kanaal) verzadigd omdat er voldoende spanning van de juiste polariteit is aangelegd tussen poort en substraat (kanaal) om deze aan te zetten (positief op poort, negatief op het kanaal). De bovenste transistor, met een spanning van nul tussen de poort en het substraat, bevindt zich in de normale modus:uit .

De uitgang van dit poortcircuit is nu dus "laag" (0). Het is duidelijk dat deze schakeling het gedrag van een inverter, oftewel GEEN poort, vertoont.

Complementaire metaaloxidehalfgeleiders (CMOS)

Het gebruik van veldeffecttransistoren in plaats van bipolaire transistors heeft het ontwerp van de inverterpoort aanzienlijk vereenvoudigd. Merk op dat de uitgang van deze poort nooit zweeft, zoals het geval is bij het eenvoudigste TTL-circuit:het heeft een natuurlijke "totempaal"-configuratie, die zowel in staat is om belastingsstroom te sourcen als te laten dalen.

De sleutel tot het elegante ontwerp van dit poortcircuit is de complementaire gebruik van zowel P- als N-kanaals IGFET's. Aangezien IGFET's beter bekend staan als MOSFET's (M etal-O xide-S emiconductor F veld E ffect T ransistor), en dit circuit gebruikt zowel P- als N-kanaaltransistoren samen, de algemene classificatie die aan poortcircuits zoals deze wordt gegeven, is CMOS :C aanvullende M et al O xide S econductor.

CMOS Gates:uitdagingen en oplossingen

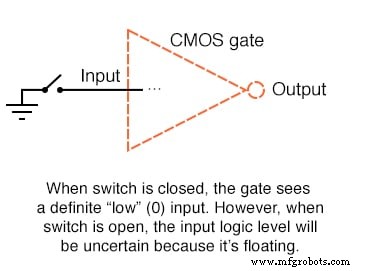

CMOS-circuits worden niet geplaagd door de inherente niet-lineariteiten van de veldeffecttransistoren, omdat als digitale circuits hun transistors altijd werken in de verzadigde of afsluiting modi en nooit in de actieve modus. Hun ingangen zijn echter gevoelig voor hoge spanningen die worden gegenereerd door elektrostatische (statische elektriciteit) bronnen, en kunnen zelfs worden geactiveerd in "hoge" (1) of "lage" (0) toestanden door onechte spanningsbronnen als ze zwevend worden gelaten.

Om deze reden is het af te raden om een CMOS logische poortingang onder geen enkele omstandigheid te laten zweven. Houd er rekening mee dat dit heel anders is dan het gedrag van een TTL-poort waarbij een zwevende ingang veilig werd geïnterpreteerd als een "hoog" (1) logisch niveau.

CMOS-problemen met zwevende invoer

Dit kan een probleem veroorzaken als de invoer naar een CMOS-logische poort wordt aangestuurd door een schakelaar met één worp, waarbij één toestand de invoer stevig verbonden heeft met ofwel Vdd of aarde en de andere staat heeft de input zwevend (niet verbonden met iets):

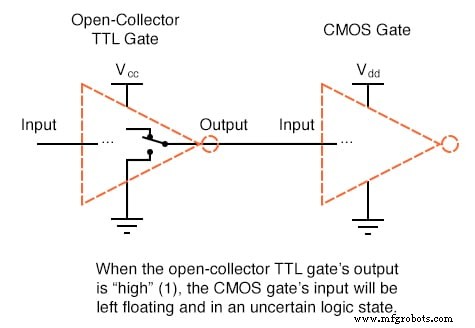

Dit probleem doet zich ook voor als een CMOS-poortinvoer wordt aangestuurd door een open-collector TTL-poort. Omdat de uitgang van een dergelijke TTL-poort zweeft wanneer deze "hoog" wordt (1), blijft de ingang van de CMOS-poort in een onzekere toestand:

Oplossing voor zwevende ingangen

Optrekweerstanden

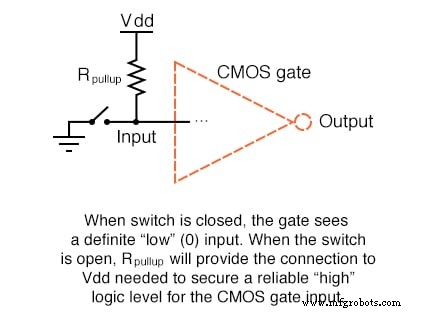

Gelukkig is er een gemakkelijke oplossing voor dit dilemma, een die vaak wordt gebruikt in CMOS-logische schakelingen. Telkens wanneer een schakelaar met één worp (of een ander soort poortuitgang die niet in staat is tot beide) sourcing en sinking current) wordt gebruikt om een CMOS-ingang aan te sturen, een weerstand die is aangesloten op Vdd of aarde kan worden gebruikt om een stabiel logisch niveau te bieden voor de toestand waarin de uitvoer van het aandrijfapparaat zweeft.

De waarde van deze weerstand is niet kritisch:10 kΩ is meestal voldoende. Wanneer gebruikt om een "hoog" (1) logisch niveau te leveren in het geval van een zwevende signaalbron, staat deze weerstand bekend als een pullup-weerstand :

Pulldown-weerstanden

Wanneer een dergelijke weerstand wordt gebruikt om een "laag" (0) logisch niveau te leveren in het geval van een zwevende signaalbron, staat dit bekend als een pulldown-weerstand . Nogmaals, de waarde voor een pulldown-weerstand is niet kritisch:

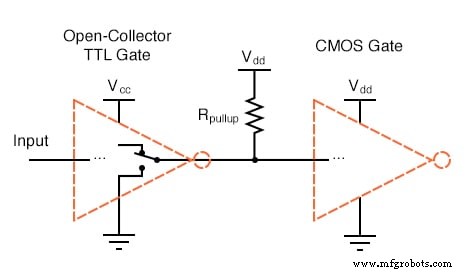

Omdat open-collector TTL-uitgangen altijd zinken, nooit bron, stroom, pullup weerstanden zijn nodig bij het koppelen van een dergelijke uitgang aan een CMOS-poortingang:

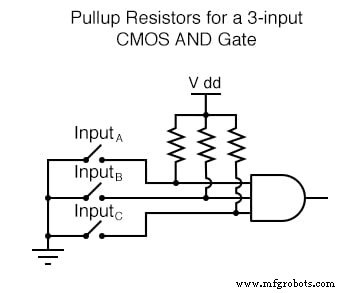

Meerdere pullup- en pulldown-weerstanden

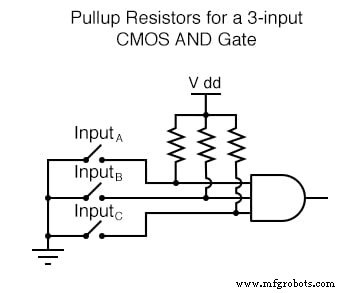

Hoewel de CMOS-poorten die in de voorgaande voorbeelden werden gebruikt allemaal inverters waren (single-input), is hetzelfde principe van pullup- en pulldown-weerstanden van toepassing op CMOS-gates met meerdere inputs. Natuurlijk is voor elke poortingang een aparte pullup- of pulldown-weerstand vereist:

Dit brengt ons bij de volgende vraag:hoe ontwerpen we CMOS-poorten met meerdere invoer, zoals AND, NAND, OR en NOR? Het is niet verrassend dat de antwoorden op deze vraag een eenvoud van ontwerp onthullen die veel lijkt op die van de CMOS-omvormer ten opzichte van zijn TTL-equivalent.

CMOS NAND-poorten

Hier is bijvoorbeeld het schematische diagram voor een CMOS NAND-poort:

Merk op hoe transistors Q1 en Q3 lijken op het in serie geschakelde complementaire paar van het invertercircuit. Beide worden bestuurd door hetzelfde ingangssignaal (ingang A), de bovenste transistor wordt uitgeschakeld en de onderste transistor wordt ingeschakeld wanneer de ingang "hoog" is (1), en vice versa.

Merk ook op hoe transistors Q2 en Q4 op dezelfde manier worden bestuurd door hetzelfde ingangssignaal (ingang B), en hoe ze ook hetzelfde aan/uit-gedrag zullen vertonen voor dezelfde logische ingangsniveaus. De bovenste transistoren van beide paren (Q1 en Q2 ) hebben hun source- en drain-aansluitingen parallel, terwijl de onderste transistors (Q3 en Q4 ) zijn in serie geschakeld.

Wat dit betekent is dat de uitvoer "hoog" wordt (1) als ofwel bovenste transistor verzadigt, en zal alleen "laag" (0) worden als beide lagere transistoren verzadigen.

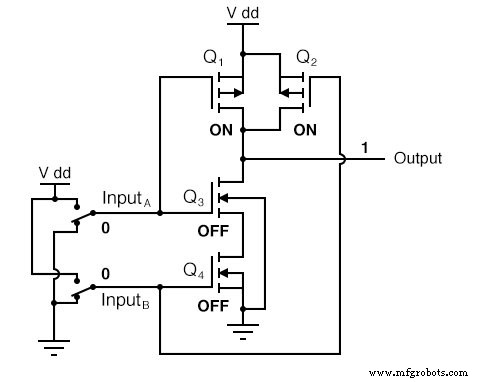

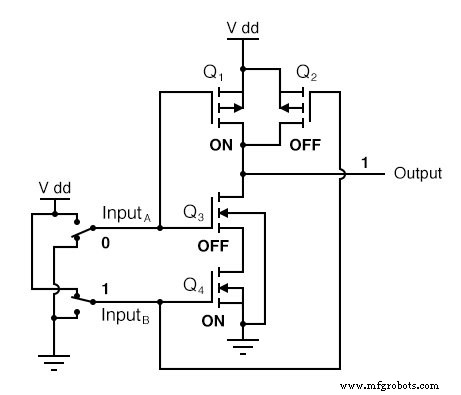

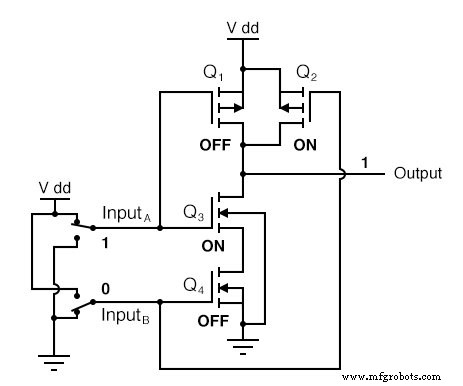

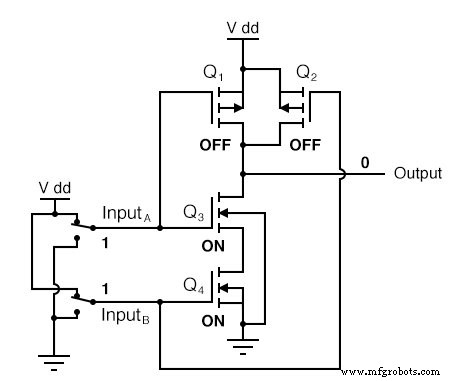

CMOS-circuitgedrag voor alle logische ingangen

De volgende reeks illustraties toont het gedrag van deze NAND-poort voor alle vier de mogelijkheden van logische ingangsniveaus (00, 01, 10 en 11):

CMOS EN poort

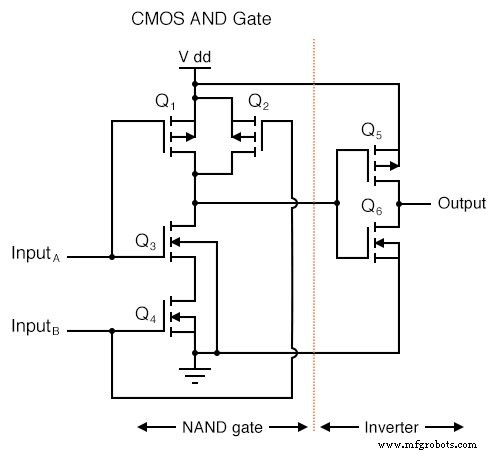

Net als bij de TTL NAND-poort, kan het CMOS NAND-poortcircuit worden gebruikt als het startpunt voor het maken van een EN-poort. Het enige dat moet worden toegevoegd, is nog een transistortrap om het uitgangssignaal om te keren:

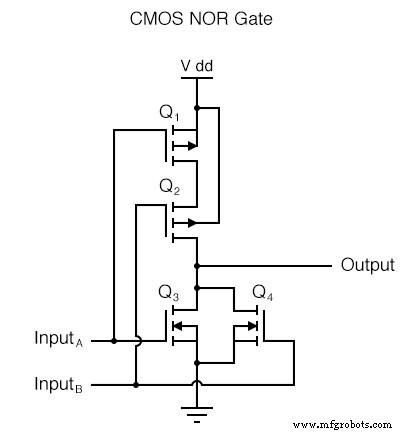

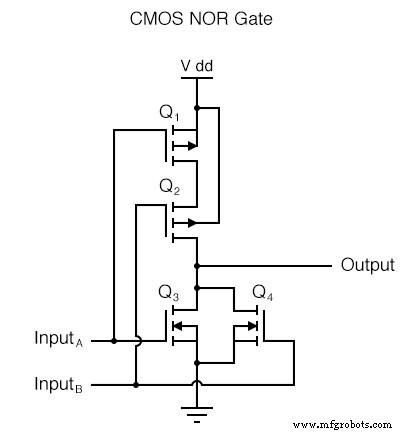

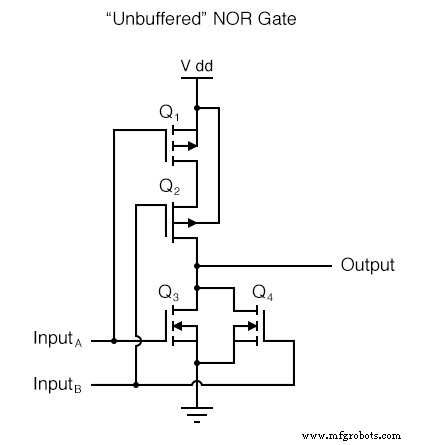

CMOS NOR-poorten

Een CMOS NOR-poortcircuit gebruikt vier MOSFET's, net als de NAND-poort, behalve dat de transistors anders zijn gerangschikt. In plaats van twee parallelle sourcing (bovenste) transistoren aangesloten op Vdd en twee in serie geschakelde sinking (lagere) transistors verbonden met aarde, de NOR-poort gebruikt twee in serie geschakelde sourcing-transistoren en twee parallel geschakelde zinkende transistors zoals deze:

Net als bij de NAND-poort, transistoren Q1 en Q3 werken als een complementair paar, net als de transistors Q2 en Q4 . Elk paar wordt bestuurd door een enkel ingangssignaal. Als ofwel voer A of . in ingang B zijn “hoog” (1), ten minste één van de onderste transistoren (Q3 of Q4 ) zal verzadigd zijn, waardoor de output “laag” (0) wordt.

Alleen in het geval van beide inputs die "laag" (0) zijn, zullen beide onderste transistors in de cutoff-modus zijn en beide bovenste transistors zijn verzadigd, de voorwaarden die nodig zijn om de output "hoog" te laten worden (1). Dit gedrag definieert natuurlijk de NOR-logische functie.

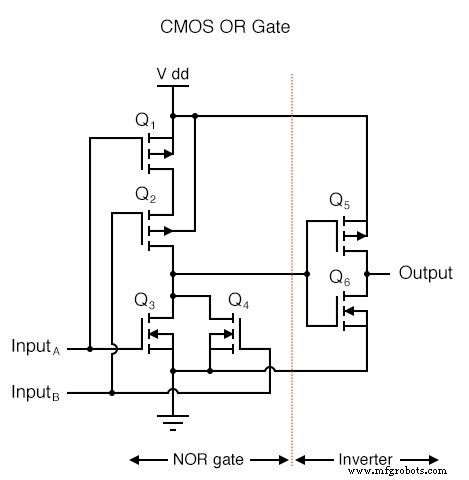

CMOS OF-poorten

De OF-functie kan worden opgebouwd uit de basis-NOR-poort met toevoeging van een invertertrap op de uitgang:

TTL vs. CMOS:voor- en nadelen

Aangezien het lijkt alsof elke poort die met TTL-technologie kan worden geconstrueerd, in CMOS kan worden gedupliceerd, waarom bestaan deze twee "families" van logisch ontwerp dan nog steeds naast elkaar? Het antwoord is dat zowel TTL als CMOS hun eigen unieke voordelen hebben.

Eerst en vooral op de lijst met vergelijkingen tussen TTL en CMOS is de kwestie van het stroomverbruik. In deze prestatiemaatstaf is CMOS de onbetwiste winnaar. Omdat de complementaire P- en N-kanaals MOSFET-paren van een CMOS-poortcircuit (idealiter) nooit tegelijkertijd geleiden, wordt er weinig of geen stroom getrokken door het circuit van de Vdd voeding, behalve de stroom die nodig is om stroom naar een belasting te leiden. TTL, aan de andere kant, kan niet altijd functioneren zonder een stroom die te allen tijde wordt getrokken, vanwege de voorspanningsvereisten van de bipolaire transistors waaruit het is gemaakt.

Er is wel een kanttekening bij dit voordeel. Terwijl de vermogensdissipatie van een TTL-poort vrij constant blijft, ongeacht de bedrijfstoestand(en), dissipeert een CMOS-poort meer vermogen naarmate de frequentie van zijn ingangssignaal(en) stijgt. Als een CMOS-poort in een statische (onveranderlijke) toestand wordt gebruikt, dissipeert deze (idealiter) nul stroom.

CMOS-poortcircuits trekken echter transiënte stroom tijdens elke uitgangstoestandomschakeling van "laag" naar "hoog" en vice versa. Dus hoe vaker een CMOS-gate van modus wisselt, hoe vaker hij stroom zal trekken van de Vdd voeding, dus grotere vermogensdissipatie bij hogere frequenties.

Voordelen van CMOS

Een CMOS-poort trekt ook veel minder stroom van een stuurpoortuitgang dan een TTL-poort, omdat MOSFET's spanningsgestuurde, niet stroomgestuurde apparaten zijn. Dit betekent dat één poort veel meer CMOS-ingangen kan aansturen dan TTL-ingangen. De maat voor hoeveel poortingangen een enkele poortuitgang kan aansturen, wordt fanout genoemd .

Een ander voordeel dat CMOS-poortontwerpen hebben ten opzichte van TTL, is een veel breder toegestaan bereik van voedingsspanningen. Terwijl TTL-poorten beperkt zijn tot stroomvoorziening (Vcc ) spanningen tussen 4,75 en 5,25 volt, kunnen CMOS-poorten doorgaans werken op elke spanning tussen 3 en 15 volt!

De reden achter deze ongelijkheid in voedingsspanningen zijn de respectieve voorspanningsvereisten van MOSFET versus bipolaire junctietransistoren. MOSFET's worden uitsluitend bestuurd door poortspanning (met betrekking tot substraat), terwijl BJT's stroomgestuurd zijn apparaten.

TTL-poortcircuitweerstanden worden nauwkeurig berekend voor de juiste biasstromen, uitgaande van een 5 volt gereguleerde voeding. Elke significante variatie in die voedingsspanning zal ertoe leiden dat de voorspanningsstromen van de transistor onjuist zijn, wat vervolgens resulteert in een onbetrouwbare (onvoorspelbare) werking.

Het enige effect dat variaties in de voedingsspanning hebben op een CMOS-poort is de spanningsdefinitie van een "hoge" (1) toestand. Voor een CMOS-poort die werkt op 15 volt voedingsspanning (Vdd ), moet een ingangssignaal bijna 15 volt zijn om als "hoog" te worden beschouwd (1). De spanningsdrempel voor een "laag" (0) signaal blijft hetzelfde:bijna 0 volt.

Nadelen van CMOS

Een duidelijk nadeel van CMOS is de lage snelheid in vergelijking met TTL. De ingangscapaciteiten van een CMOS-poort zijn veel, veel groter dan die van een vergelijkbare TTL-poort - vanwege het gebruik van MOSFET's in plaats van BJT's - en dus zal een CMOS-poort langzamer reageren op een signaalovergang (van laag naar hoog). of vice versa) dan een TTL-poort, waarbij alle andere factoren gelijk zijn.

De RC-tijdconstante gevormd door circuitweerstanden en de ingangscapaciteit van de poort hebben de neiging de snelle stijg- en daaltijden van een digitaal logisch niveau te belemmeren, waardoor de hoogfrequente prestaties afnemen.

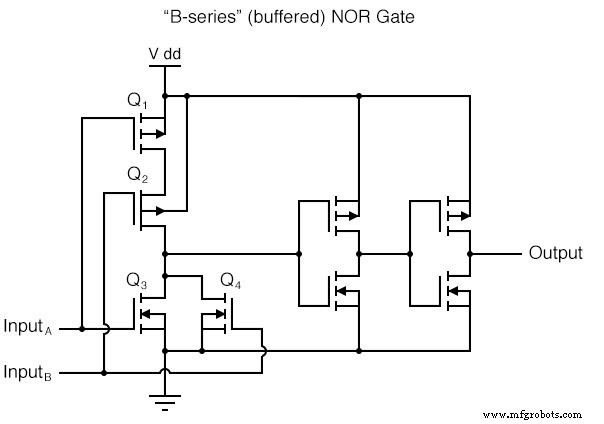

Strategieën om de nadelen te bestrijden

Een strategie om dit inherente nadeel van CMOS-poortschakelingen te minimaliseren, is om het uitgangssignaal te "bufferen" met extra transistortrappen, om de algehele spanningsversterking van het apparaat te vergroten. Dit zorgt voor een snellere overgangsuitgangsspanning (hoog naar laag of laag naar hoog) voor een ingangsspanning die langzaam verandert van de ene logische toestand naar de andere.

Beschouw dit voorbeeld van een "niet-gebufferde" NOR-poort versus een "gebufferde" of B-serie , NOR-poort:

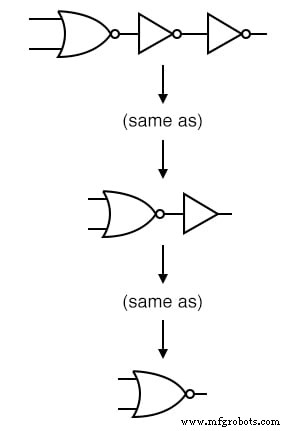

In wezen voegt de ontwerpverbetering van de B-serie twee inverters toe aan de output van een eenvoudig NOR-circuit. Dit heeft geen zin voor zover het digitale logica betreft, omdat twee cascade-omvormers gewoon annuleren:

Het toevoegen van deze invertertrappen aan het circuit dient echter om de algehele spanningsversterking te vergroten, waardoor de uitgang gevoeliger wordt voor veranderingen in de ingangsstatus, en om de inherente traagheid te overwinnen die wordt veroorzaakt door de ingangscapaciteit van de CMOS-poort.

BEOORDELING:

- Logische CMOS-poorten zijn gemaakt van IGFET-transistors (MOSFET) in plaats van bipolaire junctietransistoren.

- CMOS-poortingangen zijn gevoelig voor statische elektriciteit. Ze kunnen worden beschadigd door hoge spanningen en ze kunnen elk logisch niveau aannemen als ze zwevend blijven.

- Optrekken en pulldown weerstanden worden gebruikt om te voorkomen dat een CMOS-poortinvoer gaat zweven als deze wordt aangestuurd door een signaalbron die alleen in staat is stroom te leveren of te laten dalen.

- CMOS-poorten dissiperen veel minder vermogen dan vergelijkbare TTL-poorten, maar hun vermogensdissipatie neemt toe met de signaalfrequentie, terwijl de vermogensdissipatie van een TTL-poort ongeveer constant is over een breed scala aan bedrijfsomstandigheden.

- CMOS-poortingangen verbruiken veel minder stroom dan TTL-ingangen, omdat MOSFET's spanningsgestuurde, niet stroomgestuurde apparaten zijn.

- CMOS-poorten kunnen werken op een veel groter bereik aan voedingsspanningen dan TTL:doorgaans 3 tot 15 volt versus 4,75 tot 5,25 volt voor TTL.

- CMOS-poorten hebben de neiging om een veel lagere maximale werkfrequentie te hebben dan TTL-poorten vanwege de ingangscapaciteiten die worden veroorzaakt door de MOSFET-poorten.

- B-serie CMOS-poorten hebben "gebufferde" uitgangen om de spanningsversterking van ingang naar uitgang te vergroten, wat resulteert in een snellere uitgangsrespons op veranderingen in het ingangssignaal. Dit helpt de inherente traagheid van CMOS-poorten als gevolg van MOSFET-ingangscapaciteit en de daardoor veroorzaakte RC-tijdconstante te overwinnen.

GERELATEERDE WERKBLAD:

-

Werkblad veldeffecttransistoren geïsoleerde poort

-

CMOS Logic Gates-werkblad

Industriële technologie

- Hoe bouw je een huidig spiegelcircuit

- Basispoortfunctie

- NOR Gate S-R vergrendeling

- Transistors, bipolair

- Transistors, junction field-effect (JFET)

- Transistors, Insulated-gate Field-effect (IGFET of MOSFET)

- Transistors, hybride

- Geïntegreerde circuits

- De NIET-poort

- Inleiding tot veldeffecttransistoren met geïsoleerde poort

- Modellering op poortniveau