High-performance interconnects bouwen met meerdere PCIe-generaties

PCI Express en de honger naar bandbreedte

Als middel om computers, embedded en aangepaste hostprocessors aan te sluiten op 'eindpunt'-randapparatuur zoals Ethernet-poorten, USB-poorten, videokaarten en opslagapparaten, is PCI Express® (PCIe®) de referentie voor high-performance interconnect geworden. Door gebruik te maken van high-speed seriële communicatie, levert PCIe efficiënte point-to-point-connectiviteit en - door het aantal kanalen en de signaleringssnelheid te verhogen - schaalbare interfacebandbreedte.

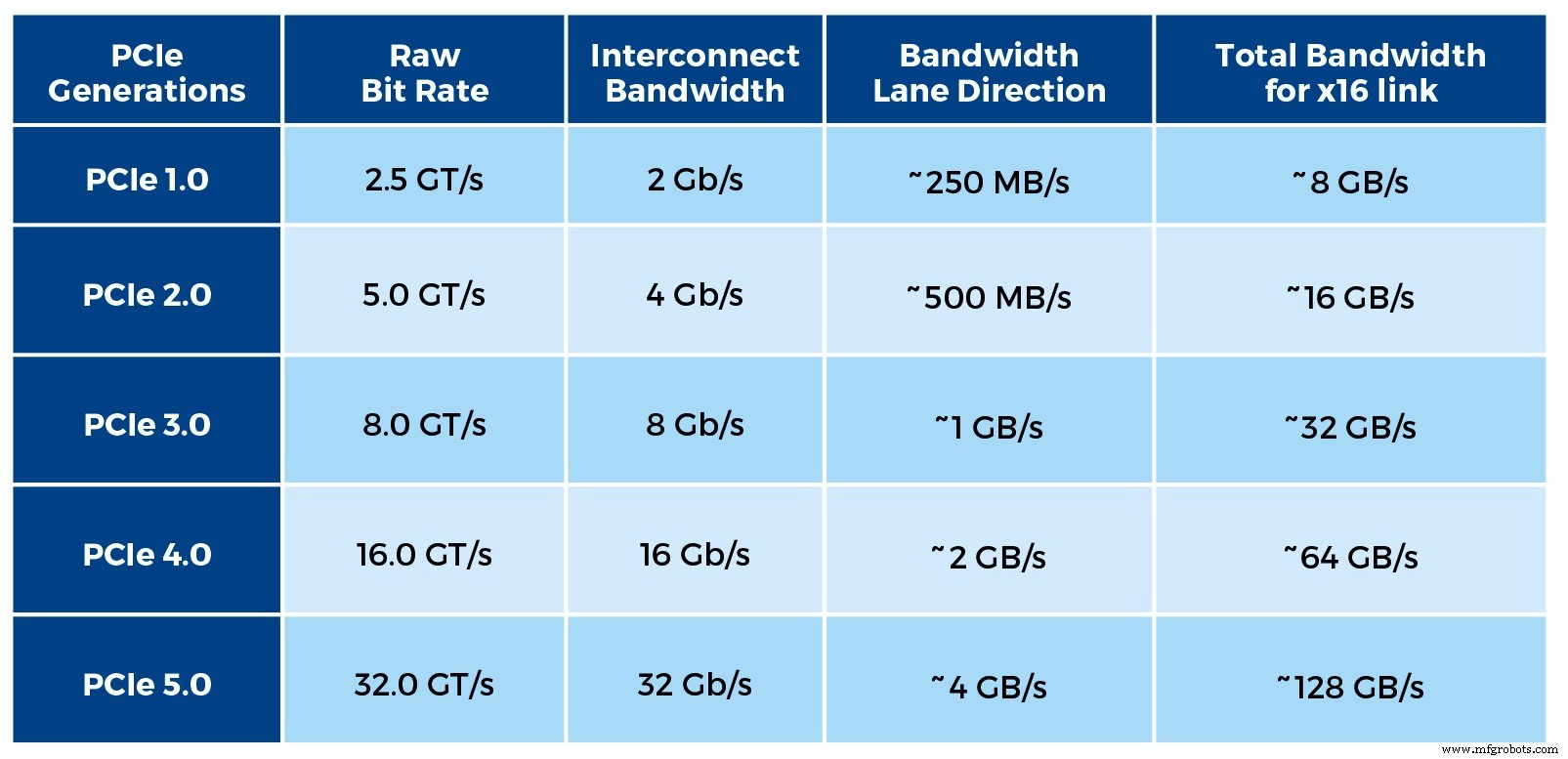

De PCIe 1.0-specificatie werd in 2002 gepubliceerd en werkt met 2,5 giga-overdrachten per seconde (GT/s), wat een totale x16-interfacebandbreedte van 8 GByte/s oplevert. De bandbreedte werd vervolgens verdubbeld in 2006 met de komst van de tweede generatie PCIe 2.0-specificaties en opnieuw in 2010 toen PCIe 3.0 de bandbreedte verhoogde tot 32 GByte/s om te voldoen aan de steeds toenemende eisen van toonaangevende hedendaagse toepassingen, waaronder high-end pc, gaming, enterprise computing en netwerken.

PCI Express is de referentie voor high-performance interconnect geworden voor een breed scala aan systeemontwerpen.

(Bron:Diodes Inc.)

Meer recentelijk heeft de snelle verspreiding van cloudgebaseerde services zoals sociale media en videostreaming nieuwe en veeleisendere vereisten geïntroduceerd voor snelle connectiviteit binnen grootschalige datacenters.

Nu het IoT-tijdperk zijn intrede doet, zullen netwerksensoren die zijn geïnstalleerd in slimme steden en infrastructuren, slimme fabrieken en andere industriële activa, commerciële en residentiële gebouwen, en wearables voor fitness en medische tracking, enorme hoeveelheden gegevens genereren voor hyperscale datacenters om vastleggen, opslaan, verwerken en analyseren. Deze krachten stimuleren de vraag naar de volgende PCIe-generaties om datacenterservers efficiënt te verbinden met high-speed Ethernet, netwerkverbonden opslag en AI-versnellers.

Geconnecteerde auto's zullen de gegevensbelasting verder vergroten, waardoor realtime druk wordt toegevoegd, om hogere niveaus van autonoom rijden en uiteindelijk volledig zelfrijdende voertuigen mogelijk te maken. Achter de datacenters is het trainen van neurale netwerken voor AI-inferentie een rekenintensieve taak die knelpunten in perifere communicatie scherp blootlegt.

Aangezien deze verschillende factoren nu een rol gaan spelen, is de tijd rijp voor PCIe om weer vooruit te gaan. PCIe 4.0, aangekondigd in 2017, werd snel gevolgd door de publicatie van PCIe 5.0 in 2019. Afbeelding 1 toont de totale snelheden die worden geboden door elke PCIe-versie.

Figuur 1:Totale snelheden aangeboden door PCIe-versies (Bron:Diodes Inc.)

PCIe 5.0 zal naar verwachting op grote schaal worden gebruikt, aangezien toonaangevende datacenters de overstap maken van 100Gb Ethernet naar de nieuwste 400Gb-specificatie. In de praktijk hebben de toename van de PCIe-bandbreedte min of meer gelijke tred gehouden met de vooruitgang in Ethernet-snelheden, waarbij idealiter een balans tussen de twee standaarden wordt behouden om prestatieknelpunten te voorkomen.

“Verouderde” PCI-standaarden blijven actueel

Nu PCIe 5.0-producten op de markt komen en met de recente aankondiging door de PCI Special Interest Group (PCI-SIG) dat het werk is begonnen aan de volgende generatie, PCIe 6.0 voor voltooiing in 2021, is PCIe het protocol bij uitstek voor prestaties -hongerige perifere communicatie, voor de nabije toekomst.

Tegelijkertijd is achterwaartse compatibiliteit een belangrijke kracht van de PCIe-reeks. Omdat er geen vervaldatum is voor PCIe-specificaties, kunnen meerdere generaties naast elkaar bestaan op de markt en zelfs in dezelfde toepassing. Dit is een voordeel voor systeemontwerpers:terwijl opeenvolgende nieuwe PCIe-generaties verschijnen om tegemoet te komen aan de steeds grotere bandbreedteverslindende vereisten, blijven eerdere iteraties waarde leveren in een groot aantal scenario's zoals personal computing, gaming en sommige zakelijke computer- en netwerktoepassingen.

Implementatie-uitdagingen oplossen

Dankzij achterwaartse compatibiliteit tussen de verschillende PCIe-generaties kunnen systemen profiteren van hogere overdrachtssnelheden wanneer nieuw silicium beschikbaar komt, met minimale ontwerpwijzigingen. Aan de andere kant leggen stijgende signaalsnelheden extra druk op de signaalmarges en kunnen ze de ontwerpcomplexiteit vergroten. Daarnaast is er een duidelijke behoefte aan oplossingen die bridging van en naar PCIe mogelijk maken, niet alleen tussen legacy interfaces maar ook tussen andere interfaces zoals USB of grafische poorten.

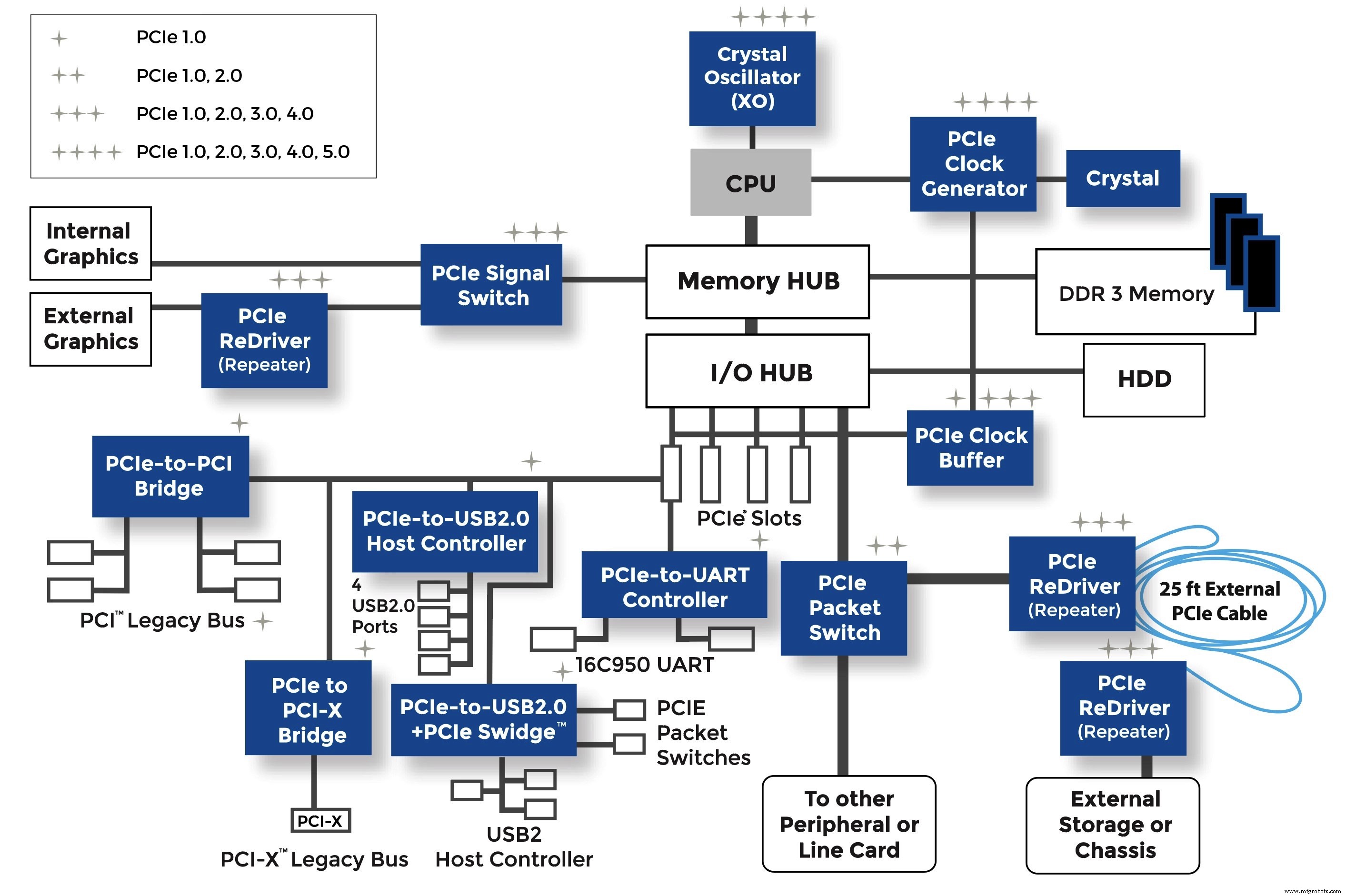

Om deze uitdagingen aan te gaan, hebben ontwerpers toegang nodig tot apparaten die verschillende PCIe-generaties ondersteunen, zoals de klokgeneratoren, klokbuffers, controllers, pakketschakelaars/bridges, ReDriver™-chips en snelle multiplexers zoals weergegeven in afbeelding 2.

klik voor grotere afbeelding

Figuur 2:Een voorbeeld van de PCIe-oplossingen die verkrijgbaar zijn bij Diodes Inc. (Bron:Diodes Inc.)

ReDriver-chips kunnen een kosteneffectieve en handige oplossing bieden voor het versterken van de signaalintegriteit in hogesnelheidssystemen. Met behulp van technieken zoals egalisatie en pre-emphasis, met een output driver die minimale latentie introduceert, compenseert de ReDriver transmissielijnverliezen om de signaalmarge te herstellen en jitter te minimaliseren om een lage bit-error rate bij de ontvanger te garanderen. Vergeleken met een retimer, die extra functies integreert, waaronder klok- en gegevensherstel, introduceert een ReDriver een lage vertraging en is relatief zuinig en eenvoudig te implementeren. Afbeelding 2 laat zien hoe een PCIe ReDriver kan worden gebruikt waar signalen over een langer PCB-spoor moeten worden gestuurd, zoals naar een externe grafische kaart of via een kabel naar externe opslag. Deze ReDrivers zijn volledig achterwaarts compatibel en ondersteunen alle eerdere PCIe-generaties.

Bruggen en schakelaars voldoen aan de vereisten voor de interface tussen verschillende typen host- en eindpuntapparaten. Een pakketbrug biedt doorgaans een interface tussen twee lagen in het OSI-referentiemodel of tussen twee protocollen. Afbeelding 2 laat ook zien hoe een bridge kan worden gebruikt om verbinding te maken tussen PCIe en oudere PCI-standaarden, waaronder PCI-X, of met USB-poorten of een UART-businterface. Packet-switches zijn apparaten met meerdere poorten en meerdere rijstroken die doorgaans worden gebruikt om een enkel rootcomplex uit te breiden naar meerdere poorten met meerdere rijstroken voor toegang tot andere peer-systemen, zoals een randapparaat of lijnkaart.

Naast individuele packet bridges en switches met verschillende poortconfiguraties en vertaalmogelijkheden, worden de functionaliteiten van een PCIe packet switch en PCIe-to-USB2.0 bridge gecombineerd in apparaten zoals Diodes Incorporated's PI7C9X442SL PCI Express-to-USB 2.0 'swidge '. Dit multifunctionele apparaat kan uitwaaieren van één PCIe x1-upstreampoort naar twee x1-downstream- en vier USB 2.0-poorten, en geeft de systeemhostprocessor tegelijkertijd toegang tot meerdere PCIe- en USB-apparaten.

Bedrijven zoals Diodes Inc. kunnen een portfolio van passieve bidirectionele PCIe 1.0-, PCIe 2.0- of PCIe 3.0-signaalmultiplexers/demultiplexers aanbieden om een enkele PCIe-rijstrook op meerdere rijstroken aan te sluiten voor bandbreedte-uitbreiding voor afbeeldingen of berekeningen. Deze apparaten kunnen ook worden gebruikt om verbindingen mogelijk te maken vanaf een enkele interface met meerdere protocollen.

Klokbuffers kunnen doorgaans een enkel referentiesignaal als ingang nemen en meerdere uitgangen produceren voor een bredere distributie rond een PCB. Klokbuffer-IC's zijn verkrijgbaar in verschillende configuraties en Diodes biedt een eigen PLL-ontwerp dat ervoor zorgt dat jitter ruim binnen de PCIe-vereisten blijft. Klokgeneratoren kunnen een kloksignaal op een specifieke frequentie genereren met een zeer lage uitgangsjitter, waardoor ze geschikt zijn voor zowel PCIe als andere systeemklokken. Ontwerpers kunnen een breed scala aan geschikte apparaten vinden, zoals de 1.8V PI6CG18xxx en 1.5V PI6CG15xxx PCIe 4.0-klokgeneratoren en buffers van Diodes in 2-, 4- en 8-kanaalsconfiguraties, die compatibel zijn met alle eerdere PCIe-generaties. Door afsluitingen op de chip te integreren, besparen deze apparaten vier externe weerstanden per uitgang, waardoor tot 32 componenten van de stuklijst worden afgesneden.

Conclusie

PCIe is de high-performance interconnect voor toepassingen van embedded en desktop computing tot datacenterconnectiviteit met hoge bandbreedte en training van neurale netwerken. Ontwerpers kunnen profiteren van de lange levensduur van eerdere PCIe-standaarden, met achterwaartse compatibiliteit tussen oudere en latere generatiespecificaties, om op een kosteneffectieve manier aan diverse systeemvereisten te voldoen. Met toegang tot een apparaatportfolio met functies zoals bridges, buffers, ReDrivers, switches en mux/demux IC's, kunnen ontwerpers efficiënte oplossingen leveren voor veeleisende toepassingen.

Ingebed

- Productie van vloeibare additieven:3D-objecten bouwen met vloeistof

- Hybride Blockchain/Cloud-applicaties bouwen met Ethereum en Google

- Serverloze mobiele applicaties bouwen met React Native en AWS

- TECHWAY:Kintex-7 FPGA PCIe-platform om de gegevenssnelheid te verbeteren met 12 HSS-links

- Botten bouwen met Raspberry Pi en Python

- Een segway bouwen met Raspberry Pi

- Nexam gaat Diab leveren met eigenschapverhogend nexamite voor hoogwaardig PET-schuim

- Hoogwaardige technische harsverbindingen met recyclebare inhoud

- Hoe IoT kan helpen met HVAC big data:deel 2

- Bouwen aan de toekomst van werknemerservaring met intelligente automatisering

- AI en robotica koppelen aan meerdere inspectiesystemen