Aan de slag met de Verilog hardwarebeschrijvingstaal

In dit artikel zullen we de basisstructuur van een Verilog-module bestuderen, enkele voorbeelden bekijken van het gebruik van het Verilog-gegevenstype "wire" en zijn vectorvorm, en kort enkele verschillen tussen VHDL en Verilog aan.

In dit artikel zullen we de basisstructuur van een Verilog-module bestuderen, enkele voorbeelden bekijken van het gebruik van het Verilog-gegevenstype "wire" en zijn vectorvorm, en kort enkele verschillen tussen VHDL en Verilog bespreken.

Verilog en VHDL zijn twee talen die vaak worden gebruikt om digitale circuits te beschrijven. AAC heeft een reeks technische artikelen waarin de basisconcepten van VHDL worden besproken. Dit artikel is een startpunt voor onze serie over Verilog.

Heb ik zowel Verilog als VHDL nodig?

Laten we, voordat we onze discussie beginnen, een voor de hand liggende vraag behandelen:moeten we deze twee talen echt kennen?

Zowel Verilog als VHDL zijn krachtige tools die kunnen worden gebruikt om een complex digitaal circuit te ontwerpen. Hoewel er enkele verschillen zijn tussen deze twee HDL's, bent u vrij om een van beide te kiezen om te beheersen en te gebruiken. Ik geloof echter dat je op een gegeven moment baat zult hebben als je op zijn minst een basiskennis van beide talen hebt. Soms hebben we als ontwerpers een voorbeeldcodesegment nodig om een idee te krijgen over het coderen van een project. We surfen uren op het internet en vinden uiteindelijk wat we nodig hebben, maar het slaat nergens op - het is geschreven in de HDL die ons volkomen onbekend is. Zonder een basiskennis van de taal, kunnen we de technieken mogelijk niet volledig begrijpen.

Verilog Evolutie

Verilog is begin 1984 ontworpen door Gateway Design Automation (ongeveer drie jaar nadat VHDL was geïnitieerd door het Amerikaanse ministerie van Defensie). Met de steun van DoD werd VHDL in 1987 een IEEE-standaard. Verilog kwam pas in 1995 op de markt. Tegenwoordig zijn zowel VHDL als Verilog populaire HDL's en ondersteunen FPGA-ontwerptools meestal beide talen.

Het woord "Verilog" is een samentrekking van de woorden "verificatie" en "logica", omdat de taal voor het eerst werd voorgesteld als een simulatie- en verificatietool. Laten we beginnen met de concepten en syntaxis van Verilog.

Voorbeeld 1

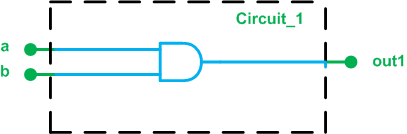

Laten we als eerste voorbeeld de Verilog-code schrijven voor het circuit dat wordt weergegeven in figuur 1.

Figuur 1. Circuit_1

Er zijn twee ingangen en één uitgang. De poorten zijn allemaal een beetje breed. De functionaliteit van het circuit is om de twee ingangen EN en het resultaat op de out1-poort te plaatsen.

Een mogelijke Verilog-beschrijving voor de Circuit_1-module is:

Lijnen 1 en 8

Deze twee regels gebruiken de trefwoorden "module" en "endmodule" om aan te geven dat de tussenliggende regels (regels 2 tot 7) allemaal een circuit met de naam "Circuit_1" beschrijven. Deze naam is willekeurig en stelt ons in staat om later naar dit circuit te verwijzen.

Lijnen 2 tot 6

Deze regels specificeren de interface van "Circuit_1" met zijn omgeving. De invoer- en uitvoerpoorten worden beschreven met de trefwoorden "invoer" en "uitvoer". Deze trefwoorden worden gevolgd door een ander trefwoord "wire" en vervolgens de naam van de poort (zie afbeelding 1). Wat specificeert het trefwoord "draad"? "Draad" is een Verilog-gegevenstype dat een fysieke draad in het ontwerp vertegenwoordigt. We zullen de gegevenstypen van Verilog in meer detail bespreken in een toekomstig artikel, maar voor nu weten we dat er drie draden zouden zijn die a, b en out1 worden genoemd in onze module en aangezien deze zijn gespecificeerd in de poortdeclaratie, komen ze overeen met de module-interface.

Lijn 7

Deze regel gebruikt de bitsgewijze AND-operator, d.w.z. &, om de functionaliteit van het circuit te beschrijven. Het trefwoord "toewijzen" plaatst a&b op de uitvoerpoort out1. Dit type opdracht wordt een doorlopende opdracht genoemd. Het wordt zo genoemd omdat de toewijzing altijd actief is wanneer een operand aan de rechterkant verandert, a&b wordt geëvalueerd en toegewezen aan out1. We kunnen ons een continue toewijzing voorstellen als een combinatorisch circuit waarvan de uitvoer continu wordt bijgewerkt, afhankelijk van de invoer. In ons voorbeeld is dit combinatorische circuit een eenvoudige EN-poort. Er zijn ook procedurele opdrachten in Verilog HDL die in toekomstige artikelen zullen worden besproken.

Nu kunnen we een softwarepakket zoals Xilinx ISE gebruiken om de bovenstaande code te verifiëren. U kunt hier een op Verilog gebaseerde handleiding van deze software vinden (PDF).

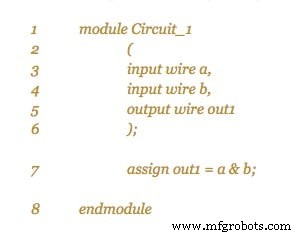

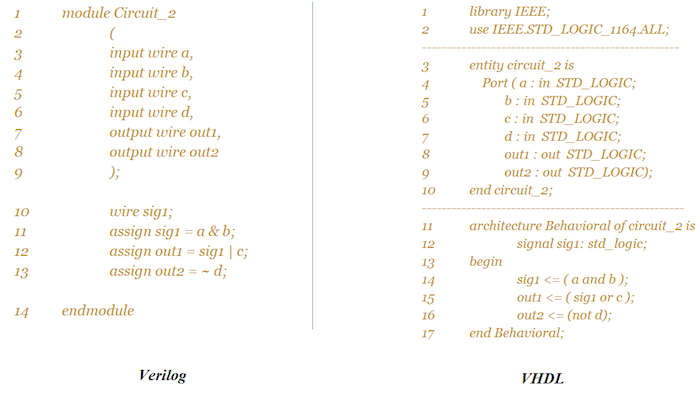

Voorbeeld 1 vergelijken met de VHDL-code

Afbeelding 2 hieronder toont de Verilog- en VHDL-beschrijvingen voor de Circuit_1-module.

Figuur 2. Vergelijking van Verilog- en VHDL-beschrijvingen voor Circuit_1.

Zoals u kunt zien, moeten we enkele bibliotheken opnemen bij het coderen in VHDL. Deze bibliotheken geven de definitie voor de gegevenstypen en operators. Gezien de toevoeging van deze bibliotheken en het algemene formaat van VHDL, zien we dat de VHDL-code uitgebreider is. Deze breedsprakigheid is echter niet zonder voordelen. De bibliotheekbeheerfunctie van VHDL kan bijvoorbeeld handig zijn bij het modelleren van systemen op een hoger niveau. In toekomstige artikelen zullen we af en toe de voor- en nadelen van deze twee HDL's bespreken.

Verilog heeft een systeem met vier waarden

Er zijn vier basiswaarden die in de meeste Verilog-gegevenstypen worden gebruikt. De draden gedefinieerd in Listing 1 kunnen een van de volgende waarden aannemen:

- 0:voor een logisch lage of een valse voorwaarde

- 1:voor een logische hoge of ware voorwaarde

- z:voor de toestand met hoge impedantie (kan worden gebruikt om de uitvoer van een buffer met drie toestanden te beschrijven)

- x:voor een onverschillig of onbekende waarde (wanneer een ingang niet is geïnitialiseerd of twee of meer conflicterende uitgangen met elkaar zijn verbonden).

Het gegevenstype VHDL std_logic kan negen verschillende waarden aannemen, maar de meest gebruikte waarden zijn '0', '1', 'Z' en '-' ('-' geeft aan dat het niet uitmaakt).

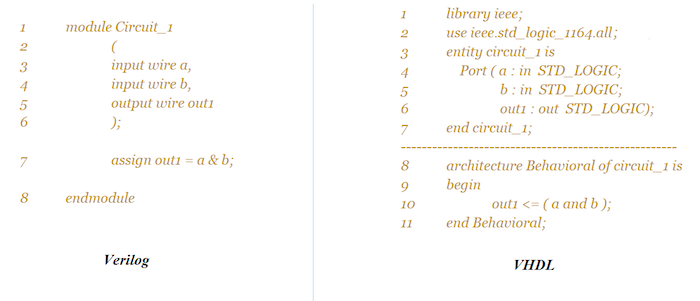

Voorbeeld 2

Laten we als een ander voorbeeld de Verilog-code schrijven voor het circuit (dat we Circuit_2 noemen) zoals weergegeven in figuur 3.

Figuur 3. Circuit_2

De volgende Verilog-code beschrijft dit circuit:

De elementen die in de bovenstaande code worden gebruikt, zijn vergelijkbaar met die in voorbeeld 1, behalve dat een intern signaal is gedefinieerd in regel 10 van de code. Het trefwoord "wire" wordt gebruikt om het gegevenstype van deze verbinding te specificeren. Zoals hierboven besproken, zou het gegevenstype "draad" zich vertalen in een fysieke draad in het ontwerp.

De bovenstaande code gebruikt ook enkele nieuwe bitsgewijze operatoren van Verilog:~ voor NOT en | voor operatie OK. Een andere nuttige bitsgewijze operator is ^ voor de XOR-bewerking. Afbeelding 4 toont zowel de Verilog- als de VHDL-beschrijvingen voor de Circuit_2-module. Dergelijke vergelijkingen kunnen u helpen de verschillen en overeenkomsten tussen deze twee talen te zien.

Figuur 4. Vergelijking van Verilog- en VHDL-beschrijvingen voor Circuit_2.

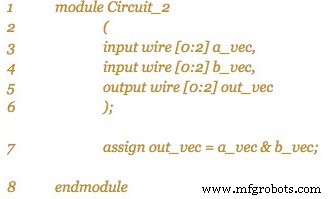

Voorbeeld 3

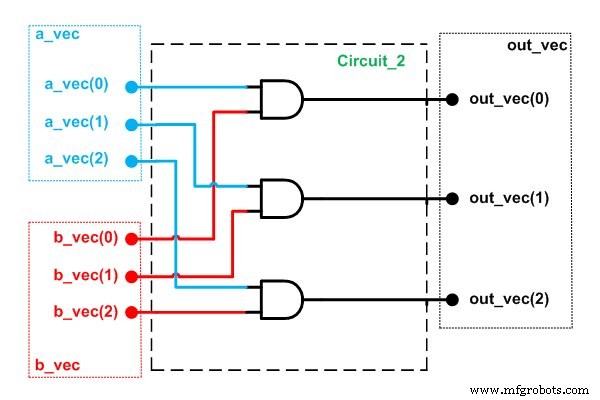

Voor ons derde en laatste voorbeeld geven we de Verilog-code voor het schema in Afbeelding 5.

Figuur 5. Schema bijvoorbeeld 3.

Zoals je kunt zien, is er een bepaalde relatie tussen de blauwe invoerpoorten en de rode:de bijbehorende invoer wordt gecombineerd met de AND-operator. Het resultaat wordt toegewezen aan een uitvoerpoort. In dergelijke gevallen kunnen we de signalen groeperen en als vector behandelen. Dit maakt de code compact en leesbaar.

Met behulp van het vectorconcept in Verilog kunnen we de code in Listing 1 gemakkelijk uitbreiden om het bovenstaande circuit te beschrijven (zie de code in Listing 3 hieronder).

Merk op dat het indexbereik van de vectoren oplopend ([0:2] zoals hierboven gebruikt) of aflopend ([2:0]) kan zijn. Hoewel hierboven het oplopende formaat wordt gebruikt, is het meestal minder foutgevoelig om het aflopende formaat te gebruiken. Dit komt door het feit dat de aflopende stijl overeenkomt met onze perceptie dat de meest linkse positie van een binair getal de hoogste index heeft. Merk op dat vectoren ook worden gebruikt in VHDL.

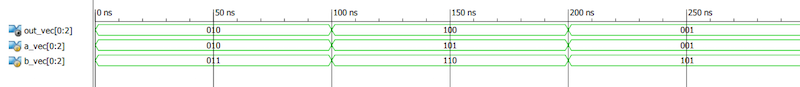

Afbeelding 6 hieronder toont een ISE-simulatie van de code in Listing 3.

Figuur 6. ISE-simulatie van de code van voorbeeld 3.

In dit artikel hebben we besproken dat het een goed idee is om zowel VHDL als Verilog te leren, we hebben de basisstructuur van een Verilog-module bestudeerd en we zijn bekend geraakt met het Verilog-gegevenstype 'wire' en zijn vectorvorm. We hebben ook kort enkele verschillen tussen VHDL en Verilog besproken. Het volgende artikel in onze Verilog-serie gaat over het ontwerpen van combinatorische circuits in Verilog.

Ingebed

- Code Ready-containers:aan de slag met procesautomatiseringstools in de cloud

- Aan de slag met keramisch 3D-printen

- Aan de slag met TJBot

- Aan de slag met de RAK 831 Lora Gateway en RPi3

- Aan de slag met de RAK831 LoRa Gateway en RPi3

- Aan de slag met AI in verzekeringen:een inleidende gids

- Aan de slag met AI-inferentie aan de rand

- Aan de slag met de Eagle Group:wat u moet weten

- Aan de slag met My.Cat.com

- Node-RED en aan de slag met Docker

- Aan de slag met Go op PLCnext