Geïntegreerd ontwerp met FPGA's:implementatie

Noot van de redactie:naarmate er steeds meer geavanceerde algoritmen verschijnen voor slimme productontwerpen, hebben ontwikkelaars vaak moeite om embedded systemen te implementeren die in staat zijn om aan de bijbehorende verwerkingsvereisten van deze algoritmen te voldoen. FPGA's kunnen de vereiste prestaties leveren, maar ontwerpen met FPGA's werd lang beschouwd als beperkt tot de bevoegdheid van FPGA-programmeerexperts. Tegenwoordig heeft de beschikbaarheid van krachtigere FPGA's en effectievere ontwikkelomgevingen FPGA-ontwikkeling echter breed toegankelijk gemaakt. In dit fragment, hoofdstuk 4 uit het boek Architecting High-Performance Embedded Systems, biedt de auteur een uitgebreid overzicht van FPGA-apparaten, implementatietalen en het FPGA-ontwikkelingsproces, evenals een gedetailleerd overzicht van hoe u aan de slag kunt gaan met het implementeren van FPGA's in uw eigen ontwerp. Het volledige fragment wordt gepresenteerd in de volgende reeks afleveringen:

Noot van de redactie:naarmate er steeds meer geavanceerde algoritmen verschijnen voor slimme productontwerpen, hebben ontwikkelaars vaak moeite om embedded systemen te implementeren die in staat zijn om aan de bijbehorende verwerkingsvereisten van deze algoritmen te voldoen. FPGA's kunnen de vereiste prestaties leveren, maar ontwerpen met FPGA's werd lang beschouwd als beperkt tot de bevoegdheid van FPGA-programmeerexperts. Tegenwoordig heeft de beschikbaarheid van krachtigere FPGA's en effectievere ontwikkelomgevingen FPGA-ontwikkeling echter breed toegankelijk gemaakt. In dit fragment, hoofdstuk 4 uit het boek Architecting High-Performance Embedded Systems, biedt de auteur een uitgebreid overzicht van FPGA-apparaten, implementatietalen en het FPGA-ontwikkelingsproces, evenals een gedetailleerd overzicht van hoe u aan de slag kunt gaan met het implementeren van FPGA's in uw eigen ontwerp. Het volledige fragment wordt gepresenteerd in de volgende reeks afleveringen:

1:Hardwarebronnen

2:Implementatietalen

3:Ontwikkelingsproces

4:Een project bouwen

5:Implementatie (dit artikel)

Aangepast van het ontwerpen van hoogwaardige ingebedde systemen, door Jim Ledin.

Het logisch gedrag testen

Het is belangrijk om het gedrag van logica te testen met behulp van simulatie voordat u het in de FPGA probeert uit te voeren. Dit komt omdat het veel gemakkelijker is om problemen in de simulatieomgeving te detecteren en op te lossen dan met de logica die in de FPGA draait. De Vivado-simulatietools zijn erg goed in het weergeven van circuitgedrag:

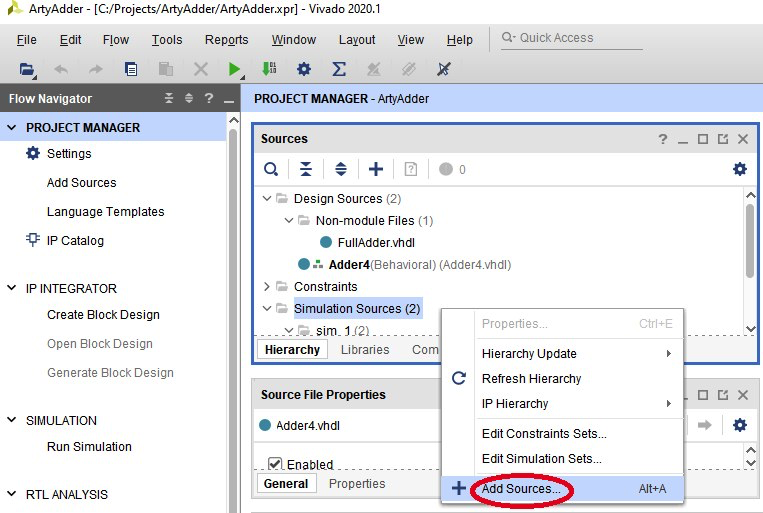

- In de Bronnen subvenster, klik met de rechtermuisknop op Simulatiebronnen en selecteer Bronnen toevoegen... :

Figuur 4.18 – Bronnen toevoegen... menuselectie voor simulatiebronnen

- In de Bronnen toevoegen dialoogvenster, zorg ervoor dat Simulatiebronnen toevoegen of maken is geselecteerd en klik vervolgens op Volgende .

- In de Simulatiebronnen toevoegen of maken dialoogvenster, klik op Bestand maken .

- Voer de bestandsnaam in vhdl en klik op OK .

- Klik op Voltooien om de Simulatiebronnen toevoegen of maken . te sluiten dialoogvenster en klik vervolgens op OK in de Definieer Module dialoogvenster en klik op Ja wanneer u wordt gevraagd of u zeker weet dat u deze wilt gebruiken

- Dubbelklik Adder4 TestBench (Behavioral) (Adder4TestBench.vhdl) onder Simulatiebronnen . Verwijder de automatisch ingevulde inhoud van de vhdl editorvenster en voer de volgende code in de Adder4TestBench.vhdl redacteur:

bibliotheek IEEE; gebruik IEEE.STD_LOGIC_1164.ALL; gebruik IEEE.NUMERIC_STD.ALL;entiteit ADDER4_TESTBENCH isend entiteit ADDER4_TESTBENCH;architectuur GEDRAG van ADDER4_TESTBENCH is component ADDER4 is poort (A4:in std_logic_vector (3 downto 0); B4:in std_logic_vector(4 downto 0); 0); C_OUT4 :uit std_logic ); eindcomponent; signaal a:std_logic_vector (3 tot 0); signaal b:std_logic_vector (3 tot 0); signaal s:std_logic_vector (3 tot 0); signaal c_out:std_logic; signaal Expected_sum5:unsigned (4 downto 0); signaal Expected_sum4:unsigned (3 downto 0); signaal verwacht_c:std_logic; signaalfout:std_logic; begin TESTED_DEVICE:ADDER4-poortkaart (A4 => a, B4 => b, SUM4 => s, C_OUT4 => c_out); TEST:proces begin -- Test alle combinaties van twee 4-bits addends (256 totale tests) voor a_val in 0 tot 15 lus voor b_val in 0 tot 15 lus -- Stel de ingangen in op de ADDER4-component a <=std_logic_vector(to_unsigned( a_val, a'length)); b <=std_logic_vector(to_unsigned(b_val, b'length)); wacht 1 ns; -- Bereken de 5-bits som van de twee 4-bits waarden Expected_sum5 <=unsigned('0' &a) + unsigned('0' &b); wacht 1 ns; -- Breek de som in een 4-bits uitvoer en een carry-bit verwachte_som4 <=verwachte_som5 (3 tot 0); verwacht_c <=verwacht_som5(4); wacht 1 ns; -- Het 'error'-signaal gaat alleen naar 1 als er een fout optreedt als ((unsigned(s) =unsigned(expected_sum4)) en (c_out =Expected_c)) then error <='0'; anders fout <='1'; stop als; -- Elke doorgang door de binnenste lus duurt 10 ns, wacht 7 ns; eindlus; eindlus; wachten; eindproces TEST;einde architectuur GEDRAG; Deze code oefent de 4-bits optelfunctie uit door alle combinaties van 4-bits getallen te presenteren aan elk van de A4 en B4 invoer naar de Adder4 onderdeel. Het vergelijkt de SUM4 en C_OUT4 uitgangen van de Adder4 component naar onafhankelijk berekende waarden voor dezelfde invoer. Na elke optelbewerking wordt de fout signaal is ingesteld op 0 als de Adder4 uitgangen kwamen overeen met de verwachte waarden, of het is ingesteld op 1 als er een mismatch is.

De code in Adder4TestBench.vhdl lijkt op traditionele softwarecode in de manier waarop het geneste for-lussen gebruikt om alle testinvoercombinaties toe te passen op de Adder4 onderdeel dat wordt getest. Code die tests uitvoert in simulatiemodus is niet-synthetiseerbaar, wat betekent dat het niet puur een hardwarelogica-circuit vertegenwoordigt en in staat is tot traditionele software-achtige bewerkingen, zoals de iteratieve uitvoering van for lussen.

Echter, net als in fysieke circuits, kunnen signalen waaraan waarden worden toegekend in de testbankcode met behulp van de <=-operator, niet op hetzelfde moment in volgende uitdrukkingen worden gebruikt. Dit komt omdat de simulatieomgeving de echte effecten van voortplantingsvertraging vertegenwoordigt, wat zelfs binnen kleine FPGA-apparaten aanzienlijk is. De drie wachten op 1 ns; verklaringen in de code van de testbank pauzeren circuitbewerkingen om propagatievertraging mogelijk te maken. Deze vertragingen van 1 ns geven tijd voor de signaalwaarden die zijn berekend net voor de wacht statement te verspreiden, zodat ze kunnen worden gebruikt in het volgende statement. De laatste wacht op 7 ns; statement in de binnenste lus is een pauze die ons in staat stelt om de resultaten van elke iteratie van de simulatielussen duidelijk te zien in de signaaltrace-weergave.

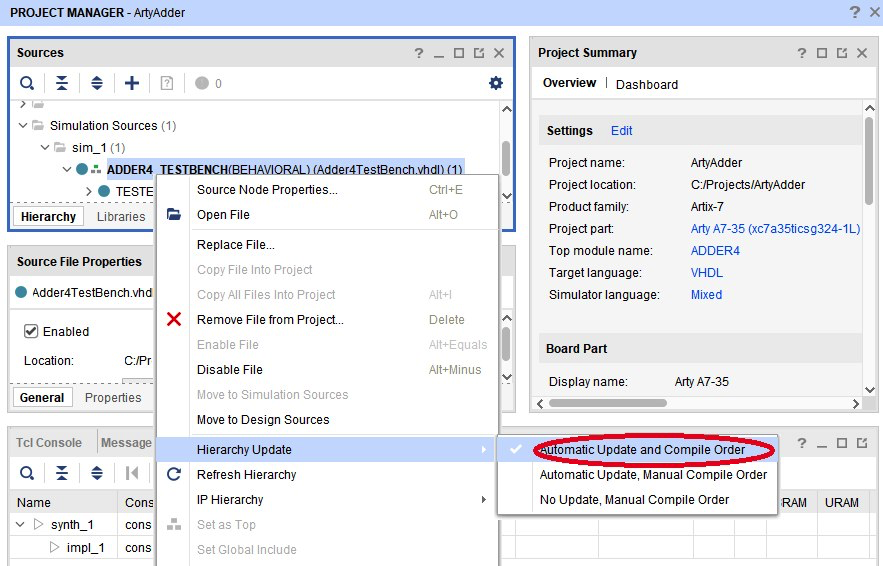

- Klik met de rechtermuisknop Adder4 TestBench (gedrag) (Adder4TestBench.vhdl) onder Simulatiebronnen en selecteer Automatisch bijwerken en bestelling samenstellen . Dit stelt ADDER4_TESTBENCH . in als het object op het hoogste niveau voor de simulatierun:

Figuur 4.19 – Menuselectie om Automatische Update en Compileervolgorde in te stellen

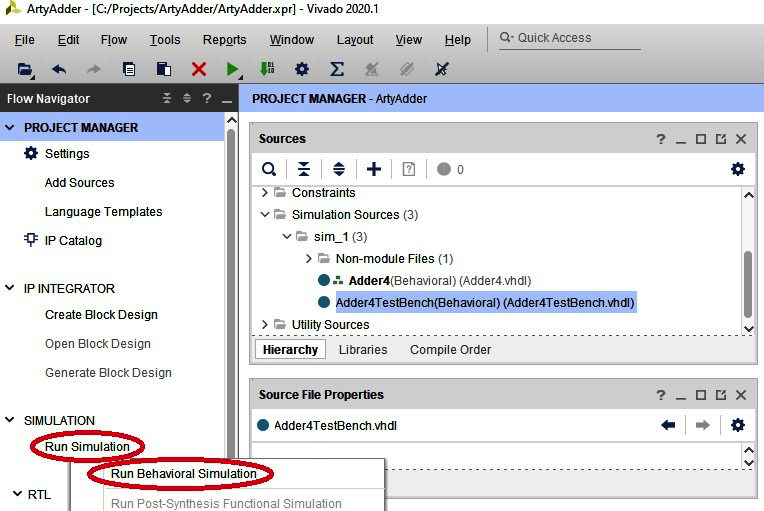

- Klik op Simulatie uitvoeren , en Voer gedragssimulatie uit in de Flow Navigator venster om naar de simulatiemodus te gaan. Als u de editorbestanden nog niet hebt opgeslagen, wordt u gevraagd dit te doen. Klik op Opslaan . De simulatie wordt dan uitgevoerd:

Figuur 4.20 – Menuselectie Gedragssimulatie uitvoeren

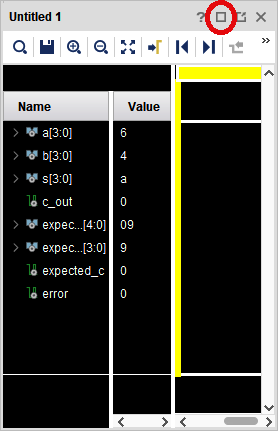

- Wanneer de SIMULATIE venster wordt geopend, klikt u op de knop Maximaliseren in het simulatie-uitvoervenster met de titel Untitled 1 :

Figuur 4.21 – Venster Simulatieresultaten

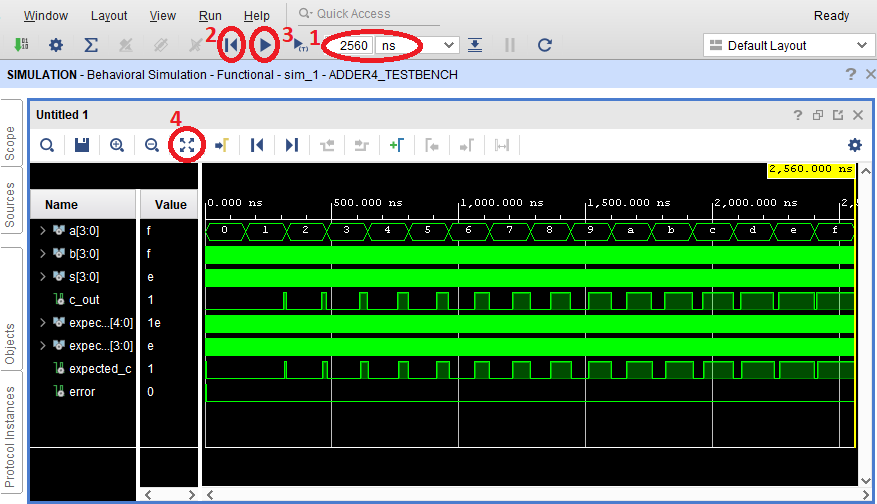

De totale gesimuleerde tijd van elke passage door de binnenste lus is 10 ns. Omdat er 256 passages door de lus zijn in Adder4TestBench.vhdl , de tijd om de simulatie uit te voeren is 2560 ns.

- Stel de looptijd van de simulatie in op 2560 ns in de bovenste werkbalk (stap 1 in de volgende afbeelding), drukt u op de naar links wijzende herstartknop (stap 2 ), druk vervolgens op de naar rechts gerichte knop om de simulatie uit te voeren gedurende 2560 ns (stap 3 ), en druk ten slotte op de Zoom Fit knop (stap 4 ) om het gegevensbereik van de simulatie-uitvoer te schalen om in het venster te passen:

Figuur 4.22 – Simulatieresultaten van het begin tot het einde van de run

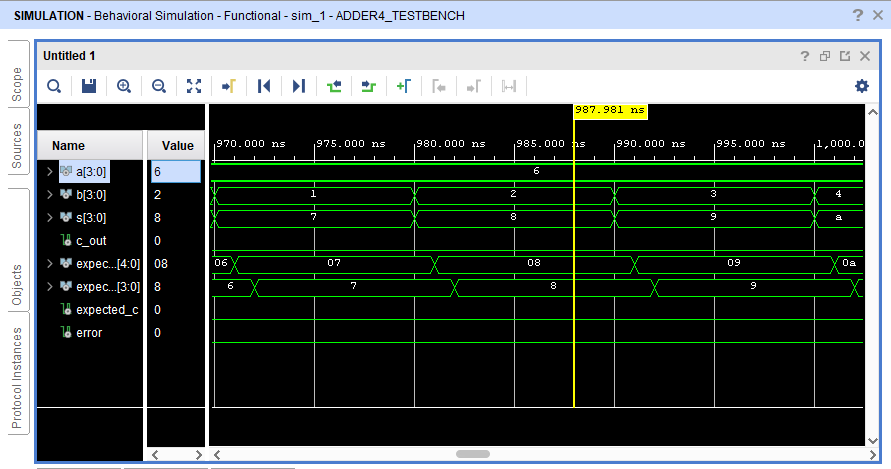

U kunt de vergrootglaspictogrammen gebruiken om op elk punt van het spoor in te zoomen en de resultaten te bekijken van elke toevoeging die tijdens het testen wordt uitgevoerd. De volgende afbeelding laat bijvoorbeeld zien dat de decimale waarden 6 en 2 zijn toegevoegd om het resultaat 8 te produceren met een carry van 0. Deze waarden komen overeen met de verwachte waarden, die een fout veroorzaakten moet worden ingesteld op 0. De fout signaal is 0 voor alle 256 testgevallen, wat aangeeft dat ons logische circuit alle tests heeft doorstaan:

Figuur 4.23 – Ingezoomde weergave van de simulatieresultaten

- Sluit de simulatiemodus door op de X . te klikken in het blauw SIMULATIE balk boven het gegevensspoor Klik op OK wanneer u wordt gevraagd of u de simulatie wilt sluiten.

Nadat we de gedragstests hebben doorstaan, zullen we de I/O-signalen definiëren die in het ontwerp worden gebruikt.

I/O-signalen definiëren

Onze volgende stap is om de in- en uitgangen van ons circuit te verbinden met hardwareapparaten op het Arty-bord. De ingangen zijn de kaartschakelaars en drukknoppen, en de uitgangen zijn LED's.

De volgende stappen creëren een bestand met beperkingen dat de I/O-pinnen beschrijft die we op het FPGA-apparaat zullen gebruiken en de functies die zijn verbonden met die pinnen op het Arty-bord. Beperkingsbestanden hebben de extensie xdc:

- In de Bronnen subvenster, klik met de rechtermuisknop op Beperkingen en selecteer Bronnen toevoegen... .

- In de Bronnen toevoegen dialoogvenster, zorg ervoor dat Beperkingen toevoegen of maken is geselecteerd en klik vervolgens op Volgende .

- In de Beperkingen toevoegen of maken dialoogvenster, klik op Bestand maken .

- Voer de bestandsnaam in Arty-A7-100.xdc (of Arty-A7-35.xdc indien van toepassing op uw apparaat) en klik op OK .

- Klik op Voltooien om de Beperkingen toevoegen of maken . te negeren

- Vergroot de beperkingen bronstructuur en dubbelklik op Arty-A7-35.xdc .

- Digilent biedt vooraf ingevulde beperkingsbestanden voor de Arty A7-borden. Bezoek https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-35-Master .xdc en kopieer de volledige inhoud van het browservenster naar het Arty-A7-35.xdc-editorvenster in Vivado. Gebruik, indien geschikt voor uw apparaat, het bestand op https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-100-Master.xdc in plaats daarvan.

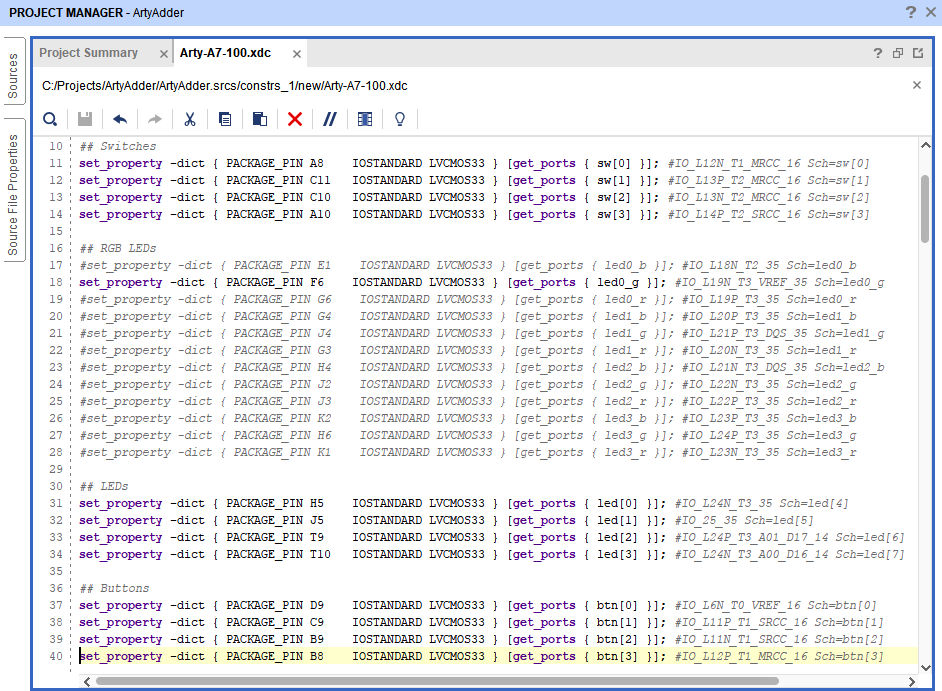

- Alle I/O-pinnen worden van commentaar voorzien in het bestand met beperkingen door commentaar op de betreffende regels in het bestand op te heffen door het #-teken aan het begin van elke regel te verwijderen. We zullen de pinnen gebruiken die in de volgende secties worden vermeld in de Arty- A7-100.xdc bestand:Schakelaars , RGB LED's (maar alleen led0_g , de eerste groene LED), LED's , en Knoppen . De volgende afbeelding toont deze regels nadat ze niet meer van commentaar zijn voorzien:

Figuur 4.24 – Beperkingen-editorvenster

In de volgende sectie zullen we een VHDL-bestand op het hoogste niveau maken dat de addercode koppelt aan de I/O-apparaten.

Een VHDL-bestand op het hoogste niveau maken

We zullen vervolgens een VHDL-bestand op het hoogste niveau maken dat onze 4-bits adder-component verbindt met de overeenkomstige I/O-signalen van het bord:

- In de Bronnen subvenster, klik met de rechtermuisknop op Ontwerpbronnen en selecteer Bronnen toevoegen... .

- In de Bronnen toevoegen dialoogvenster, zorg ervoor dat Ontwerpbronnen toevoegen of maken is geselecteerd en klik vervolgens op Volgende .

- In de Ontwerpbronnen toevoegen of maken dialoogvenster, klik op Bestand maken .

- Voer de bestandsnaam in vhdl en klik op OK .

- Klik op Voltooien om de Ontwerpbronnen toevoegen of maken . te sluiten dialoogvenster en klik vervolgens op OK in de Definieer Module dialoogvenster en klik op Ja wanneer u wordt gevraagd of u zeker weet dat u deze wilt gebruiken

- Dubbelklik vhdl onder Ontwerpbronnen . Verwijder de automatisch ingevulde inhoud van de ArtyAdder.vhdl editorvenster en voer de volgende code in de ArtyAdder.vhdl redacteur:

-- Laad de standaardbibliothekenbibliotheek IEEE; gebruik IEEE.STD_LOGIC_1164.ALL;entity ARTY_ADDER is poort (sw:in STD_LOGIC_VECTOR (3 omlaag naar 0); btn:in STD_LOGIC_VECTOR (3 omlaag naar 0); led:uit STD_LOGIC_VECTOR (3 omlaag naar 0); led0_g:uit STD_LOGIC); ARTY_ADDER; architectuur BEHAVIORAL van ARTY_ADDER is -- Verwijs naar de vorige definitie van de 4-bits addercomponent ADDER4 is poort (A4:in std_logic_vector (3 tot 0); B4:in std_logic_vector (3 tot 0); SUM4:out std_logic_vector (3 tot 0); C_OUT4 :uit std_logic ); eindcomponent;begin ADDER :ADDER4-poortkaart ( A4 => sw, B4 => btn, SUM4 => led, C_OUT4 => led0_g );eindarchitectuur BEHAVIORAL;

Deze code brengt de signaalnamen in kaart voor de I/O-apparaten genoemd in Arty-A7-100.xdc as sw (4 schakelaars), btn (4 drukknoppen), led (4 eenkleurige LED's) en led0_g (het groene kanaal van de eerste meerkleurige LED) naar de ADDER4 in- en uitgangen.

Hoewel VHDL niet hoofdlettergevoelig is, is de verwerking van xdc constraint-bestanden in Vivado zijn hoofdlettergevoelig. Het geval dat wordt gebruikt in I/O-apparaatnamen die zijn gedefinieerd in de xdc bestand moet identiek zijn wanneer ernaar wordt verwezen in een VHDL-bestand. De namen van het I/O-signaal in VHDL moeten in dit bestand met name in kleine letters zijn, omdat ze in het bestand met beperkingen in kleine letters staan.

We zijn nu klaar om ons ontwerp voor het Arty-bord te synthetiseren, implementeren en programmeren.

Het synthetiseren en implementeren van de FPGA-bitstream

U kunt ook Bitstream genereren . selecteren en Vivado zal alle vereiste stappen uitvoeren, inclusief synthese, implementatie en bitstreamgeneratie zonder verdere tussenkomst van de gebruiker. Als er een fatale fout optreedt, stopt het proces en worden foutmeldingen weergegeven. Voer de volgende stappen uit om de bitstream te genereren:

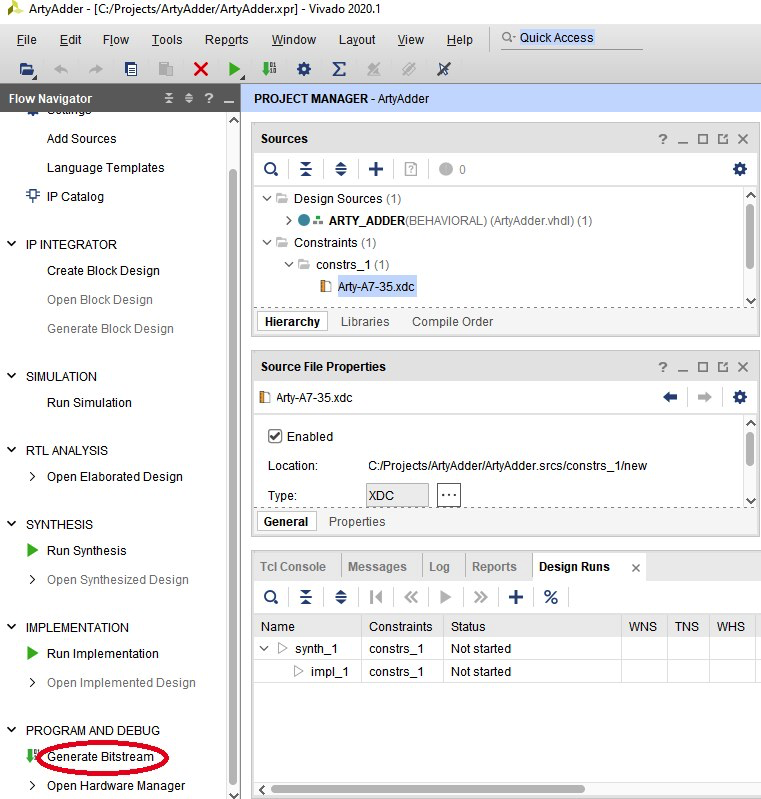

- Klik op Bitstream genereren om de build te starten Mogelijk wordt u gevraagd of u teksteditors wilt opslaan. Klik op Opslaan . Mogelijk wordt u geïnformeerd dat er geen implementatieresultaten beschikbaar zijn en wordt u gevraagd of het OK is om de synthese en implementatie te starten. Klik op Ja :

Figuur 4.25 – Bitstream-menuselectie genereren

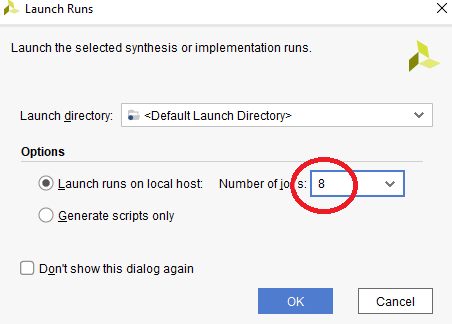

- De Launch Runs dialoogvenster verschijnt. U kunt een waarde selecteren voor Aantal taken tot het aantal processorcores in uw computer. Als u meer kernen gebruikt, gaat het proces sneller, maar het kan uw machine vastlopen als u het tijdens een langdurig bouwproces wilt blijven gebruiken. Klik op OK om de bouw te starten:

Figuur 4.26 – Dialoogvenster Runs starten

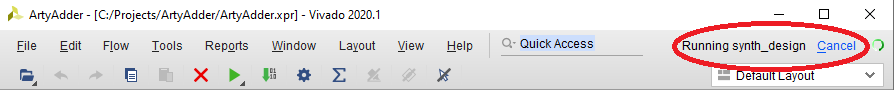

- Tijdens het bouwproces zal Vivado de status in de rechterbovenhoek van het hoofdvenster weergeven. Indien nodig kunt u het bouwproces annuleren door op Annuleren . te klikken naast de statusweergave:

Figuur 4.27 – Compilatiestatusweergave

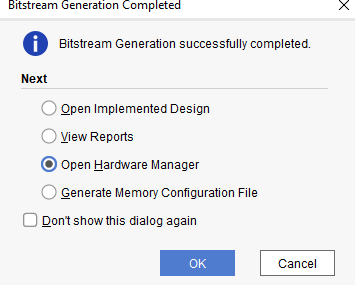

- Als het bouwproces is voltooid, ervan uitgaande dat er geen fatale fouten zijn opgetreden, wordt een Bitstream Generation Completed dialoog zal Hoewel andere opties worden aangeboden, zullen we direct doorgaan met het downloaden van de bitstream naar het Arty-bord. Selecteer Hardwarebeheer openen en klik op OK :

Figuur 4.28 – Dialoogvenster Bitstreamgeneratie voltooid

Vervolgens downloaden we de bitstream naar de FPGA.

De bitstream downloaden naar het bord

Voer de volgende stappen uit om de bitstream naar een Arty A7-bord te downloaden:

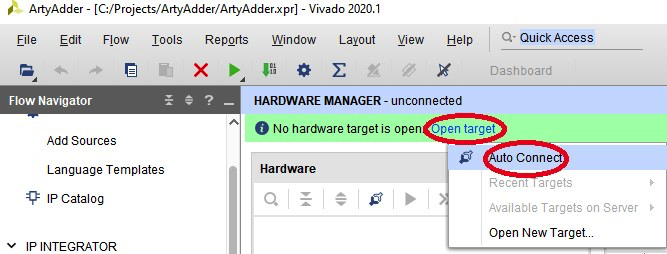

- De HARDWARE MANAGER dialoogvenster verschijnt en geeft aan dat Er is geen hardwaredoel geopend .

- Sluit uw Arty A7-35- of A7-100-bord aan op de computer via een USB. Wacht een paar seconden totdat het bord wordt herkend en klik vervolgens op Doel openen en vervolgens Automatisch verbinden :

Figuur 4.29 – Selecties Open doel en Automatisch verbinden

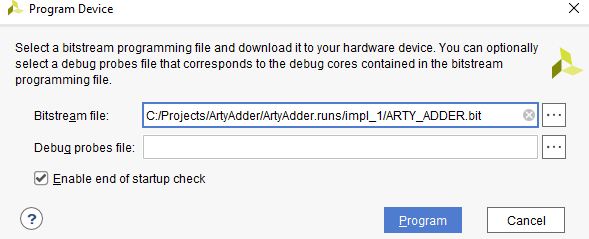

- Na een paar seconden zou Vivado moeten aangeven dat het bord is aangesloten. Klik op Apparaat programmeren om de FPGA-bitstream naar de Arty te downloaden U wordt gevraagd een bitstream-bestand te selecteren. Als u dezelfde directorystructuur als dit voorbeeld heeft gebruikt, bevindt het bestand zich op C:/Projects/ArtyAdder/ ArtyAdder.runs/impl_1/ARTY_ADDER.bit :

Figuur 4.30 – Dialoogvenster Programmeerapparaat

- Klik op Programma om het programma naar het FPGA-apparaat te downloaden en te starten

- U kunt nu de werking van het programma testen met de Arty I/O. Zet alle vier de schakelaars in de uit positie (verplaats de schakelaars naar de aangrenzende rand van het bord) en druk niet op een van de vier drukknoppen. Alle vier de groene LED's moeten uit zijn.

- Als u een afzonderlijke schakelaar inschakelt of op een drukknop drukt, moet de bijbehorende groene LED gaan branden. Als u een willekeurige combinatie van schakelaars inschakelt terwijl u op een willekeurig aantal drukknoppen drukt, worden de bijbehorende 4-bits nummers toegevoegd en gaan de LED's branden met de Als er een overdracht is (schakel bijvoorbeeld SW3 in en druk op BTN3 tegelijk), gaat de groene draag-LED branden.

Het hier uitgevoerde programmeerproces heeft het programma opgeslagen in FPGA RAM. Als u de FPGA-kaart uitschakelt, moet u het programmeerproces herhalen om het programma opnieuw te laden. Als alternatief kunt u het FPGA-configuratiebestand opslaan in het ingebouwde flashgeheugen, zoals beschreven in de volgende sectie.

De bitstream programmeren in ingebouwd flash-geheugen

Om de FPGA te configureren telkens wanneer de Arty-kaart van stroom wordt voorzien, moet het FPGA-configuratiebestand worden opgeslagen in het flashgeheugen op de kaart. Als de MODE-jumper is geïnstalleerd, zal de FPGA bij het inschakelen proberen een configuratiebestand te downloaden van het ingebouwde flashgeheugen. Dit geheugen zit in een aparte chip naast de Artix-7 FPGA. Volg deze stappen om het configuratiebestand naar het flashgeheugen te programmeren:

- Installeer de MODE jumper op het Arty-bord als het er nog niet is

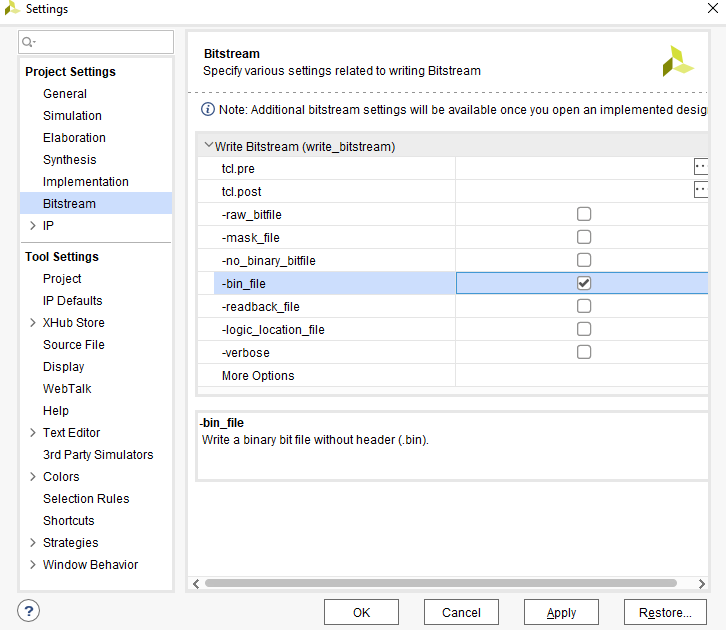

- Klik met de rechtermuisknop Bitstream genereren en selecteer Bitstream-instellingen… .

- In de Instellingen dialoogvenster, vink het vakje aan naast -bin_file en klik op OK :

Figuur 4.31 – Dialoogvenster Bitstream-instellingen

- Klik in het hoofdvenster van Vivado op Bitstream genereren en herhaal het proces voor het genereren van bitstreams. Klik op Annuleren wanneer de Bitstream-generatie voltooid dialoog

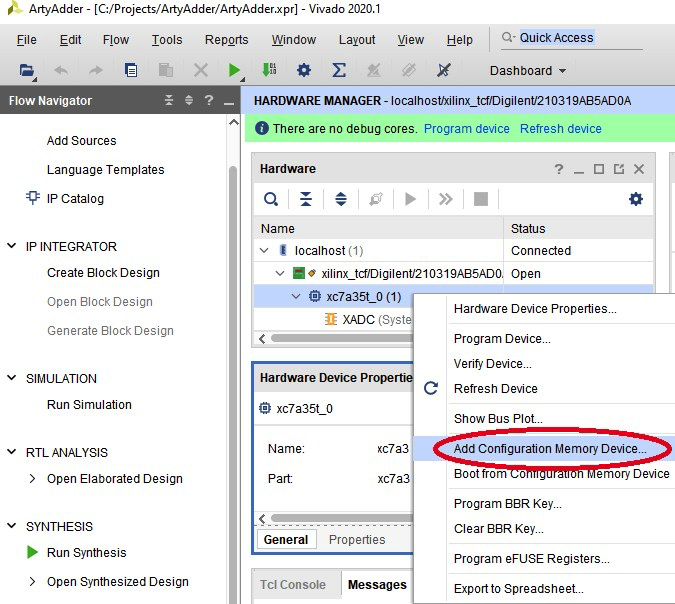

- In de Hardware dialoogvenster, klik met de rechtermuisknop op het FPGA-onderdeelnummer (xc7a100t_0 ) en selecteer Configuratiegeheugenapparaat toevoegen… :

Figuur 4.32 – Configuratiegeheugenapparaat toevoegen... menuselectie

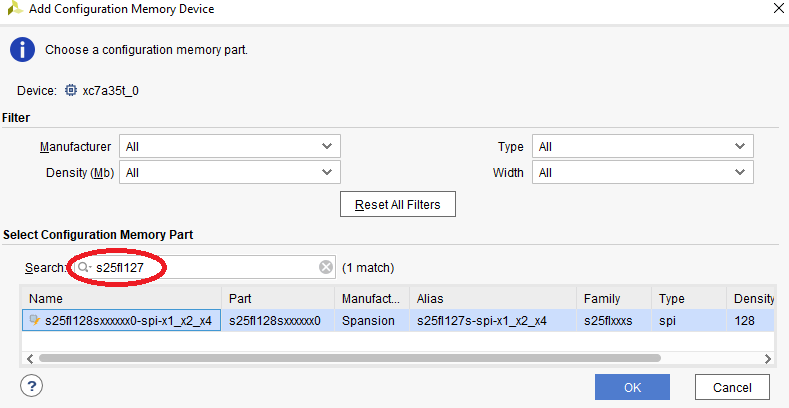

- Typ s25fl127 in de Zoeken Dit zou één overeenkomend onderdeelnummer moeten opleveren. Selecteer het onderdeel en klik op OK :

Figuur 4.33 – Dialoogvenster Configuratiegeheugenapparaat toevoegen

- U krijgt een dialoogvenster te zien met de vraag Wilt u het configuratiegeheugenapparaat nu programmeren? Klik op OK .

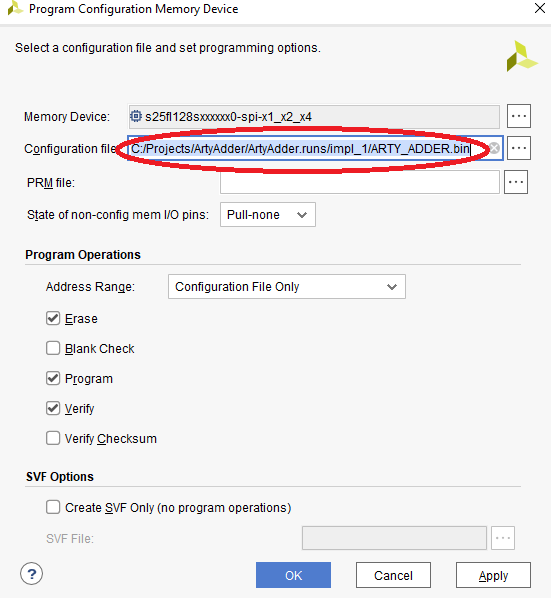

- Dit zal een Program Configuration Memory Device . oproepen dialoogvenster waarin om de configuratiebestandsnaam wordt gevraagd. Klik op de … knop rechts van Configuratiebestand en selecteer C:/Projects/ArtyAdder/ArtyAdder.runs/impl_1/ARTY_ADDER.bin. Klik op OK :

Figuur 4.34 – Dialoogvenster Geheugenapparaat programmaconfiguratie

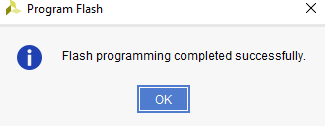

- Het programmeerproces duurt enkele seconden. U zou een bericht moeten ontvangen dat het gelukt is nadat het bestand in het flashgeheugen van de kaart is geprogrammeerd:

Figuur 4.35 – Dialoogvenster Programma Flash voltooid

Hierna wordt, elke keer dat u de voeding van het bord wisselt, het 4-bits optellerprogramma geladen en uitgevoerd. Het duurt lang voordat het programma is geladen met de instellingen die we hebben gebruikt voor het laden van het configuratiebestand. Om te voorkomen dat u moet wachten tot de FPGA het programma laadt, kunt u de laadsnelheid van het configuratiebestand verbeteren door de volgende stappen uit te voeren:

- Selecteer Open synthetisch ontwerp in Flow Navigator .

- Selecteer in het hoofdmenu van Vivado Extra/Apparaateigenschappen bewerken… .

- In de Algemeen tabblad, stel Bitstream-compressie inschakelen . in naar WAAR .

- In de Configuratie tabblad, stel Configuratiesnelheid (MHz) . in naar 33 en klik vervolgens op OK .

- Genereer de bitstream opnieuw en programmeer het flashgeheugen zoals beschreven. U moet het configuratiegeheugenapparaat verwijderen en opnieuw toevoegen om de optie voor herprogrammering weer te geven.

- Sluit Hardware Beheerder .

- Koppel de USB-kabel van het Arty-bord los en sluit deze aan. Het programma zou vrijwel onmiddellijk moeten starten bij het opstarten.

Deze sectie presenteerde een voorbeeld van eenvoudige combinatorische logica die interageert met signalen op de FPGA I/O-pinnen. De bedoeling hier was om u vertrouwd te maken met de Vivado

toolsuite en om te demonstreren hoe de tools worden gebruikt om een volledige FPGA-ontwikkelingscyclus uit te voeren.

Samenvatting

Dit hoofdstuk begon met een discussie over het effectieve gebruik van FPGA's in realtime embedded systeemarchitecturen en ging verder met een beschrijving van standaard FPGA-apparaten en de low-level componenten die ze bevatten. Het scala aan FPGA-ontwerptalen, waaronder HDL's, blokdiagrammethoden en populaire softwareprogrammeertalen zoals C/C++, werd geïntroduceerd. Een schets van het FPGA-ontwikkelingsproces werd gepresenteerd. Het hoofdstuk werd afgesloten met een compleet voorbeeld van een FPGA-ontwikkelcyclus, beginnend met een eisenoverzicht en eindigend met een functioneel systeem geïmplementeerd op een goedkoop FPGA-ontwikkelbord.

Als u dit hoofdstuk hebt voltooid, moet u weten hoe FPGA's effectief kunnen worden toegepast in realtime embedded systeemarchitecturen en moet u de componenten binnen een FPGA-geïntegreerd circuit begrijpen. Je hebt geleerd over de programmeertalen die worden gebruikt bij het ontwerpen van FPGA-algoritmen, de stappen in de FPGA-ontwikkelingscyclus en begrijpt de volgorde van stappen in het FPGA-ontwikkelingsproces.

Het volgende hoofdstuk gaat dieper in op het FPGA-ontwikkelingsproces om een complete benadering te bieden voor het ontwerpen van realtime embedded systemen die FPGA's bevatten. Het zal ook beginnen met de ontwikkeling van een prototype high-performance embedded systeem, een digitale oscilloscoop, dat als voorbeeld zal dienen voor de volgende hoofdstukken.

Herdrukt met toestemming van Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin is de CEO van Ledin Engineering, Inc. Jim is een expert in het ontwerpen, ontwikkelen en testen van embedded software en hardware. Hij is ook bekwaam in het beoordelen van cyberbeveiliging van embedded systemen en het testen van penetratie. Hij heeft een B.S. graad in lucht- en ruimtevaarttechniek van Iowa State University en een M.S. graad in elektrotechniek en computertechniek aan het Georgia Institute of Technology. Jim is een geregistreerde professionele elektrotechnisch ingenieur in Californië, een Certified Information System Security Professional (CISSP), een Certified Ethical Hacker (CEH) en een Certified Penetration Tester (CPT).

Jim Ledin is de CEO van Ledin Engineering, Inc. Jim is een expert in het ontwerpen, ontwikkelen en testen van embedded software en hardware. Hij is ook bekwaam in het beoordelen van cyberbeveiliging van embedded systemen en het testen van penetratie. Hij heeft een B.S. graad in lucht- en ruimtevaarttechniek van Iowa State University en een M.S. graad in elektrotechniek en computertechniek aan het Georgia Institute of Technology. Jim is een geregistreerde professionele elektrotechnisch ingenieur in Californië, een Certified Information System Security Professional (CISSP), een Certified Ethical Hacker (CEH) en een Certified Penetration Tester (CPT). Verwante inhoud:

- Ingesloten ontwerp met FPGA's:hardwarebronnen

- Ingesloten ontwerp met FPGA's:implementatietalen

- Ingesloten ontwerp met FPGA's:ontwikkelingsproces

- Open-source tools helpen FPGA-programmering te vereenvoudigen

- Implementatie van drijvende-kommaalgoritmen in FPGA's of ASIC's

- Gebruik maken van FPGA's voor diepgaand leren

- Softwaretools migreren GPU-code naar FPGA's voor AI-toepassingen

Abonneer u voor meer Embedded op de wekelijkse e-mailnieuwsbrief van Embedded.

Ingebed

- Wat is ingebed systeemontwerp:stappen in het ontwerpproces

- 3D-geprinte onderdelen afwerken met… kleurpotloden?

- Interview met expert:hoofdtechnoloog van ANSYS over het bereiken van succesvol 3D-printen met metaal met simulatie

- Big data omzetten in slimme data met ingebouwde AI

- Uitdagingen voor implementatie van USB Type-C-poorten en ontwerpoplossingen

- Belangrijke trends in de branche geven vorm aan embedded design

- Open-source platform richt zich op IoT met embedded Linux

- Clientron:multifunctionele POS-terminal met geïntegreerde printer

- Ontwerpkit meet bloeddruk met optische sensor

- Ingesloten ontwerp met FPGA's:implementatietalen

- All-in met additief