Ingesloten ontwerp met FPGA's:implementatietalen

Noot van de redactie:naarmate er steeds meer geavanceerde algoritmen verschijnen voor slimme productontwerpen, hebben ontwikkelaars vaak moeite om embedded systemen te implementeren die in staat zijn om aan de bijbehorende verwerkingsvereisten van deze algoritmen te voldoen. FPGA's kunnen de vereiste prestaties leveren, maar ontwerpen met FPGA's werd lang beschouwd als beperkt tot de bevoegdheid van FPGA-programmeerexperts. Tegenwoordig heeft de beschikbaarheid van krachtigere FPGA's en effectievere ontwikkelomgevingen FPGA-ontwikkeling echter breed toegankelijk gemaakt. In dit fragment, hoofdstuk 4 uit het boek Architecting High-Performance Embedded Systems, biedt de auteur een uitgebreid overzicht van FPGA-apparaten, implementatietalen en het FPGA-ontwikkelingsproces, evenals een gedetailleerd overzicht van hoe u aan de slag kunt gaan met het implementeren van FPGA's in uw eigen ontwerp. Het volledige fragment wordt gepresenteerd in de volgende reeks afleveringen:

Noot van de redactie:naarmate er steeds meer geavanceerde algoritmen verschijnen voor slimme productontwerpen, hebben ontwikkelaars vaak moeite om embedded systemen te implementeren die in staat zijn om aan de bijbehorende verwerkingsvereisten van deze algoritmen te voldoen. FPGA's kunnen de vereiste prestaties leveren, maar ontwerpen met FPGA's werd lang beschouwd als beperkt tot de bevoegdheid van FPGA-programmeerexperts. Tegenwoordig heeft de beschikbaarheid van krachtigere FPGA's en effectievere ontwikkelomgevingen FPGA-ontwikkeling echter breed toegankelijk gemaakt. In dit fragment, hoofdstuk 4 uit het boek Architecting High-Performance Embedded Systems, biedt de auteur een uitgebreid overzicht van FPGA-apparaten, implementatietalen en het FPGA-ontwikkelingsproces, evenals een gedetailleerd overzicht van hoe u aan de slag kunt gaan met het implementeren van FPGA's in uw eigen ontwerp. Het volledige fragment wordt gepresenteerd in de volgende reeks afleveringen:

1:Hardwarebronnen

2:Implementatietalen (dit artikel)

3:Ontwikkelingsproces

4:Een project bouwen

5:Implementatie

Aangepast van Architecting High-Performance Embedded Systems, door Jim Ledin.

FPGA-implementatietalen

Het implementeren van een ontwerp voor een FPGA komt uiteindelijk neer op het gebruik van een of meer software-programmeer-achtige talen om de functionaliteit van het apparaat te definiëren.

De traditionele talen die worden gebruikt voor FPGA-ontwikkeling zijn VHDL en Verilog.

De huidige generatie FPGA-ontwikkeltools ondersteunen over het algemeen beide talen, samen met de mogelijkheid om systeemconfiguraties te definiëren met behulp van blokdiagramtechnieken. Sommige toolsuites ondersteunen ook de definitie van FPGA-functionaliteit met behulp van de traditionele programmeertalen C en C++.

VHDL

VHSIC-hardwarebeschrijvingstaal (VHDL ), waarbij VHSIC staat voor Very Hoge snelheid geïntegreerd circuit , heeft een syntaxis die doet denken aan de programmeertaal Ada. VHDL werd in 1983 ontwikkeld onder leiding van het Amerikaanse ministerie van Defensie.

Net als Ada is VHDL nogal uitgebreid en rigide gestructureerd. In programmeertaaltermen is VHDL sterk getypeerd. De taal bevat een vooraf gedefinieerde set basisgegevenstypen, voornamelijk boolean, bit, bit_vector, karakter, string, integer, real, time en array. Alle andere gegevenstypen worden gedefinieerd in termen van de basistypen.

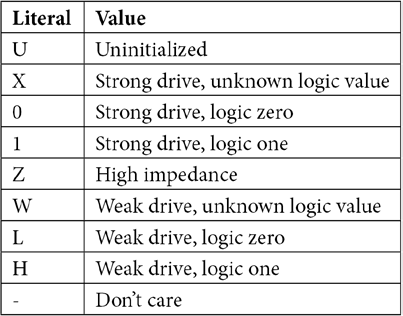

Een set VHDL-bibliotheken is gedefinieerd door het Institute of Electrical and Electronics Engineers (IEEE ) en geformaliseerd als de IEEE 1164-standaard, Multivalue Logic System voor Interoperabiliteit VHDL-model . Deze bibliotheken definiëren de set logische waarden die in de VHDL-taal moet worden gebruikt. Deze bibliotheek bevat een type met de naam std_logic, dat een 1-bits signaal vertegenwoordigt. De logische waarden binnen het type std_logic worden weergegeven door de lettertekens die in de volgende tabel worden getoond:

De "sterke" 0- en 1-waarden in de voorgaande afbeelding vertegenwoordigen signalen die naar de gespecificeerde binaire toestand zijn gestuurd. De "zwakke" signalen vertegenwoordigen signalen die worden aangedreven op een bus met meerdere stuurprogramma's, waarbij elke bestuurder zichzelf op de bus kan laten gelden en de andere stuurprogramma's overschrijft. De Z-waarde vertegenwoordigt een CMOS-uitgang in de toestand met hoge impedantie, waar in plaats van de bus naar een 0- of 1-toestand te sturen, de uitgang in plaats daarvan effectief wordt losgekoppeld van de bus en deze helemaal niet aanstuurt. De U-status vertegenwoordigt de standaardwaarden voor alle signalen. Bij het uitvoeren van circuitsimulatie wordt elk signaal in de U-status gedetecteerd, wat waarschijnlijk aangeeft dat een niet-geïnitialiseerde waarde onbedoeld wordt gebruikt. De X-status wordt geassocieerd met draden die geen uitgangen hebben die ze aansturen. De status – staat voor ingangen die niet worden gebruikt, en daarom maakt het niet uit in welke staat ze zich bevinden.

VHDL-circuitontwerpen beginnen over het algemeen met het importeren van de IEEE 1164-bibliotheken via de volgende instructies:

bibliotheek IEEE;

gebruik IEEE.std_logic_1164.all;

We zullen VHDL later in het hoofdstuk in ons projectvoorbeeld gebruiken. Dit is niet bedoeld als een sterke voorkeur voor VHDL boven Verilog. Beide hardwaredefinitietalen zijn volledig in staat om in wezen elk ontwerp weer te geven dat kan worden gesynthetiseerd voor een FPGA.

Verilog

De Verilog Hardwarebeschrijvingstaal (HDL ) werd in 1984 geïntroduceerd en werd in 2005 gestandaardiseerd als IEEE 1364. In 2009 werd de Verilog-standaard gecombineerd met de SystemVerilog standaard om IEEE Standard 1800-2009 te produceren. SystemVerilog bevat uitgebreide faciliteiten voor het uitvoeren van systeemverificatie, naast de hardware-ontwerpfuncties die aanwezig zijn in Verilog.

Verilog is ontworpen om op de C-programmeertaal te lijken, inclusief vergelijkbare operatorprioriteit en het gebruik van enkele van dezelfde control flow-sleutelwoorden, inclusief if, else, for en while.

Verilog gebruikt het concept van een draad om signaaltoestanden weer te geven. Een signaalwaarde kan elk van de waarden 0, 1 hebben, maakt niet uit (x), of hoge impedantie (z), en kan een sterke hebben of zwak signaalsterkte.

Zowel VHDL als Verilog definiëren taalsubsets die kunnen worden gebruikt om logische schakelingen te ontwerpen. Deze subsets worden de synthetiseerbare . genoemd taal subsets. Extra taalfuncties naast de synthetiseerbare subsets zijn beschikbaar om taken zoals circuitsimulatie te ondersteunen. We zullen hier later in dit hoofdstuk een voorbeeld van zien.

Niet-synthetiseerbare taalconstructies hebben de neiging zich meer te gedragen als traditionele softwareprogrammeertalen. Een niet-synthetiseerbare for-lus bijvoorbeeld, itereert achtereenvolgens een bepaald aantal keren door een codeblok, net als in een gewone programmeertaal. Een synthetiseerbare for-lus daarentegen wordt effectief uitgerold om een verzameling gerepliceerde hardwareconstructies te genereren die parallel worden uitgevoerd en elke iteratie van de lus vertegenwoordigen.

Blokdiagrammen

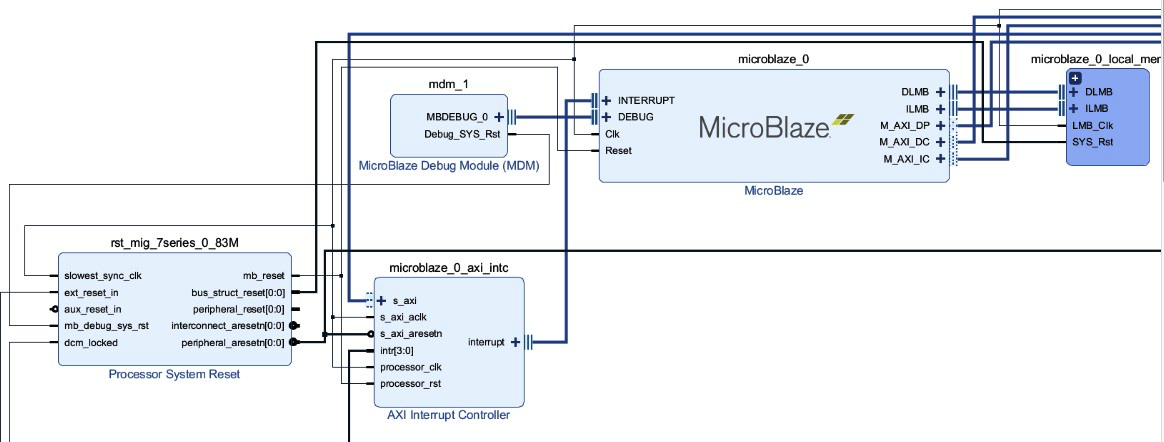

Op een abstractieniveau boven de op tekst gebaseerde HDL's, ondersteunen moderne FPGA-ontwikkeltoolsuites de snelle configuratie van systeemontwerpen met complexe logische componenten zoals microprocessors en geavanceerde I/O-apparaten met behulp van een blokstructuurformaat. Figuur 4.2 is een voorbeeld van een deel van een blokschema voor een Xilinx FPGA-ontwerp met een MicroBlaze-softprocessor:

klik voor afbeelding op volledige grootte

Figuur 4.2 – Blokschema met een MicroBlaze zachte microprocessor

De MicroBlaze-processor is een processorkern die wordt geleverd met de Xilinx Vivado-toolsuite voor gebruik in FPGA-ontwerpen in processorfamilies, waaronder de Artix-7.

Hoewel het gebruik van blokdiagrammen een visueel intuïtieve manier biedt om de concretisering en onderlinge verbinding van complexe logische elementen in een FPGA-ontwerp te organiseren, is het belangrijk om te onthouden dat achter het diagram de ontwikkeltool VHDL- of Verilog-code genereert om de componenten en hun verbindingen. Het blokschema is gewoon een gebruikersinterface voor het beheren van de configuratie van deze componenten.

Nadat u een blokschema hebt ontwikkeld, kunt u de gegenereerde HDL-code onderzoeken, die zal worden opgenomen in bestanden die bij het project horen. In het diagram van Figuur 4.2 , wordt een bestand met de naam design_1_microblaze_0_0_stub.vhdl geproduceerd op basis van het diagram. Dit bestand begint met de volgende VHDL-code:

bibliotheek IEEE;

gebruik IEEE.STD_LOGIC_1164.ALL;

entiteit design_1_microblaze_0_0 is

Poort (

Clk:in STD_LOGIC;

Reset:in STD_LOGIC;

Onderbreken:in STD_LOGIC;

Interrupt_Address:in STD_LOGIC_VECTOR (0 tot 31);

Interrupt_Ack:uit STD_LOGIC_VECTOR (0 tot 1);

Instr_Addr:uit STD_LOGIC_VECTOR (0 tot 31);

Instr:in STD_LOGIC_VECTOR (0 tot 31);

Deze code begint met een verwijzing naar de IEEE 1164-standaardbibliotheek en definieert vervolgens een interface naar de MicroBlaze-processor die de signalen blootlegt die u op een microprocessor zou verwachten, inclusief de systeemklok, reset, interruptverzoek en interruptvectoringangen; onderbrekingsbevestiging en instructie-adresuitgangen; en een bus voor de instructies die uit het geheugen worden opgehaald.

Deze code maakt gebruik van de IEEE 1164-bibliotheekgegevenstypen voor single-bit signalen (STD_LOGIC) en voor multi-bit bussignalen (STD_LOGIC_VECTOR).

De code in de lijst definieert de interface naar de MicroBlaze-processor, maar bevat niet de HDL-definitie van de processor zelf. Complexe HDL-ontwerpen voor componenten zoals microprocessors worden als waardevol beschouwd Intellectueel eigendom (IP ) en de commerciële entiteiten die deze ontwerpen ontwikkelen, ondernemen vaak stappen om ervoor te zorgen dat ze niet worden gebruikt zonder de juiste licentie. Wanneer leveranciers IP distribueren voor gebruik door hun klanten, kan het worden geleverd in een gecompileerde indeling die ondoorzichtig is voor eindgebruikers. Hierdoor kunnen gebruikers het IP-adres in hun ontwerpen opnemen, maar ze kunnen de HDL die is gebruikt om het te ontwikkelen niet onderzoeken. Dit is conceptueel vergelijkbaar met softwareontwikkelaars die een bibliotheek in gecompileerde vorm vrijgeven maar niet de broncode verstrekken.

C/C++

Een aantal leveranciers biedt softwaretools die traditionele programmeertalen op hoog niveau, vaak C en C++, vertalen naar HDL-code voor gebruik bij FPGA-ontwikkeling. Deze aanpak kan aantrekkelijk zijn als je een complex algoritme in C of C++ hebt dat je wilt versnellen in een FPGA-implementatie. Met deze tools kunnen softwareontwikkelaars die bekend zijn met C/C++ onmiddellijk beginnen met het implementeren van code voor FPGA-gebruik zonder dat ze een van de HDL's hoeven te leren.

Hoewel FPGA-ontwikkeltools voor deze talen op hoog niveau in staat zijn tot aanzienlijke optimalisatie van de resulterende FPGA-implementatie van het C/C++-codealgoritme, is er nog steeds iets van een ontkoppeling in die zin dat het C/C++-uitvoeringsmodel de sequentiële uitvoering van instructies omvat, terwijl de native FPGA-omgeving bestaat uit parallelle hardwarecomponenten. Het FPGA-ontwerp dat voortkomt uit C/C++-code lijkt typisch op een verzameling statusmachines die de sequentiële uitvoering van de bewerkingen beheren die zijn gedefinieerd in de programmeertaalinstructies. Afhankelijk van de beschikbaarheid van mogelijkheden voor parallelle uitvoering binnen de C/C++-code, kan een FPGA-implementatie een aanzienlijke prestatieverbetering bieden in vergelijking met het uitvoeren van dezelfde code op een traditionele processor.

In moderne FPGA-ontwikkeltoolsuites kunnen alle methoden van FPGA-implementatie die in deze sectie worden beschreven (VHDL, Verilog, blokdiagrammen en C/C++) indien nodig in één ontwerp worden gecombineerd. Hierdoor kan het ene teamlid liever in VHDL werken, terwijl een ander Verilog gebruikt. Er kunnen projectmanagementredenen zijn om multi-HDL-gebruik binnen één project te ontmoedigen, maar de talen zelf functioneren probleemloos samen in één ontwerp. Een van de redenen waarom een projectmanager het gebruik van meerdere HDL's zou willen vermijden, is dat de toekomstige ondersteuning van de inspanning de deelname vereist van ontwikkelaars met vaardigheden in beide talen.

Evenzo is het mogelijk om een architectuur op hoog niveau voor een project te definiëren in termen van een blokschema en vervolgens gedetailleerde subsysteemfunctionaliteit te implementeren met behulp van de HDL naar keuze. In hetzelfde ontwerp is het ook mogelijk om HDL te integreren dat is gegenereerd op basis van een C/C++-algoritme. Ingebedde systeemarchitecten en ontwikkelaars moeten de implicaties zorgvuldig overwegen en de juiste implementatiemethode selecteren voor elk deel van een FPGA-ontwerp.

In het volgende gedeelte worden de stappen in het standaard FPGA-ontwikkelingsproces geïntroduceerd.

Herdrukt met toestemming van Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin is de CEO van Ledin Engineering, Inc. Jim is een expert in het ontwerpen, ontwikkelen en testen van embedded software en hardware. Hij is ook bekwaam in het beoordelen van cyberbeveiliging van embedded systemen en het testen van penetratie. Hij heeft een B.S. graad in lucht- en ruimtevaarttechniek van Iowa State University en een M.S. graad in elektrotechniek en computertechniek aan het Georgia Institute of Technology. Jim is een geregistreerde professionele elektrotechnisch ingenieur in Californië, een Certified Information System Security Professional (CISSP), een Certified Ethical Hacker (CEH) en een Certified Penetration Tester (CPT).

Jim Ledin is de CEO van Ledin Engineering, Inc. Jim is een expert in het ontwerpen, ontwikkelen en testen van embedded software en hardware. Hij is ook bekwaam in het beoordelen van cyberbeveiliging van embedded systemen en het testen van penetratie. Hij heeft een B.S. graad in lucht- en ruimtevaarttechniek van Iowa State University en een M.S. graad in elektrotechniek en computertechniek aan het Georgia Institute of Technology. Jim is een geregistreerde professionele elektrotechnisch ingenieur in Californië, een Certified Information System Security Professional (CISSP), een Certified Ethical Hacker (CEH) en een Certified Penetration Tester (CPT). Verwante inhoud:

- Ingesloten ontwerp met FPGA's:hardwarebronnen

- Open-source tools helpen FPGA-programmering te vereenvoudigen

- Implementatie van drijvende-kommaalgoritmen in FPGA's of ASIC's

- Softwaretools migreren GPU-code naar FPGA's voor AI-toepassingen

- FPGA's verdringen ASIC's in op Subaru Eyesight gebaseerde ADAS

- Hoe op flash gebaseerde FPGA's functionele veiligheidsvereisten vereenvoudigen

- De voordelen plukken van instant-on FPGA's

- FPGA-configuratie met snelle NOR-flitser

- Hoe FPGA-technologie evolueert om te voldoen aan nieuwe systeemvereisten voor het middensegment

Abonneer u voor meer Embedded op de wekelijkse e-mailnieuwsbrief van Embedded.

Ingebed

- Wat is embedded systeemprogrammering en de bijbehorende talen

- Wat is ingebed systeemontwerp:stappen in het ontwerpproces

- Big data omzetten in slimme data met ingebouwde AI

- Uitdagingen voor implementatie van USB Type-C-poorten en ontwerpoplossingen

- Belangrijke trends in de branche geven vorm aan embedded design

- FPGA-versneller voor embedded vision MIPI-camera's

- Open-source platform richt zich op IoT met embedded Linux

- Clientron:multifunctionele POS-terminal met geïntegreerde printer

- Ontwerpkit meet bloeddruk met optische sensor

- Defensie-grade FPGA debuteert met vroege toegang

- All-in met additief